JANUARY 2018 VOL. 25, NO. 1 ISSN: 1074 1879

EDITOR-IN-CHIEF: CARMEN M. LILLEY

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                         |     |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| TECHNICAL BRIEFS  • Technical Review of the 63rd IEDM Conference                                                                                                                                                                                                                                                          | . 1 |

| UPCOMING TECHNICAL MEETINGS                                                                                                                                                                                                                                                                                               | . 7 |

| SOCIETY NEWS  EDS Board of Governors Forum Meetings Highlights  Message from EDS President  IEEE EDS Celebrated Members Recognized in 2017  Message from Newsletter Editor-in-Chief                                                                                                                                       | . 9 |

| EDS Members Recently Elected to IEEE Senior Member Grade      Awards and Call for Nominations                                                                                                                                                                                                                             | 15  |

| Fellowship Recipients  EDS PhD Student Fellowship Program  Updates from the 2017 EDS Masters Student Fellowship Recipients  EDS Masters Student Fellowship Program                                                                                                                                                        |     |

| YOUNG PROFESSIONALS  • Young Entrepreneur Attracts Record Number of Attendees at Annual IEDM Event  • GaN Transistors – Giving New Life to Moore's Law  • First NanoBootcamp Young Professionals Colombia Micro & Nano day "Reloaded"  • Educate Children on the Use of Integrated Circuit (IC) Chips on a Beginner Level | 20  |

| CHAPTER NEWS  2017 EDS Chapter of the Year Award Winners  IEEE Africa Initiative, 2016–2017: Courses delivered by EDS Distinguished Lecturers  2018 EDS Chapter of the Year Award—Call for Nominations  EDS-ETC Program for Students of SM Kepala Batas, Penang                                                           | 26  |

| Mini-Colloquia and Conference Reports  IEEE EDS Vancouver Mini-Colloquium at Simon Fraser University  ED Brazil Mini-Colloquium and Report of SBMicro 2017  Report on the 11th IEEE Regional Symposium on Micro & Nanoelectronics                                                                                         | 30  |

| REGIONAL NEWS                                                                                                                                                                                                                                                                                                             | 34  |

| EDS MEETINGS CALENDAR                                                                                                                                                                                                                                                                                                     | 44  |

| INAUGURAL CEREMONY OF IEEE 'EDS CENTER OF EXCELLENCE'                                                                                                                                                                                                                                                                     | 47  |

| EDS VISION, MISSION AND FIELD OF INTEREST STATEMENTS                                                                                                                                                                                                                                                                      | 48  |

# **IEEE**

## TECHNICAL BRIEFS

# TECHNICAL REVIEW OF THE 63RD IEDM CONFERENCE

BY BARBARA DE SALVO AND SUMAN BANERJEE

The IEEE 63rd IEDM conference (www.ieee-iedm.org) was held December 2–6, 2017 at the Hilton San Francisco Union Square Hotel. Highlights of the conference include the technology platform presentations by Intel and Globalfoundries detailing their competing new 10 nm/7 nm FinFET technology platforms. In addition, AMD President & CEO Lisa Su spoke on multi-chip technologies for high-performance computing. There was also the plenary talk by Nobel Laureate Dr. Hiroshi Amano during Wednesday morning plenary on "Development of Sustainable Smart Society based on Transformative Electronics."

Of high interest at the conference was the competing technology platform presentations by Intel and Globalfoundries on FinFETS. FinFETs are high-performance transistors for ultra-dense, powerful integrated circuits (ICs). They have a multi-sided gate surrounding a fin-shaped channel for precise transistor control even at the nanoscale. The most advanced FinFETs in volume production are at the 14 nm/16 nm technology node. FinFETs are a major driver of the continued progress of the electronics industry, and at the IEDM, Intel and Globalfoundries unveiled their forthcoming state-of-theart integrated FinFET technology platforms.

Intel researchers presented a 10 nm logic technology platform with excellent transistor and interconnect performance and aggressive design-rule scaling. They demonstrated its versatility by building a 204 Mb SRAM having three different types of memory cells: a high-density 0.0312  $\mu m^2$  cell, a low voltage 0.0367  $\mu m^2$  cell, and a high-performance 0.0441  $\mu m^2$  cell. The platform features 3rd-generation FinFETs fabricated with self-aligned quadruple patterning (SAQP) for critical layers, leading to a 7 nm fin width at a 34 nm pitch, and a 46 nm fin height; a 5th-generation high-k metal gate;

(continued on page 3)

### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at clilley@uic.edu

## ELECTRON DEVICES SOCIETY

#### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### **President-Elect**

Fernando Guarin GlobalFoundries E-mail: fernando.quarin@ieee.org

#### Treasurer

Subramanian S. Iyer UCLA

E-mail: iyer@ieee.org

#### Secretary

Simon Deleonibus CEA-LETI

E-mail: simon.deleonibus.1992@

ieee.org

#### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Sr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

## Vice President of Membership and Services

Tian-Ling Ren Tsinghua University

E-mail: rentl@mail.tsinghua.edu.cn

## Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: h.s.momose@ieee.org

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

## Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith

IEEE Operations Center

E-mail: tlsmith@ieee.org

### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

#### **Membership Administrator**

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (B0G) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2018                                                                                                | TERM                                                 | 2019                                                                                     | TERM                            | 2020                                                                                                 | TERM                                                 |

|-----------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|---------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| N. Bhat<br>D. Camacho Montejo<br>S. Deleonibus<br>M. leong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) | J. Burghartz<br>R. Huang<br>S. Ikeda<br>M. Meyyappan<br>A. Nathan<br>J. Swart<br>B. Zhao | (2)<br>(1)<br>(1)<br>(1)<br>(2) | R. Booth<br>M. Farooq<br>E. Gutierrez<br>B. Iniguez<br>C. Lilley<br>D. Misra<br>M. Saxena<br>S. Sood | (1)<br>(2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(1) |

## NEWSLETTER EDITORIAL STAFF

#### Editor-In-Chief

Carmen M. Lilley University of Illinois at Chicago E-mail: clilley@uic.edu

### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

## Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

## Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery

Air Force Research Laboratory

E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

## REGION 8

## Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

## Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### **UK, Middle East & Africa**

Jonathan Terry

The University of Edinburgh

E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

## REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia

E-mail: susi@ukm.edu.my

#### **Northeast Asia**

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editorin Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

### Newsletter Deadlines

| ISSUE   | DUE DATE    |

|---------|-------------|

| April   | January 1st |

| July    | April 1st   |

| October | July 1st    |

| January | October 1st |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2018 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

## TECHNICAL REVIEW OF THE 63RD IEDM CONFERENCE

(continued from page 1)

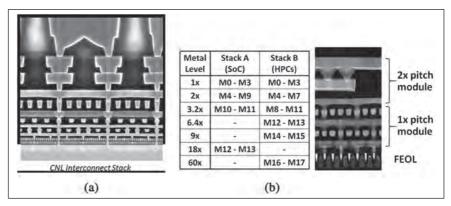

and 7th-generation strained silicon. There are 12 metal layers of interconnect, see Figure 1(a), with cobalt wires in the lowest two layers that yield a 5-10x improvement in electromigration and a 2x reduction in via resistance. NMOS and PMOS current is 71% and 35% greater, respectively, compared to 14 nm FinFET transistors. Metal stacks with four or six workfunctions enable operation at different threshold voltages, and novel self-aligned gate contacts over active gates are employed.

Globalfoundries researchers presented a fully integrated 7 nm CMOS platform that provides significant density scaling and performance improvements over 14 nm. It features a 3rd-generation FinFET architecture with SAQP used for fin formation, and self-aligned double patterning for metallization. The 7 nm platform features an improvement of 2.8x in routed logic density, along with impressive performance/power responses versus 14 nm: a >40% performance increase at a fixed power, or alternatively a power reduction of >55% at a fixed frequency. The researchers demonstrated the platform by using it to build an incredibly small 0.0269 µm<sup>2</sup> SRAM cell. Multiple Cu/low-k BEOL stacks, see Figure 1(b), are possible for a range of system-on-chip (SoC) applications, and a unique multiworkfunction process makes possible a range of threshold voltages for diverse applications. A complete set of foundation and complex IP (intellectual property) is available in this advanced CMOS platform for both high-performance computing and mobile applications.

In addition, the 2017 IEDM featured four Focus Sessions with invited papers from world experts describing the latest research in some of the fastest-growing and futuristic areas of electronics technology. The first

Fig. 1. (a) Micrograph of Intel platform's 12-layer interconnect stack [1]. (b) Micrograph of two BEOL stacks, with the cross-section focused on the 1X and 2X levels from GlobalFoundries [2]

focus session was on "3D Integration and Packaging" and featured talks on topics including low-temperature processing, materials, resistance, bandwidth and cost challenges. It also gave an industry perspective on future packaging technologies. As scaling below 7 nm approaches, 3D integration and advanced packaging are key enabling technologies for a host of applications including sensor interfaces, IoT systems, neuromorphic computing, CCD image sensors and onchip power supplies with integrated magnetics. The session included "3D Sequential Integration: Application-Driven Technological Achievements and Guidelines," by Perrine Batude et al, CEA Leti, "Pixel/DRAM/Logic 3-layer Stacked CMOS Image Sensor Technology," by Hidenobu Tsugawa et al, Sony Semiconductor Solutions Corp., "Power Inside - Applications and Technologies for Integrated Power in Microelectronics," Cian O'Mathuna, University of Cork, "3D System Package Architecture as Alternative to 3D Stacking of ICs with TSV at System Level," by Rao Tummala, Georgia Institute of Technology, "Advanced Packaging Saves the Day! - How TSV Technology Will Enable Continued Scaling," by Luke England et al, Globalfoundries, "Advanced Packaging with

Greater Simplicity," by Douglas Yu, TSMC, and "Towards Cube-Sized Compute Nodes: Advanced Packaging Concepts Enabling Extreme 3D Integration," by Thomas Brunschwiler et al, IBM Research, Zurich.

The second focus session was on "Nanosensors for Disease Diagnostics." Today's health-related problems are increasingly complex, multidisciplinary in nature, often illdefined, and require solutions that cannot be addressed by the medical community on its own. This session reviewed the latest advances in bio-sensing technologies, including the potential of miniaturization in microfluidics to achieve a human organ on a chip; disease models for a "prostate on a chip"; nanoparticleenabled microscale technologies for the capture of rare circulating tumor cells; a rapid antibiotic susceptibility test system; imaging techniques for in-vivo tissue engineering to track drug penetration; a high-throughput detection system for single bacteria and mammalian cell sizing; and bulk acoustic wave resonators with unique high resonant frequencies >1 GHz to provide a platform for versatile bioactuators. Talks in this session included "Nanofluidics for Cell and Drug delivery," by Mauro Ferrari et al, Houston Methodist Research Institute, "Rapid Antibiotic Susceptibility Testing System: Life Saving BioMEMS devices," by Sunghoon Kwon et al, Quantamatrix and Celemics, "Development of High Frequency Bulk Acoustic Wave Resonators as Biosensors and Bioactuators," by Xuexin Duan et al, Tianjin University, "Encapsulated Organoids and Organ-on-a-Chip for Cancer Modeling," by Nathalie Picollet D'hahan et al, CEA, "A Single Bacterium and Mammalian Cell Analysis by Ionic Current Measurements in a Microchannel," by Noritada Kaji et al, Nagoya University, "Tissue Microenvironment and Cellular Imaging," by Karen Cheung et al, University of British Columbia, and "Microscale Profiling of Circulating Tumor Cells" Reza Mohamadi et al, University of Toronto.

The third focus session was on "Modeling Challenges for Neuromorphic Computing." ReRAM is a promising synaptic device that is naturally aligned to brain-inspired cognitive computing applications versus software-based systems implemented in CMOS circuitry that consume higher energy at lower densities. This session had presentations on a comprehensive mix of topics covering critical devices, circuits and applications which included "Stochastic Synapses as Resources for Efficient Deep-Learning Machines," by Emre Neftci, University of California at Irvine, "Attractor Networks and Associative Memories with STDP Learning in RRAM Synapses," by Elisabetta Chicca et al, University of Bielefeld, "Energy Use Constrains Brain Information Processing," by Renaud Jolivet et al, CERN, Switzerland, "Understanding the Trade-Offs of Device, Circuit and Applications in RRAM-Based Neuromorphic Computing Systems," by Hai Li et al, Duke University, "Device and Circuit Optimization of RRAM for Neuromorphic Computing," by Huagiang Wu et al, Tsinghua University, "Challenges and Opportunities Toward Online Training Acceleration Using RRAM-Based Hardware Neural Network," by Tuohung Hou et al, National Chiao Tung University, and "Multiscale Modeling of Neuromorphic Computing Devices: From Materials to Device Operations," by Luca Larcher et al, Universita di Modena e Reggio-Emilia.

The fourth focus session was on "Silicon Photonics: Current Status and Perspectives." Silicon photonics integrated circuits consist of devices such as optical transceivers, modulators, phase shifters and couplers, operating at >50 GHz for use in nextgeneration data centers. This session describes the latest in photonics IC advances in state-of-the-art 300 mm fabrication technology; integrated nano-photonic crystals with fJ/bit optical links; and advanced packaging concepts for the specialized form factors this technology requires. The talks included "Developments in 300 mm Silicon Photonics Using Traditional CMOS Fabrication Methods and Materials," by Charles Baudot et al, STMicroelectronics, "Reliable 50 Gb/s Silicon Photonics Platform for Next-Generation Data Center Optical Interconnects," by Philippe Absil et al, Imec, "Advanced Silicon Photonics Technology Platform Leveraging the Semiconductor Supply Chain," by Peter De Dobbelaere, Luxtera, "Femtojoule-per-Bit Integrated Nanophotonics and Challenge for Optical Computation," by Masaya Notomi et al, NTT Corporation, and "Advanced Devices and Packaging of Si-Photonics-Based Optical Transceiver for Optical Interconnection," by K. Kurata et al, Photonics Electronics Technology Research Association.

There were several other noteworthy talks including a presentation on Lab on Skin™ titled "Lab On Skin™: 3D Monolithically Integrated Zero-Energy Micro/Nanofluidics and FD SOI Ion-Sensitive FETs for Wearable Multi-Sensing Sweat Applications," by F. Bellando et al at EPFL/Xsensio. Hundreds of biomarkers can be tracked in human sweat, and wearable sweat sensors may play a key role in precision healthcare and life-

style applications. A team led by EPFL reported a novel fully integrated, lowpower, multi-sensing smart system that can passively collect sweat and measure its biomarker content in real-time. Called Lab on Skin™, it uses arrays of functionalized sensors to simultaneously detect pH, Na+ and K+ concentrations in sweat. Built using wafer-level techniques, it features the 3D heterogeneous integration of ionsensitive, fully depleted SOI (FD SOI) FETs and micro/nanofluidic sensing channels created with the commonly used SU-8 negative photo resist. Unlike previous sweat sensors, which required large amounts of sweat, the new system exploits capillary forces to provide zero-energy pumping of tiny amounts into the channels for analysis. The system demonstrated excellent sensitivities (52mV/dec for pH and -37 mV/dec for Na+ sensors) and ultra-low power consumption (<50 nWatts/sensor). It features the integration of miniaturized Ag/AgCl quasi-reference electrodes, paving the way for use in fully wearable flexible patches or as plug-in modules in wrist-based devices.

Additionally, there was a presentation on high-performance devices on paper by S. Park and D. Akinwande at the Univ. Texas-Austin titled "First Demonstration of High Performance 2D Monolayer Transistors on Paper Substrates." Paper is a thin, inexpensive and ubiquitous material, making it attractive as a possible substrate for flexible electronic devices for use in nanoelectronic systems, sensors and Internet of Things (IoT) applications. Two-dimensional (2D), or monolayer, semiconductors like graphene and molybdenum disulfide (MoS<sub>2</sub>) are attractive potential matches for paper substrates because they are thin and also strong enough to bend without damage, up to a point. Univ. Texas-Austin researchers discussed at the IEDM how they built a variety of highperformance two- and three-terminal graphene and MoS, devices on paper for the first time ever. They first coated the paper with polyimide to make

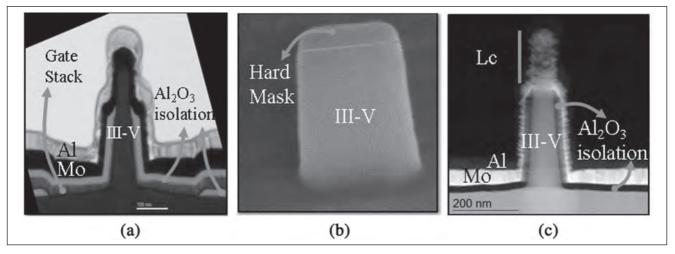

Fig. 2. (a) Electron microscope micrograph with view across the width of a 37 x 480 nm single nanosheet FET device. (b) Electron microscope micrograph of a single vertical nanosheet after dry etch. (c) Electron microscope micrograph of a vertical nanowire resistor after transmission line measurement (TLM) fabrication. [3]

it extremely smooth, and to prepare it for the wet transfer of the high-quality large-area-synthesized 2D films. The graphene or MoS, devices were fabricated via CVD. A record 25 GHz cutoff frequency for a graphene device on a paper substrate was demonstrated, and device performance remained high even when the paper was rolled into a 2" diameter roll. Further, it was stable even when the paper was cycled >1,000 times to a bending strain of 0.6%.

A team led by Nanjing University reported on the first steep subthreshold-slope MoS, devices ever demonstrated. The paper titled "Negative Capacitance 2D MoS2 Transistors with Sub-60mV/dec Subthreshold Swing over 6 Orders, 250 μA/μm Current Density, and Nearly Hysteresis-Free," by Z. Yu et al, Nanjing Univ./Fudan Univ./Hong Kong Polytechnic Univ. They fabricated a negative capacitance FET structure using ferroelectric HfZrO (HZO)/AIO as the gate stack. The devices exhibited an ultra-low subthreshold swing of 23mV/dec (with sub-60mV/dec for over six orders of magnitude). There was negligible hysteresis, a small threshold voltage loss (<0.4 V) and a high  $I_{on}/I_{off}$  ratio (>10°). This all makes the negative-capacitance

MoS, FET a potential candidate for future ultralow-power applications (sub-0.5 V operation). There was also a presentation on the record performance from vertical III-V nanowire/ nanosheet MOSFETs titled "Computational Study of Gate-Induced Drain Leakage in 2D-Semiconductor Field-Effect Transistors," by J. Kang et al, Univ. California-Santa Barbara/ Micron Technology. High-mobility materials such as III-V compound semiconductors may be well-suited for transistor channels in future lowpower logic applications. A vertical architecture is attractive for III-V devices because they normally suffer from higher off-currents than silicon given their narrower bandgaps, and so the ability to relax the gate-length scaling requirement - as can be done in a vertical configuration - is beneficial. A team from KU Leuven and Imec built InGaAs vertical nanowire and vertical nanosheet MOSFETs using a top-down VLSI-compatible fabrication technique. These experimental devices, shown in Figure 2, demonstrated the best performance ever reported for vertical III-V devices –  $I_{nn}$  = 397  $\mu$ A/ $\mu$ m and peak transconductance (Gm) = 1.6 S/µm at Vds = 0.5 V - along with impressivesubthreshold slope performance

(SS = 63 mV/decade). The performance was driven by excellent electrostatic control, an improved process integration scheme versus earlier work, a low-damage dry etch process and optimized surface treatment. The fabrication process did not compromise reliability compared to similar gate stacks, and the researchers say that reducing access resistance and especially contact resistance to the source/drain regions would further improve performance.

In addition the excellent sessions at this year's conference, there were also 90-Minute Tutorials on emerging technologies presented by leading technical experts in each area, with the goal of bridging the gap between textbook-level knowledge and cutting-edge current research. There were day-long Short Courses to provide the opportunity to learn about important developments in key areas, and they enable attendees to network with the industry's leading technologists.

Finally, the plenary sessions included the following presentations: "Driving the Future of High-Performance Computing," by Lisa Su, President & CEO, AMD, "Energy-Efficient Computing and Sensing: From Silicon to the Cloud, Adrian Ionescu, Professor,

EPFL, "System Scaling Innovation for Intelligent Ubiquitous Computing, Jack Sun, VP of R&D, TSMC, and "Development of a Sustainable Smart Society by Transformative Electronics, Hiroshi Amano, Professor, Nagoya University. Dr. Amano received the 2014 Nobel Prize in Physics along with Isamu Akasaki and Shuji Nakamura for the invention of efficient blue LEDs, which sparked a revolution in innovative, energy-saving lighting.

In addition, jointly sponsored by IEDM and IEEE EDS Women in Engineering, this year's Entrepreneurs Lunch featured Courtney Gras, Executive Director for Launch League, a local nonprofit focused on developing a strong startup ecosystem in Ohio. The moderator was Prof.

Leda Lunardi from North Carolina State University, Gras is an engineer by training and an entrepreneur by nature. After leaving her job as a NASA power systems engineer to work on her own startup company, she discovered a passion for building startup communities and helping technology-focused companies meet their goals. Named to the Forbes "30 Under 30" list in 2016, among many other recognitions and awards, Gras enjoys sharing her stories of founding a cleantech company with young entrepreneurs. She speaks on entrepreneurship, women in technology and clean energy at venues such as TEDx Budapest, the Pioneers Festival, and the IEEE WIE International Women's Leadership Conference.

#### References

- [1] C. Auth et al, Intel, "A 10 nm High Performance and Low-Power CMOS Technology Featuring 3rd-Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact Over Active Gate and Cobalt Local Interconnects," 2017 IFDM

- [2] S. Narasimha et al, Globalfoundries, "A 7 nm CMOS Technology Platform for Mobile and High-Performance Compute Applications," 2017 IEDM.

- [3] S. Ramesh et al, KU Leuven/ Imec, "Record PerformanceTop-down In0.53Ga0.47As Vertical Nanowire FETs and Vertical Nanosheets," 2017 IEDM

Edited by Carmen M. Lilley

# Present a world of opportunity

- Professional Growth

- Collaboration

- Global Network

## When you give the gift of an IEEE Membership,

you're helping someone you care about build a platform for success. That's because IEEE delivers access to the industry's most essential technical information, provides both local and global networking opportunities, offers career development tools, plus discounts on conference registrations and insurance programs, as well as many other exclusive member benefits.

Get started today at www.ieee.org/gift

## UPCOMING TECHNICAL MEETINGS

## 2018 IEEE International Reliability Physics Symposium (IRPS)

The International Reliability Physics Symposium (IRPS) is the world's premier forum for leading-edge research addressing developments in the Reliability Physics of devices, materials, circuits, and products used in the electronics industry. IRPS is the conference where emerging reliability physics challenges and possible solutions to achieve realistic End-of-Life projections are first discussed. This year, the IRPS will be held at Hyatt Regency San Francisco Airport, Burlingame, CA. Scheduled for March 11-15, 2018, the IRPS will commence with two full days of tutorials and year-in-review on Sunday, March 11th and Monday, March 12th. This will be followed by three days (Tues-Thurs, March 13–15) of plenary and parallel technical sessions presenting original, state-of-the-art work.

The IRPS draws presentations and attendees from industry, academia and governmental agencies worldwide. No other meeting presents as much leading work in so many different areas of reliability of electronic devices, encompassing silicon device, non-silicon device, process technology, nanotechnology, optoelectronics, photovoltaic, MEMS technology, circuits and systems reliability including packaging.

IRPS 2018 is soliciting increased participation in the following areas: reliability of wide bandgap semiconductor power devices, circuit aging, consumer electronics, reliability of 2D NAND flash replacement technologies, 2.5D & 3D packaging. We are also emphasizing self-heating effects on transistors and circuit aging and systems reliability comprehending complex applications including chip-package interactions and packaging. In addition, we are strongly promoting all reliability work on photovoltaics. Furthermore, three focus sessions composed of worldwide recognized reliability experts will be organized on the following topics: 1) wide bandgap semiconductors: reliability issues and standardization status; 2) 2.5D/3D packaging reliability; 3) System level reliability.

The conference hotel is conveniently located near the San Francisco Airport, situated between downtown San Francisco and near many Silicon Valley industries. It is the perfect starting point to explore the many things to do in the Bay Area, including the Golden Gate Bridge, Cable Cars, Alcatraz Island, Lombard Street, shopping in Union Square, dining at Fisherman's Wharf, and many museums, theaters and clubs.

For 56 years, IRPS has been the premiere conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and all other parts of the world, IRPS seeks to understand the reliability of semiconductor devices, integrated circuits, and microelectronic assemblies through an improved understanding of both the physics of failure as well as the application environment. IRPS 2018 will offer a full slate of tutorials, evening panel debates and workshops, invited plenary talks in addition to an outstanding technical program.

Other opportunities at the symposium include:

Two-Day Tutorial Program (Sunday-Monday March 11-12). The IRPS tutorial program is a comprehensive two-day event designed to help both the new engineer and experienced researcher. The

tutorial program contains both beginner and expert tracks, and is broken down into topic areas that allow the attendee to participate in tutorials relevant to their work with a minimum of conflicts between subject areas.

- Year in Review Session (Monday March 12). These seminars provide a summary of the most significant developments in the reliability community over the past year. This serves as a convenient, single source of information for attendees to keep current with the recent reliability literature. Industry experts serve as the "tour guide" and save you time by collecting and summarizing this information to bring you up to date in a particular area as efficiently as possible.

- Evening Poster Session. The poster session will provide an additional opportunity for authors to present their original research. The setting is informal and allows for easy discussion between authors and other attendees.

- Evening Session Workshops. These workshops enhance the symposium by providing the attendees an opportunity to meet in informal groups to discuss key reliability physics topics with the guidance of experienced moderators. Some of the workshop topics are directly coupled to the technical program to provide a venue for more discussion on the topic.

- **Vendor Exhibits**. Held in parallel with the technical sessions, the equipment demonstrations provide a forum for manufacturers of state-of-the-art laboratory equipment to present their products. Attendees are encouraged to visit

- the manufacturers' booths for information and demonstrations.

- IRPS Paper Awards. IRPS bestows awards for Best Paper, Outstanding Paper, Best Poster and Best Student Paper. The Best Paper author is typically invited

to present the paper at ESREF in October.

For registration and other information, visit the IRPS-2018 home page at http://www.irps.org/ .

The IRPS committee members look forward to seeing you in March.

Elyse Rosenbaum 2018 IRPS General Chair University of Illinois

Cathryn Christiansen 2018 IRPS Publicity Chair GlobalFoundries

## 2018 IEEE INTERNATIONAL MEMORY WORKSHOP (IMW)

The 10th International Memory Workshop (IMW) will be held at the Westin Miyako Hotel in Kyoto, Japan from May 13-16, 2018. The history of the IMW dates back to the NVSMW (Nonvolatile Semiconductor Memory Workshop) which began in 1976 and which later merged with the ICMTD (International Conference on Memory Technology and Design) to become the IMW. The IMW is sponsored by the IEEE Electron Devices Society and meets annually in May. The workshop covers all types of memory technology, is focused on advancing innovation in memory technology, and is organized in a way that provides excellent professional development and networking opportunities for attendees.

The IMW is the premier international forum for both new and seasoned technologists having diverse technical backgrounds to share and learn about the latest developments in memory technology with the global community. The scope of workshop content ranges from new memory concepts in early research to the technology drivers currently in volume production as well as emerging technologies in development. Topics include new device concepts, technology advancements, scaling and integration, circuit design and reliability, as well as emerging applications. Consistent with the increased importance of

memory system architecture and integration, the workshop also includes increasing coverage of the systems in which memories are deployed and the co-evolution of memory technology along with memory systems and applications.

The IMW is the preeminent forum covering the latest developments, innovations, and evolving trends in the memory industry. Typical workshop attendance exceeds 250 attendees and the technical program begins with a full day short course given by distinguished experts that provides an excellent professional development opportunity for both new and experienced technologists. The single-track technical program spans three days and also includes an evening poster session for informal technical discussion with authors as well as a panel discussion where experts discuss and debate a current hot topic. The 2017 workshop included invited talks from industry and research leaders from Google, Samsung, Micron, IBM, Western Digital, Panasonic, Everspin, CEA LETI, and IMEC. Highlights included experts sharing their insights and perspectives on a variety of topics including the 3D NAND scaling horizon and potential successors, the latest breakthroughs in RRAM/MRAM/FRAM technology, low latency persistent memory architecture, the prospects

of emerging NVM to accelerate deep learning, and the transformative impact that machine intelligence in consumer products is having on memory architecture. The technical program is organized to maximize networking opportunities and facilitate open information exchange among workshop contributors, committee members, and attendees. The program schedule includes ample time dedicated to social events including provided refreshment breaks, a workshop luncheon, and an evening banquet. This year's workshop is located near downtown Kyoto, with opportunities to explore the local temples, shrines, palaces, gardens, and museums that are part of the area's rich cultural heritage.

On behalf of the organizing committee, I cordially invite you to attend the 2018 IMW to participate in the advancement of innovation in the rapidly evolving memory industry. For additional information, including the call for papers, key dates, abstract submission instructions, registration information, and technical program details, please visit the IMW website for the latest updates: http://www.ewh.ieee.org/soc/eds/imw/. I look forward to seeing you in Kyoto this May.

Randy Koval 2018 IMW Publicity Chair Intel

## SOCIETY NEWS

## EDS BOARD OF GOVERNORS/FORUM DECEMBER 2 AND 3, **2017 MEETINGS HIGHLIGHTS**

Simon Deleonibus EDS Secretary

The 2017 end of the year EDS Board of Governors/Forum meetings were held in San Francisco, California on December 2nd and 3rd, 2017, Since 2016, this edition of the annual series is held

in San Francisco in the same premises as IEDM at the Hilton Union Square. The whole Forum is indebted to the EDS Office members for the wonderful organization of the meetings. This year was marked by the celebration of our very prestigious members Gordon Moore and Simon Sze, on Sunday evening and during the opening session of the IEDM on Monday December 4th.

Yearly updates by the publications and newsletter, education, membership, regions & chapters and conferences and technical activities Standing Committees were given on Saturday, December 2nd and reported by the chairs on Sunday, December 3rd at the Forum meeting. December is also time for the awards, nominations and elections, as well as the Fellow committees to report on the past year results. Officers and members-at-large elections took place at the end of the December 3rd Forum meeting, with the presence of voters only. The ExCom held its meeting on Saturday evening. Significant highlights are given hereafter.

A first report was given by the President on the collection of surveys from our Technical Committees & Conferences, Region and Chapters and Publications Committees supporting our 5-year plan. More discussions will be necessary in the coming months before submitting our 5-year plan to IEEE, for its approval in May 2018.

During Saturday's Committees meetings and Sunday's Forum, we had fervent discussions on the future of EDS policies. Our Standing and Technical Committees efforts constantly need to cover all aspects of knowledge dissemination by taking coordinated and coherent approaches. There are important questions that need to be addressed regarding: 1) our publications leadership in EDS core business, the new web based contents and accessibility of our highlights to the general public; 2) strengthening our conferences by continuing the stimulation of EDS excellence policy and enhanced collaborations between our Standing and Technical Committees; 3) our Education, R&C and Membership policies to attract interest of the younger generations (students or professionals) and female population towards the field of electron device engineering, as well as to develop new education tools; 4) the increasing use of mobile access to 100% web based services to our members, including social media; 5) the efficiency and transparency of our governance; 6) outreach and strategic alliances with other societies, particularly in establishing roadmaps.

The BoG and Forum membership reached a quorum at the meeting. The list of 7 approved motions is given at the end of this article. One motion regarding the revision of Bylaws section 10.4 will be voted by email. The main highlights are reported hereafter.

Newsletter: The newly assigned EDS Newsletter Editor in Chief, Carmen Lilley, has taken full service with the July issue. A strategy to enhance the web based version of the Newsletter, while enhancing the paper version at reduced cost was proposed to the Oversight Committee and Forum. Both bodies approved the proposed path: a motion was approved by the Forum and the various Newsletter formats will be accessible by mid-2018. More changes will be brought to the Newsletter organization: the Forum adopted the definition of two new Associate Editor positions openings to enhance the Technical Content and Professional Development sections. The Technical Content Associate Editor will stimulate the publication of tutorial papers- not in competition with our peer review journals - to widely disseminate the society's updated knowledge. This person will drive increased interactions with our Technical Committees to suggest technical articles subjects. A first initiative has been launched following the MQ "Marvels in Microelectronics" held in Stuttgart in September 2017. The Professional Development Associate Editor will interact mostly with Young Professionals, Women in Engineering, Education Committees, IEEE Collabratec and other member services.

Publications: The initiatives to revamp our journal covers by the means of editor's picks has received positive feedbacks despite the fact that changes are susceptible to creating some controversy. In 2017, we observed a substantial increase in the number of submissions to our journals, while maintaining the selection rates steady and good progression of our bibliometric indices (Impact factors EDL: 3.048; TED: 2.605; JEDS: 3.141). The time from submission to e-publication has decreased noticeably down to 3.6 weeks for EDL, 12.7 weeks for TED and remain steady (11.8 weeks) for JEDS. These results are due to all the volunteers and staff efforts to improve our publication service efficiency and outreach. Our bylaws fixing our paper charge strategy (Bylaws section 10.4) need to be updated due to the Society's hybrid policy (volunteer or open access). The page charge influence on our journal's impact factors in the general context of IEEE and the race against competition, without sacrificing our journal's reputations, should not be the only metric to measure their quality. Important aspects such as the type of content and the access to 100% mobile-based publications will be other hot topics in the future. The most efficient way to address plagiarism was questioned through the direct contribution of human intervention: JEDS will dedicate a fulltime editor to address this question. The evolution of the type of content (including modifications in our web versions) is among the hot topics to address for our future differentiation. The place of special issues and their relevance in each of our journals was discussed to avoid any internal competition between EDS journals and foster complementarity: TED focuses on topical issues whereas JEDS will handle conferences special issues.

Conferences and Technical Committees: The interactions between our 14 Technical Committees, Conferences organizations and the Publication and Products Committee are fruitful through the web and conferences calls. The meeting on Saturday gathered several working groups around the technical committees. These discussions effectively came with outputs for topical and special journals issues ideas or plenary talks. On the financial viewpoint most of our conferences are trying to doing well without sacrificing quality. Updates on our flagship conferences (IEDM, PVSC, VLSI Technology and Circuits Symposia), well established (IVEC, and now 100% sponsored ESSDERC) and recently started (EDTM, ICEE) meetings are good indicators of the vitality in this sector. However, EDS

must continue the efforts in avoiding strong overlap and unfruitful competition in the future between newly established conferences.

Regions and Chapters: The number of Chapters has been increasing up to 208. One of our biggest efforts is dedicated to keeping our chapters on the way to sustainability. Reviving chapters and obtaining regular reports is an important task including not only the EDS Office but also the SRC (chairs and cochairs). The chapters' subsidy is linked to their reporting. The formation of student chapters is strongly dependent on proper faculty approval. These measures contribute in encouraging chapters durability. Our MQ program gaining in popularity will certainly request some evaluation method as far as the meeting and speakers are concerned. As a matter of fact, the number of Distinguished Lecturers has increased to 105, reaching the 1% maximum limit of our members. The method to select new DLs has been discussed among the different bodies and will be deployed soon. Their main guideline was unanimously to maintain a high quality among our DLs, either in the nomination/endorsement process and in the operation of our program.

Education: Our EDS-ETC and EDS Institute programs are expanding and gaining in popularity. As an example, in 2016-2017, 9,744 high school students (50% male, 50% female) participated to our EDS-ETC program in all regions. These programs are continuing their expansion. They will be excellent vehicles in the future to extend electron device popularity to all ages and levels of education from junior high school to higher education levels. Our webinars are including more and more topics from the Diversification domain. Other activities and initiatives such as the Student Fellowships, "Discover the Creative Engineer in You", "Young Engineer Drive" are piloted by the Education Committee with good matching of objectives with our Regions & Chapters and Membership Committees. To recognize the great dedication to the success of these missions, the Education Award Committee has designated Mansun Chan as recipient of the 2017 Education Award.

Membership: Our membership growth by 3% in one year has been confirmed to 10,440 members (as of November 2017). Developing strategies to overcome these numbers will be a major challenge for EDS in the next 5 years. Our recruitment methodology certainly needs to be updated even though membership fee subsidy could help in bringing in new members. The question of future EDS members profile has to certainly be addressed, including searching beyond the electronics and electrical engineers. A good connection with our various social/ professional initiatives, such as Young Professionals or Women in Engineering, has to be kept and expanded.

Finally, the Forum and BoG were happy to congratulate the 14 newly elected Fellow members. I wish good luck to the newly elected BoG members and thank the outgoing members for their contributions. As I am terminating my 2 years duty, I wish the best to Jacobus Swart, newly elected EDS Secretary, to whom I leave the floor.

Simon Deleonibus EDS Secretary (2016–2017)

# Motions approved at the December 3, 2017 IEEE EDS BoG meeting in San Francisco.

**Motion**: To approve the minutes of the last meeting

**Motion**: For repeat conferences to approve the 2019 financial conferences and to approve the technical cosponsored conferences for 2019

**Motion**: To approve 100% financial sponsorship for the IEEE International Flexible Electronics Technology Conference starting in 2019

Motion: To approve the 2018 budget Motion: To transfer remaining funds into the IEEE EDS foundation account with a total of \$25K

**Motion**: To approve new format changes to EDS Newsletter

**Motion:** To approve two Newsletter Associate Editors

## Message from EDS President

Samar K. Saha EDS President, 2016-2017

Dear Colleagues and Members of the Electron Devices Society:

First of all, I wish you a Happy and Prosperous New Year, 2018! And, I hope everyone had a wonderful holidav season! I am

writing this message as I prepare to transition to a Past President of the IEEE Electron Devices Society (EDS). Please note that I will continue to be active with EDS promoting excellence in the field of electron devices for the benefit of humanity!

It has been my great pleasure to serve EDS as the President for the past two years (2016-2017). As I shared in my President's report on December 3rd, 2017 Board-of-Governors (BoG) meeting at San Francisco, the EDS has been on a steady roll with the help of Executive Committee (ExCom), BoG, Technical Committee (TC), and Regions & Chapters (RC) volunteers and EDS Executive Office staff in these two years. Following my pledge to building EDS on the foundation of the past to meet the challenges of the future, we made some amazing strides with our ongoing programs and new initiatives for our Society with the great support and outstanding team work of volunteers as well as the staff of the Executive Office! Through the selfless dedication, hard-work, passion, and innovative team work of all, we made some extraordinary accomplishments. I sincerely thank the Ex-Com, BoG,TC, and RC volunteers and Executive Office for their dedicated service for Society's successes. In this message, I will highlight some of the major accomplishments we made together in these past two years:

Membership Growth: Through our membership drive to grow and retain EDS membership, our overall membership grew by

- about 3.6% during 2016-2017 (totaling 10,443). It is worthwhile to mention that during the same two year period, the IEEE membership declined by about 1.1%.

- **Chapter Growth**: The growth of EDS chapters over the past two years modestly reflects the growth of our membership. Considering our primary focus on the growth of student membership and chapters, our worldwide overall chapter growth is about 11.2% in these past two years (totaling 209).

- Publications Excellence: During 2016-2017, we have completed new Editor-In-Chief (EIC) transition for IEEETransactions on Electron Devices (T-ED), IEEE Electron Device Letters (EDL), and EIC search and transition for IEEE Journal of Electron Devices Society (J-EDS) and EDS Newsletter. Through the dedication and relentless pursuit of excellence by new EICs and their editorial boards, our publications continue to excel. The open access (OA) publication, the J-EDS has been the most preferred OA publication for the electron devices community with an impact factor (IF) of 3.14. And, the IF for all our world-class flagship publications, the T-ED and EDL has improved reaching 2.61 and 3.05, respectively. In addition, the EDL submission to online publication is the best in IEEE, averaging about 3.5 weeks. Also, we have published special issues on emerging topical areas including Solid-State Image Sensors, Power Semiconductor Devices and SmartPower ICTechnologies, and Flexible Electronics in T-ED and Ultra-low Power Electronic Devices as well as extended version of selected toprated 2017 EDTM (Electron Devices Technology and Manufacturing) conference papers in J-EDS. Furthermore, we have created a ded-

- icated Special Section with a well-known technical expert in the field as the lead editor to publish the Display Technology research papers in the J-EDS.

- Conference Management: We have successfully executed the launching of the first EDTM conference at Toyama, Japan during February 28th-March 2nd, 2017 to strategically position EDS in the manufacturing stronghold in the Asia-Pacific region. And, the EDTM 2018 is scheduled to be held during March 13-16, 2018 at Kobe, Japan. We have initiated the new IEEE International Flexible Electronics Technology Conference (IFETC) to be held during August 7-9, 2018 at Ottawa, Ontario, Canada with 100% financial sponsorship from 2019 and beyond. The IFETC is, also, aimed to revitalize EDS activities in Region 7. To strategically position EDS in the Europe and Region 8, we have signed an agreement for 100% financial sponsorship of European Solid-State Device research Conference (ESSDERC). Also, to increase the visibility and attendance of our flagship conferences, we have offered options to the newly elected EDS fellows to be recognized at any of our flagship conferences. Accordingly, for the first time, we have recognized EDS Fellows at the opening sessions of 2017 VLSITechnology Symposium at Kyoto, Japan and 2017 Photovoltaic Specialist Conference (PVSC) at Washington, D.C.

- **Educational Program**: In addition to our ongoing stellar educational programs such as Masters and PhD Student Fellowships, Distinguished Lectures (DLs), Mini-Colloquia (MQ), EDS-ETC, Webinar, and so on, we have established an EDS Center of Excellence. This is the 1st of its kind educational program in EDS and IEEE and is aimed to attract future

EDS membership and engage high school and undergraduate boys and girls students in electrical engineering and specifically device engineering, and choose device engineering as their professional career.

- **Outreach Program**: In the past two years, we have established bi-lateral collaboration of mutually beneficial multi-society programs including Heterogeneous Integration Roadmap (HIR), Internet of Things (IoT), International Roadmaps for Devices & systems (IRDS), and IEEE 5G initiatives. In addition to multi-Society technical programs, through our outreach program to IEEE Division I societies, we have, also, added new EDS membership (30 in 2017). In our outreach efforts to students and young professionals, we hosted social events at the 43rd PVSC in Portland, Oregon and 44th PVSC in Washington D.C.

- Future Directions: Besides operating business as usual in these two years of my Presidency, we have initiated the EDS first fiveyear strategic planning to meet the challenges of the future. Though the EDS as an organization is in good standing with the Society's near-future directions and engagements by regularly adopting new strategic initiatives, it is necessary to continuously

change with the changing technology in the digital era: "Change is the law of life. And, those who look only to the past or present are certain to miss the future." -John F. Kennedy. Our first fiveyear strategic plan is based on thorough self-assessment of Society's current position in 2017 by a survey questionnaire to our members, our values, vision, and mission. We will rigorously review the five-year strategic plan and execute accordingly to position EDS in 2022 and beyond.

In these past two years, we recognized and honored the achievements of our members' and honored our most venerated alumni as Celebrated Members: Professor Mildred Dresselhaus in 2016, and Dr. Gordon E. Moore and Professor Simon M. Sze in 2017.

Also, in these past two years, the Society has been in a good financial health. The EDS mission fund for humanitarian activities has grown to about \$102 K. We have updated the EDS Field-of-Interest in compliance to IEEE Technical Activities Board (TAB) word-count requirement and updated the EDS Constitution and Bylaws by resolving the inconsistencies and ambiguities therein by an appointed Ad Hoc committee and got it approved by EDS BoG. Also, Jim Skowrenski was hired as the EDS Operations Director (2016); and

EDS flagship publications have been transferred to IEEE publishing operations to ensure IEEE-wide uniform standard for EDS publications.

These are the major highlights of Society's accomplishments in the past two years in addition to our ongoing day-to-day EDS operations. And, these accomplishments were possible through selfless dedication and outstanding team work of volunteers and the staff of the EDS Executive Office. Once again, I sincerely thank each one of our membership and Executive Office staff for the accomplishments of these past two years. And, special thanks to Simon Deleonibus, Fernando Guarin, Subramanian Iyer, Hisayo Momose, Tian-Ling Ren, MK Radhakrishnan, Ravi Todi, Paul Yu, Albert Wang, James Skowrenski, Laura Riello, Stacy Lehotzky, Joyce Lombardini, and Jessica Lotito for their support in Society's success.

Finally, I congratulate the newly elected BoG members and Officers and, newly appointed ExCom members and Technical Committee Chairs and Members. And, I welcome the new EDS President, Fernando Guarin and wish him all the best to take the Society to a new horizon!

> Samar K. Saha EDS President, 2016-2017 Prospicient Devices, CA, USA samar@ieee.org

## IEEE EDS CELEBRATED MEMBERS RECOGNIZED IN 2017

EDS ANNOUNCED GORDON E. MOORE AND SIMON M. SZE AS EDS CELEBRATED MEMBERS

"For fundamental contributions to the Field of Electron Devices for the benefit of humanity."

Dr. Gordon E. Moore, widely known for Moore's Law, is the founding father of Silicon Valley and a pioneering architect of the history of computing leading to the digital era. He is the co-founder of Fairchild Semiconductor and Intel.

Gordon and his wife Betty established the Gordon and Betty Moore

Foundation in September 2000. The foundation fosters path-breaking scientific discovery, environmental conservation, patient care improvements, and preservation of the special character of the San Francisco Bay Area.

Gordon co-founded Intel in 1968, serving initially as executive vice president. He became president and chief executive officer in 1975 and held that post until elected chairman and chief executive officer in 1979. He remained CEO until 1987 and was named chairman emeritus in 1997, stepping down in 2006.

Gordon is widely known for "Moore's Law," which in 1965 he predicted that the number of components the industry would be able to place on a computer chip would double every year. In 1975, he updated his prediction to once every two years. Because of changing technology, the industry now states approximately every 18 months. "Moore's Law" has become the guiding principle for the industry to deliver ever-more powerful semiconductor chips at proportionate decreases in cost. In practical terms, what this means is faster, cheaper chips with more functionality that allows everything from a laptop computer, cell phones, GPS, cleaner car emissions/skid control/anti-lock brakes, and digital cameras, to medical devices that non-invasively see inside the body, and literally hundreds of thousands of other uses.

Gordon earned a B.S. in chemistry from the University of California at Berkeley and a PhD in chemistry and physics from the California Institute of Technology. He was born in San Francisco, California, on January 3, 1929.

Gordon received the Presidential Medal of Freedom, the nation's highest civilian honor, from George W. Bush in 2002. He received the National Medal of Technology from President George H. W. Bush in 1990. He received the Institute of Electrical and Electronics Engineers (IEEE) Medal of Honor in 2008: "For pioneering technical roles in integratedcircuit processing, and leadership in the development of MOS memory, the microprocessor computer and the semiconductor industry." He is also a member of the National Academy of Engineering and a Fellow of the IEEE. He served as chairman of the board of trustees of the California Institute of Technology from 1995 until the beginning of 2001 and continues now as a LifeTrustee.

Dr. Simon M. Sze was born in Nanking, China in 1936. He received the B. S. degree from the National Taiwan University in 1957, M. S. from the University of Washington in 1960, and PhD from Stanford University in 1963, all in Electrical Engineering.

Simon was with Bell Laboratories in Murray Hill, N. J., from 1963 to 1989 as a member of the Technical Staff, where he was involved in the study of advanced transistors and the development of novel device concepts. He joined the National Chiao Tung University (NCTU) in Hsinchu, Taiwan from 1990 to 2006 as a Distinguished Chair Professor. At present, he is an Honorary Chair Professor at NCTU. Simon has served as Visiting Professor to many academic institutions including the University of Cambridge, Delft University, Soochow University, Stanford University, Swiss Federal Institute of Technology, and Tokyo Institute of Technology.

He has made fundamental and pioneering contributions to semiconductor devices, especially the metal-semiconductor contacts, microwave devices, and MOSFET technology. Of particular importance is his discovery with Dr. Dawon Kahng of the *floating-gate memory* (FGM) effect which has subsequently given rise to a large family of memory devices including EPROM, EEPROM and Flash memory. FGM is a ground-breaking technology for longterm information storage (superseding HDD, optical disk and magnetic tape) and enables the invention of nearly all modern electronic systems such as the digital cellular phone, tablet computer, personal digital assistant, smart IC card, digital camera, digital television, portable DVD, MP3 music player, pacemaker, implantable defibrillator, global positioning system (GPS), and anti-lock braking system (ABS). FGM has also empowered technology for the development of artificial intelligence, big data, cloud computing, internet of things, robotics, and solid-state drive.

Simon has authored or coauthored over 350 technical papers. He has written and edited 16 books. His book "Physics of Semiconductor Devices" (Wiley, 1969; 2nd Ed, 1981; 3rd Ed, with Dr. K. K. Ng, 2007) is one of the most cited works in contemporary engineering and applied science publications (over 47,500 citations according to Google Scholar). Simon has received the IEEE J.J. Ebers Award, the National Endowed Chair Professor Award, the Flash Memory Summit Lifetime Achievement Award, and the National Science and Technology Prize. He is a Life Fellow of IEEE, an ITRI Laureate, an Academician of the Academia Sinica, a foreign member of the Chinese Academy of Engineering, and a member of the US National Academy of Engineering.

## Message from the Editor-in-Chief

Dear EDS Members and Readers,

Carmen M. Lilley Editor-in-Chief EDS Newsletter

It is a pleasure to share with the January newsletter, filled with highlights and summaries of the EDS Board of Governor's meeting held December 2–3 and a technical review

article that summarizes high impact news from 2017 IEEE International Electron Devices Meeting (IEDM) Dec. 2–6. Both events took place concurrently in the exciting city of San Francisco, CA. We also have many articles featuring EDS activities from around the globe. I think you will find this newsletter to be full of informative news from EDS. I want to also express my gratitude to Simon Deleonibus, who is completing his term as EDS Secretary and the Chair of the Newsletter Oversight Committee. I worked alongside Simon, Joyce Lombardini, and James Skowrenski, to collect, organize, and analyze the proposed changes to the EDS newsletter that were approved at the December BoG meeting, highlights that you can find in the Secretary's Letter from Simon in this newsletter. I am grateful for all of their contributions in assisting me with the goal to enhance the newsletter for our readers. As always, I invite our EDS members and readers to share with me their ideas on themes they would like to appear in the newsletter and feedback on changes you see in the newsletter.

Sincerely, Carmen M. Lilley University of Illinois at Chicago Editor-in Chief, EDS Newsletter e-mail: clilley@uic.edu

# EDS MEMBERS RECENTLY ELECTED TO IEEE SENIOR MEMBER GRADE

Gengchiau Liang

Ethem Erkan Aktakka Abdualah Aljankawey Mohammad Amin Arbabian Sergio Bampi Anirban Bandyopadhyay Ismail Hakki Batum Karlheinz Bock Marc Chappo Sang Hun Chung Ryuichi Fujimoto John George Adele Gilliland Guohan Hu Hazem Khanfar Rama Komaragiri Steven Kosier

Felix Levinzon

Gian Domenico Licciardo Chun-Yu Lin Blanka Magyari-Kope Siegfried Mantl Mark Martin **Guy Meynants** Tien Khee Ng Hiroki Noguchi **Guido Notermans** Daniele Passeri Yi Pei Peter Ramm Masa Rao Dilip Risbud Tae Roh Kishore Prabhala

Sneh Saurabh

Jae-Sun Seo

Pankaj Sharma

David Sheridan

Eddy Simoen

P. Sivakumar

Takao Someya

Sergey Tolpygo

Mani Vaidyanathan

Tadaaki Yamauchi

Saul Winderbaum

Hiu Yung Wong

Rajesh Yadav

Yang Yang

Jumril Yunas

If you have been in professional practice for 10 years, you may be eligible for Senior Membership, the highest grade of membership for which an individual can apply. New senior members receive a wood and bronze plaque and a credit certificate for up to US \$25 for a new IEEE society membership. Upon request, a letter can be sent to employers, recognizing this new status. For more

information on senior member status, visit: http://www.ieee.org/membership\_services/membership/senior/index.html

To apply for senior member status, fill out the on-line application after signing in with your IEEE account: https://www.ieee.org/membership\_services/membership/senior/application/index.html.

## Awards and Call For Nominations

## 2016 IEEE TSM BEST PAPER AWARD

High quality scholarship requires technical excellence but also connects the work to the primary references in the field. In this way the reader advances their knowledge and gains perspective. The Transactions on Semiconductor Manufacturing supports these goals by recognizing the best paper chosen by the Associate Editors and reviewers.

The winning paper was selected from 51 papers published by TSM in

2016. The winner is "Risk-Controlled. Product Mix Planning in Semiconductor Manufacturing Using Simulation Optimization" by Dr. Kuo-Hao Chang published in the November 2016 issue of IEEE Transactions on Semiconductor Manufacturing.

Dr. Chang is a professor of Industrial Engineering and Engineering Manufacturing at NationalTsing Hua University in Hsinchu, Taiwan. The paper applies a method developed in another domain to find the optimal product mix in a semiconductor manufacturing line.

On behalf of the associate editors, I congratulate Dr. Chang on being selected.

> Anthony J. Muscat, T-SM Editor-in-Chief Department of Chemical and Environmental Engineering University of Arizona Tucson, AZ, USA

## CALL FOR NOMINATIONS TO IEEE FELLOW CLASS OF 2019

IEEE Fellow is a distinction reserved for select IEEE members. The honor is conferred by the Board of Directors upon a person with an extraordinary record of accomplishments in any of the IEEE fields of interest.

If you know of an IEEE colleague who is a Senior Member or Life Senior Member in good standing, has completed five full years of service in any grade of IEEE Membership and who has made an outstanding contribution to the electronic or electrical engineering profession in any of the IEEE fields of interest, you can nominate this person in one of four categories: Application Engineer/Practitioner, Educator, Research Engineer/Scientist or Technical Leader.

Nominations for the Fellow Class of 2019 are now being accepted.

To learn more about the Fellow program and the application process, visit http://www.ieee.org/fellows.

The deadline for nominations is 1 March 2018.

## UPDATES FROM THE 2017 EDS PHD STUDENT FELLOWSHIP RECIPIENTS

Carmen Lilley EDS Student Fellowship Committee Chair

The EDS PhD Student Fellowship Program is designed to promote, recognize, and support graduate level study and research within the Electron Devices Society's

Fields of Interest, The 2017 EDS PhD Student Fellowship recipients were:

Renjie Chen - University of California, San Diego, USA

Po-Hsun Chen - National Sun Yatsen University, Taiwan

Hao Yu - imec/Katholieke Universiteit, Leuven, Belgium

Renjie Chen is currently a PhD candidate in the Department of Electrical and Computer Engineering at the University of California, San Di-

ego. He joined Prof. Shadi A. Dayeh's group in 2013, and worked at Center for Integrated Nanotechnologies (a Sandia National Labs affiliated organization) for 3 years as a facility user. Under Prof. Dayeh's supervision, Renjie focused his research efforts on the metallurgy of forming metal contacts to nanoscale semiconductor channels for materials relevant to current and emergent transistors that are only a few atoms across. They devised a variety of fabrication processes to combine precisely controlled nanochannels with in situ TEM (Transmission Electron Microscopy) heating platforms to record the dynamics of metal-semiconductor solid-state reactions.

Po-Hsun Chen is a PhD candidate in the Department of Physics at National Sun Yat-sen University, under the direction of Professor Ting-

Chang Chang. His main field of study is in resistive random access memory (RRAM), which is a non-volatile memory for next generation electronic devices. His research focuses on applying transparent conductive oxide (TCO) within the RRAM structure to further enhance device performance and reliability. In addition, he is also working to solve forming voltage issues by introducing a new sidewall spacer in RRAM. Another recent project has him working closely with other researchers to develop vanadium-based selector devices. To date, he has authored 23

peer-reviewed journal papers covering various electron devices.

Hao Yu received his B. S. and M. S. degrees in Microelectronics and Solid-State Electronics from Fudan University in 2010 and

2013, respectively. He is currently a PhD candidate affiliated to imec and Katholieke Universiteit Leuven under supervision of Dr. Nadine Collaert and Prof. Kristin De Meyer, working on metal-semiconductor contact resistances. As high contact resistances become major obstacles that compromise performance of modern CMOS devices, Hao Yu has developed high-accuracy test vehicles and reported multiple contact schemes meeting the 10-9 Ω·cm<sup>2</sup> contact - resistivity industrial target. He has contributed 14 articles to peerreviewed journals and 12 to international conferences.

> Carmen Lilley EDS Student Fellowship Committee Chair University of Illinois at Chicago Chicago, IL, USA

## 2018 PhD Student Fellowship

Description: One year fellowships will be awarded to promote, recognize, and support PhD level study and research within the Electron Devices Society's field of interest. The field of interest for EDS is all aspects of engineering, physics, theory, experiment and simulation of electron and ion devices involving insulators, metals, organic materials, plasmas, semiconductors, quantum-effect materials, vacuum, and emerging materials. Specific applications of these devices include bioelectronics, biomedical, computation, communications, displays, electro and micro mechanics, imaging, micro actuators, optical, photovoltaics, power, sensors and signal processing.

Three fellowships are expected to be awarded to eligible students in each of the following geographical regions for 2018: Americas, Europe/Middle East/Africa, and Asia & Pacific. Only one candidate can win per educational institution.

**Prize:** US\$5,000 to the student and if necessary funds are also available to assist in covering travel and accommodation costs for each recipient to attend the EDS Governance meeting in December 2018 for presentation of the award plaque. The EDS Newsletter will feature articles about the FDS PhD Fellows and their work over the course of the next year.

Eligibility: A candidate must be an IEEE EDS student member at the time of nomination; be pursuing a doctorate degree within the EDS field of interest on a full-time basis: and continue his/her studies at the current institution with the same faculty advisor for twelve months after receipt of award. The nominator must be an IEEE EDS member and preferable be serving as the candidate's faculty advisor. Previous award winners are ineligible.

Basis for Judging: Demonstration of his/her significant ability to perform independent research in the fields of electron devices and a proven history of

May 15, 2018

Submission Deadline

## **Nomination Package**

- Nomination letter from an EDS member

- Two letters of recommendation from individuals familiar with the student's research and educational credentials. Letters of recommendation cannot be from the nominator.

- One-page biographical sketch of the student (including student's mailing address and email address)

- Two-page (maximum) statement by the student describing his or her education and research interests, accomplishments and graduation date

- One copy of the student's under-graduate and graduate transcripts/grades. Please provide an explanation of the grading system if different from the A-F format.

### **Timetable**

- Completed nomination packages are due at the EDS Executive Office no later than May 15, 2018

- Recipients will be notified by July 15

- Monetary awards will be given by August 15

- Formal award presentation will take place at the EDS Governance Meeting in December

Please submit application packages via e-mail or mail:

Email: edsfellowship@ieee.org

IEEE EDS Executive Office PhD Student Fellowship Program 445 Hoes Lane Piscataway, NJ 08854 USA

For more information contact:

edsfellowship@ieee.org

#### Visit the EDS website:

http://eds.ieee.org/eds-phd-student-fellowship.html

## UPDATES FROM THE 2017 EDS MASTERS STUDENT FELLOWSHIP WINNERS

Carmen Lilley EDS Student Fellowship Committee Chair

The EDS Masters Student Fellowship program is designed to promote, recognize, and support Masters level study and research within the Electron Devices Society's Fields of Interest.

The 2017 EDS Masters Student Fellowship recipients were as follows:

Abhinandan Borah - Columbia University, New York, USA

Jiabin Wang - Tsinghua University, Beijing, China

Abhinandan Borah is currently pursuing doctoral studies in the Department of Electrical Engineering at Columbia University.

He received his bachelor's degree

in Electronics and Communication Engineering from National Institute of Technology, Silchar in 2013. After graduation, he worked at IBM India as an Associate Systems Engineer for a year. In 2014, he joined Tata Institute of Fundamental Research (TIFR), Mumbai as a Junior Research Fellow in the Nanoelectronics lab with a fellowship from the Department of Science and Technology, India. At TIFR, his research focus was nanoscale devices with 2D materials. Advancing his interest in unconventional nanoelectronics, his current research at Columbia involves understanding and developing heterostructure devices of 2D semiconductors through both simulations and experiments, in order to contribute towards a postsilicon era in future.

Jiabin Wang received the B.E degree in electronic science and technology from Tsinghua University, Beijing, China, in 2015, where he is currently pursuing the M.E degree

in the Institute of Microelectronics, supervised by Professor Tian-Ling Ren. His research interests include thin film transistors, synaptic de-

vices, neuromorphic computation systems, low-voltage applications, ferroelectric applications, and critical technology for advanced microand nano-electronics. His current research topic is developing novel brain-like electron devices and neuromorphic computation system with higher efficiency, low energy consumption, and novel functionality, to build artificial computation systems in high similarity and comparable efficiency with the human brain.

> Carmen Lilley EDS Student Fellowship Committee Chair University of Illinois at Chicago Chicago, IL, USA

## 2018 Masters Student Fellowship

**Description:** One-year fellowships will be awarded to promote, recognize, and support graduate Masters level study and research within the Electron Devices Society's field of interest. The field of interest for EDS: all aspects of engineering, physics, theory, experiment and simulation of electron and ion devices involving insulators, metals, organic materials, plasmas, semiconductors, quantum-effect materials, vacuum, and emerging materials. Specific applications of these devices include bioelectronics, biomedical, computation, communications, displays, electro and micro mechanics, imaging, micro actuators, optical, photovoltaics, power, sensors and signal processing.

Three fellowships are expected to be awarded to eligible students in each of the following geographical regions for 2018: Americas, Europe/Mid-East/Africa, and Asia & Pacific. Only one candidate can win per educational institution.

**Prize:** US\$2,000 and a plaque to the student, to be presented by the Dean or Department head of the student's enrolled graduate program.

Eligibility: Candidate must be an IEEE EDS student member at the time of nomination; be accepted into a graduate program or within the first year of study in a graduate program in an EDS field of interest on a full-time basis; and continue his/her studies at a graduate education institution. The nominator must be an IEEE EDS member and preferably be serving as the candidate's mentor or faculty advisor. Previous award winners are ineligible.