#### Transistors at 75—Past, Present, and Future

CHENMING HU TSMC DISTINGUISHED PROF. EMERITUS, UNIV. OF CALIFORNIA BERKELEY IEEE LIFE FELLOW, MEDAL OF HONOR RECIPIENT

Early Transistors: Three Bell Labs researchers born on three continents invented the transistor 75 years ago-John Bardeen in America (Madison USA), William Shockley in Europe (Liverpool England), and Walter Brattain in Asia (Xiamen China). Another engineer, John Pierce, suggested the name "transistor" because it connects the new device to the already familiar terms: transconductance, resistor, etc.

Transistor became a household word when SONY introduced a shirt-pocket-size transistor radio using Texas Instruments transistors and a standard 9V battery in 1957 and went on to sell 6 million units of that model. IBM introduced the first mass-produced transistor computer in 1958.

From Ge to Si to Heterogeneous **Integration**: The early transistors were made with germanium. Around 1960, silicon became the preferred semiconductor because its larger bandgap greatly reduces the transistor leakage current especially when the transistors are hot.

While Si wafers are now entrenched as the substrate material. Ge has returned in the form of Si<sub>x</sub>Ge<sub>1-x</sub> alloy thin films added on the Si substrates during IC production. SiGe is playing increasingly critical roles in advanced MOSFETs for enhancing electron and hole mobilities and other benefits. Optical, magnetic, and ferroelectric materials have also been integrated into Si technology. Wide band-gap semiconductors GaN on Si or SiC substrates are used for making high-voltage transistors.

How the Transistor Density Grew and Grew: Jack Kilby of TI received the 2000 Nobel Prize in Physics "for his part in the invention of the integrated circuits". Robert Noyce of Fairchild Semiconductor is considered the other major contributor and his

President Barack Obama shakes hands with Dr. Chenming Hu

patent content bears a great resemblance to modern IC technology, but he had died before 2000.

Today, we take for granted that over 100 million silicon wafers are used each year to produce about 10<sup>20</sup> transistors with the smallest features the size of tens of atoms. But the growth of circuit density could have halted for any one of several reasons long ago but for the ingenuity and hard work of many people and several industries. The semiconductor equipment industry kept improving lithography and other production tools. The process engineers in the leading IC fabs delivered high-yield nano-fabrication technologies for making tiny intricate structures. The

high costs of technology development and fabs were once considered potential showstoppers - until industry consolidation and the foundry model created huge IC manufacturing companies. The EDA industry's design automation tools reduced the barrier to designing large complex ICs, and accurate standard transistor models bridged the physical fabs and the digital EDA tools. Ensuring the long-term reliability of billions of transistors turned out possible through better materials, manufacturing, understanding of failure mechanisms, and failure rate modeling. But past success does not guarantee future success. The hill gets steeper.

Power Consumption, MOSFET, CMOS, Thin-Body CMOS, 3D Transistor: If we want to cramp a hundred times more transistors into a chip of a certain size, we need to reduce the power consumption per transistor by about a hundred times. Otherwise, heat removal would be a nightmare, not to mention the impact of such energy use on mother earth. A major change that reduced power consumption was the transition from bipolar transistors to MOSFET and then CMOS. CMOS technology reduced the standby current of circuits to nothing but the transistor leakage current.

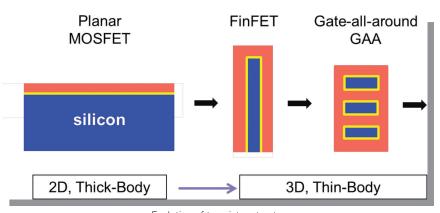

Evolution of transistor structure

The basic MOSFET structure remained unchanged from 1960 for 50 years until reducing MOSFET size further without degrading leakage, speed or switching energy became impossible. In 2011 Intel adopted the first 3D transistor, FinFET for production. FinFET and the thinbody MOSFET concept arise from the insight that the leakage current basically cannot flow within several nanometers (nm) of the Si surface because the surface potential is well controlled by the gate voltage. In the figure showing the MOSFET evolution, FinFET has a vertical Si fin (in blue), about 10nm thin, as the transistor body. The body is covered by gate oxide (in yellow) and gate metal (in orange) and leaves no Si outside the range of strong gate control. It reduces the leakage current by orders of magnitude. Furthermore, the FinFET size can be reduced every few years as long as the fin thickness is also reduced. Another thinbody MOSFET demonstrated in the same DARPA research project as Fin-FET is the ultra-thin-body SOI (UTB-SOI or FDSOI). Being a 3D transistor, FinFET has a smaller footprint than the planar MOSFET. It has the same advantage as building tall buildings

instead of single-story buildings in a crowded city.

The fin of FinFET has become thinner and taller with each new technology node. At the 2nm node, it is too hard to make the required thin and tall fin by lithography and etching. The industry is adopting a new 3D thin-body MOSFET structure called NanoSheet or GAA (gate-all-around), where the thin body is made by epitaxial growth and etch-release. The figure above illustrates the evolution from FinFET to GAAFET.

# Examples of What May Happen Next

3D transistors and 3D packaging are here to stay. 3D NAND technology is an excellent example of a costeffective monolithic 3D memory IC. Monolithic 3D logic IC may start with stacking PFET on top of NFET to reduce CMOS-gates' footprints. Future monolithic 3D IC paths may employ transferred single-crystal semiconductor films, self-assembled 2D semiconductors, or amorphous or polycrystalline semiconductor films as the transistor material. 0.6nm MoS2 monolayer has been used to demonstrate 1 nm gate-length thinbody MOSFET. Power supply voltage

and power consumption may be reduced by many folds with Negative-Capacitance Transistor (NCFET). It requires inserting a thin layer of ferroelectric such as HfZrO in the MOSFET gate stack. Another advantage of adding the thin ferroelectric is its memory property that may be exploited for computing in memory or fast non-volatile memory.

## Does the World Need More and Better Transistors?

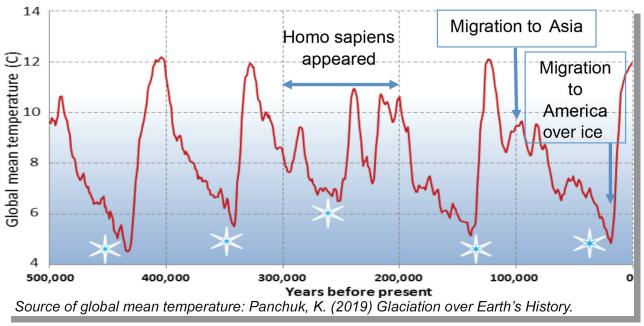

The enormity of the task of dealing with global warming (see the graph below) is beginning to be realized. What about the task of dealing with the next Ice Age, which is predicted to start in 1500 years based on Earth's orbit? Humans may need order-of-magnitude greater capabilities to deal with future existential challenges.

But how can we possibly get 10x or more problem-solving power? Electronics are the key. While all technological advances bring forth new capabilities, electronics are unique for three reasons.

Its impact is infectious. Highspeed communication and computing, automation, internet, Al, robotics, and

Variation of global mean temperature

- yet-unknown future technologies enabled by better transistors have lifted and will lift up all technologies, industries, and sciences. And they in turn lift each other.

- ICs use relatively small amounts of materials. And the less materials they use (by being made smaller), the faster and more capable they become.

- 3) Theoretically, the energy required for information manipulation can still be reduced by more than a thousand times. Although we have no idea how to get there now, reducing the energy by 10 or 100 times would not violate physical laws. The energy efficiencies of other technologies (transportation, lighting, ...) are mostly already around 50% of their theoretical limits.

### Lesson From the Past and Task for the Future

The history of transistors is a journey log of climbing one hill after another. Until we get high enough on one hill, we can not even see the terrain and map a route to reach the next hill. Importantly, with each hill climbed, we accumulate and discover new skills that help us move forward. Deposit and etch materials one atomic layer at a time? Sure. Economically on millions of wafers every week at high yield with billions of transistors on each chip? Sure. Magnetic, ferroelectric, and optical materials too? Sure. Switch the magnetic polarization with an electric field, not current? Sure. Do anything that does not violate physical

laws? Probably. Continuing the hard climbs while diligently scouting for new provisions and possible routes is the best way to create future electronics, which may be very different in devices, materials, and operating mechanisms. The new provisions and route will come from university and industry researchers with deep knowledge in physics, chemistry, biology, and algorithms—and the help of expanding problem-solving capabilities, time, and luck.

#### **Biography**

Dr. Hu received his B.S. degree from National Taiwan University, which honored him with its Distinguished Alumni Award,

and M.S. and Ph.D. degrees from UC Berkeley. Dr. Chenming Hu is called the Father of 3D Transistors for developing the FinFET in 1999. Intel hailed FinFET as the most radical shift in semiconductor technology in over 50 years. Modern computers, smart phones, and the internet all ran on 3D transistor processors. He received the US NationalTechnology and Innovation Medal from President Obama in 2016. He leads the ongoing development of BSIM, a suite of industry-standard computer models of transistors. University of California provides it royalty free for the global IC industry to design integrated circuits worth well over a trillion US dollars since 1995. IEEE, world's largest technical professional organization, gave him its highest award,

Medal of Honor, in 2020 for helping to "keep Moore's Law going over many decades" after lauding him as "Microelectronics Visionary" for "achievements critical to producing smaller yet more reliable and higher-performance integrated circuits" in 2009. The 2013 Kaufman Award cited his "tremendous career of creativity and innovation that fueled the past four decades of the semiconductor industry". Dr. Hu is TSMC Distinguished Chair Professor Emeritus of the University of California, Berkeley. From 2001 to 2004 he was the Chief Technology Officer of TSMC, now the world's largest semiconductor company. He was the board chairman of the nonprofit Friends of Children with Special Needs and the East Bay Chinese School. He has authored six books and 1000 research papers and received over 100 US patents and honorary doctoral degrees from the University of Hong Kong and NYCU in Taiwan. He is honored with memberships in the US National Academy of Engineering, Chinese Academy of Sciences, US Academy of Inventors, The World Academy of Sciences and Academia Sinica. His other professional honors include Asian American Engineer of the Year; Silicon Valley Engineering Hall of Fame; IEEE Jack Morton Award, Solid State Circuits Award, Nishizawa Medal, and the EDS Education Award for "distinguished contributions to education and inspiration of students, practicing engineers and future educators." He also received UC Berkeley's highest honor for teaching-the Berkeley Distinguished Teaching Award.