APRIL 2019 VOL. 26, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: CARMEN M. LILLEY

#### TABLE OF CONTENTS

| Save the Date! EDS Governance Meeting Series |

|----------------------------------------------|

| TECHNICAL BRIEFS                             |

| UPCOMING TECHNICAL MEETINGS                  |

| SOCIETY NEWS                                 |

| AWARDS & RECOGNITION                         |

| YOUNG PROFESSIONALS                          |

| CHAPTER NEWS                                 |

| MQ, DL AND CONFERENCE REPORTS                |

SOI was first mentioned in the 1960s during the search of epitaxial-

(continued on page 3)

#### SAVE THE DATE!

**EDS Governance Meeting Series** 25-26 May 2019 Tarragona, Spain

CHAPTER EDUCATIONAL OUTREACH ...... 34

EDS-ETC by ED Netaji Subhash Engineering College

REGIONAL NEWS ...... 37

EDS MEETINGS CALENDAR...... 52

EDS-ETC by ED Malaysia Chapter IEEE Electronic Exploration Camp

Student Chapter

EDS MISSION, VISION AND FIELD OF INTEREST STATEMENTS ...

#### ECHNICAL

#### MARVELS IN MICROELECTRONIC DEVICES STRUCTURE: ACTUATE, ISOLATE AND INTERCONNECT

BY SIMON DELEONIBUS, PAST CHIEF SCIENTIST, CEA, LETI

Looking for the Holy Grail device having the lowest parasitics, the highest performance and the lowest leakage current has been the rule of the game for microelectronics since Large Scale Integration (LSI) offered the possibility to design complex circuits for digital and mixed signals applications. In their time, groundbreaking ideas to actuate, isolate and interconnect all devices with the smallest footprint possible have been proposed. Among these, channel/substrate engineering with Silicon on Insulator (SOI), Local Oxidation of Silicon (LOCOS) and Shallow Trench Isolation (STI), and copper interconnects have been developed worldwide, as breakthroughs in high risk/high gain projects pushed by highly talented teams and their charismatic leaders.

The attractiveness of SOI was put forward for its unbeatable isolation capabilities and low junction capacitance, especially for power, radio frequency or rad-hard applications. Initially considered as restricted to niche applications, SOI is nowadays considered a mainstream substrate, a must for RF and Low Power applications and is a candidate to replace bulk Si in the high performance market.

ly grown Silicon on Sapphire (SOS), which was supposed to "almost" epitaxially match perfectly with Si (100). The "almost" was actually a best case 7% crystallographic strain mismatch, thus thermal mismatches, between Si and sapphire induced a substantial number of crystallographic defects, such as threading dislocations (106–107/cm<sup>2</sup>) [1].

## ELECTRON DEVICES SOCIETY

#### President

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

#### **President-Elect**

Meyya Meyyappan NASA Ames Research Center E-mail: m.meyyappan@nasa.gov

#### **Treasurer**

Subramanian S. Iyer UCLA E-mail: iyer@ieee.org

L-Iriali. Iyel@leee.org

#### Secretary

Jacobus Swart FEEC/UNICAMP

E-mail: jacobus@fee.unicamp.br

#### Jr. Past President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### Sr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Vice President of Membership and Services

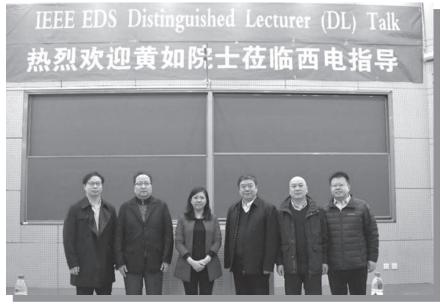

Ru Huang Peking University

E-mail: ruhuang@pku.edu.cn

#### Vice President of Publications and Products

Tsu-Jae King Liu University of California at Berkeley E-mail: king@eecs.berkeley.edu

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

#### Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith

IEEE Operations Center

E-mail: tlsmith@ieee.org

#### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

#### **Content Management**

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2019                                                                                              | TERM                                          | 2020                                                                                                                                            | TERM                                                 | <u>2021</u>                                                                                                                              | TERM                                          |

|---------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Joachim N. Burghartz Ru Huang Shuji Ikeda Meyya Meyyappan Arokia Nathan Jacobus W. Swart Bin Zhao | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) | Roger Booth<br>Mukta Farooq<br>Edmundo A.<br>Gutierrez-D.<br>Benjamin Iniguez<br>Carmen M. Lilley<br>Durga Misra<br>Manoj Saxena<br>Sumant Sood | (1)<br>(2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(1) | Paul Berger<br>Navakanta Bhat<br>Maria De Souza<br>Kazunari Ishimaru<br>William (Bill) Nehrer<br>Murty Polavarapu<br>Camilo Velez Cuervo | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) |

### NEWSLETTER EDITORIAL STAFF

#### **Editor-In-Chief**

Carmen M. Lilley University of Illinois at Chicago E-mail: clilley@uic.edu

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Rinus Lee GlobalFoundries E-mail: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

#### Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Edmundo A. Guiterrez-D. INAOE

E-mail: edmundo@inaoep.mx

#### REGION 8

#### Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Marcin Janicki Lodz University of Technology E-mail: janicki@dmcs.pl

#### UK, Middle East & Africa

Jonathan Terry

The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Mike Schwarz Robert Bosch GmbH E-mail: mike.schwarz1980@ googlemail.com

#### REGION 10

#### Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu

Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

#### Newsletter Deadlines

| <u>ISSUE</u>  | DUE DATE                 |

|---------------|--------------------------|

| April<br>July | January 1st<br>April 1st |

| October       | July 1st                 |

| January       | October 1st              |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2019 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

#### MARVELS IN MICROELECTRONIC DEVICES STRUCTURE: ACTUATE, ISOLATE AND INTERCONNECT

(continued from page 1)

The first demonstration of SOS was made in 1968 by HM Manasevit and WI.I. Simpson at North American Aviation, Inc., later on known as North American Rockwell Corp. [2], [3]. Following a decomposition of SiCl4 by H2 at 1250 °C, the substrate was reduced by Si. Further coalescence of the reacting Si atoms occurred on the surface of alpha alumina.

Jean Pierre Colinge, 2012 IEEE A. Grove Award recipient, now with CEA, LETI, reports: "In the early 1980's, the only proven SOI technology was SOS (Silicon on Sapphire), which was used in military/ aerospace applications because of its resistance to radiation, and in some Hewlett-Packard computers, the 1000 Series processor in the L-Series computers introduced in 1979 [6]. SOS technology was, however, clearly unsuitable for 3D monolithic integration, and other techniques, based on laser/lamp melting and

recrystallization or various epitaxial techniques, were developed." From the late 1970s to the beginning 1990s, various alternatives to SOS were developed on full sheet substrates (BESOI by IBM in the 1970s; ELTRAN by Canon in 1990) or by 3D process integration (Zone Melted Recrystallization ZMR since the 1980s). "The real breakthroughs in SOI wafer fabrication were the Separation by Oxygen Implantation (SI-MOX) technique, first used in 1978 to fabricate CMOS circuits by NTT [4], and the Smart-Cut process, invented by LETI [5], [7]." SIMOX kept on improving by perfecting substrate annealing during oxygen implantation and high temperature annealing (by CEA,LETI at 1300 °C) [8], multi-implantation (by Monsanto) [9] and low energy implantation (by Spire) [10]. Defect density drastically dropped by 4 orders of magnitude (10<sup>2</sup>–10<sup>3</sup>/ cm<sup>2</sup>) compared to SOS.

Since the late 1960s, Michel Bruel, was involved at CEA, LETI to develop defect free heavy dose ion implantation. With his team and the collaboration of visiting Professor Stoemenos, of Thessaloniki University, he was the right person to successfully address the reduction of defect density in SI-MOX, which he succeeded in, and finally he invented SMARTCUT. Michel Bruel says: "I wanted to imagine new solutions better suited than SIMOX for electronic mass market applications. I thought of a fracturing process, based upon defects generated at their projected end of range (Rp) by light ions implanted at high dose, giving rise to the formation of nano-gaseous bubbles and nano-fracturing. Hydrogen, or helium gas ions, would penetrate into silicon without introducing any damage along the major part of the Rp. By tuning the acceleration voltage on the implanter, we could choose the depth of the nano fracturation layer, i.e. the

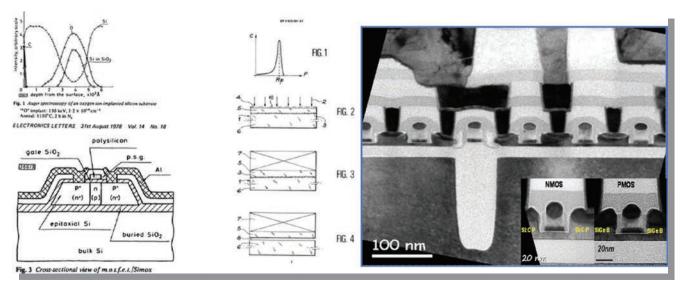

(left ) The first SIMOX paper [4]. (middle) Smartcut principle: European patent EP/FR9111491, filed Sept. 18, 1991 by Michel Bruel (CEA, LETI)[5] showing the 3 major steps of ion implant into the substrate through a screening layer, bonding to a handle wafer and splitting of the new substrate at the fracture zone around Rp after heat treatment. (right) Ultra thin FD devices for CMOS scaled logic applications.(Tsi = 6 nm TBOx = 20 nm) Lg = 14 nm processed on 300 mm SMARTCUT wafers (middle and right figures provided by courtesy of CEA, LETI)

thickness of the layer to be created. After the implant, we bonded the substrate to a handle wafer, applied a thermal cycle that fractured the implanted substrate. We removed the initial substrate before smoothly polishing the final SOI substrate surface. The initially fractured wafer was recyclable. This process was directly applicable in a microelectronics environment. We wanted to keep some lead time: the invention was kept confidential from 1991 to 1995." Meanwhile, SIMOX was used to process radiation hardened high speed microprocessors of the 68000 family, for military and space applications, as soon as 1988. Michel Bruel received many awards for the invention of the SMARTCUT process, among which was the 2008 IEEE Cledo Brunetti Award. In 1992, in the context of the fall of Berlin wall, André-Jacques Auberton-Hervé and Jean-Michel Lamure started SOITEC, with the support of Michel Bruel in the clean rooms of CEA, LETI, and were convinced to apply the technology to future low power and high performance civilian applications. Initially a company of 4 employees, today SOITEC counts 1000 employees worldwide. SOITEC has ramped up the SMARTCUT wafer production since 1993 and is nowadays the provider of 90% of the SOI market worldwide. Auberton-Hervé, SOITEC CEO until 2015, declares: "We licensed SEH in 1997 and used the money to invest in our first factory. Nobody believed we could challenge them not only on innovation but also on production." SMARTCUT SOI wafers have a diameter range from 50 to 450 mm, with the lowest defect density, comparable to what is provided on commercial bulk silicon by volume. The SMARTCUT principle is applied to many different materials that could be bonded to an oxidized Si wafer.

Ghavam Shahidi, the IEEE 2010 Cledo Brunetti and 2006 JJEbers Awards recipient, was among those who pioneered the realization of VLSI designs on Partially Depleted SOI as soon as 1989 at IBM. Shahidi says: "Over the first 10 years, the biggest

'non-technical' challenges were convincing the IBM management and end users to commit product to SOI technology." It took 8 years in device engineering and development to achieve the first complex circuit demonstration (the Power PC601). The "first commercial IBM's Power 4 processor in 180 nm CMOS SOI technology, came out in 2001, first IBM's giga frequency processor and largest chip at the time." Other companies adopted partially depleted SOI in the 180 down to 45 nm nodes, such as Freescale (Power PC7455 CPU), AMD (K series) or SONY (Xbox360, PS3, Wii).

Fully depleted and multigate/ Gate-All-Around architectures have been studied since the 1980s by SONY [11], CEA,LETI [12], Hewlett-Packard [13], IMEC [14] and are necessary to reach a MOSFET minimum subthreshold slope of 60 mV/dec, and thus reduce drastically leakage current. The reduction of Si (TSi) and buried oxide (BOx) thicknesses are the prime challenges to scaledown CMOS devices. It took approximately ten years to achieve sub-20 nm gate lengths devices on less than 10 nm thin SOI and 10 nm thin BOx on 300 mm wafers [15], OKI was the first company to ship in 2000 an ultra low power circuits based on FDSOI, including an MCU, power circuits, memory and LCD driver. STMicroelectronics, IBM and Globalfoundries adopted FDSOI for their sub-28 nm nodes, moving towards 10 nm. As such, SMARTCUT is a desirable choice for monolithic 3D integration based on thin film devices [16].

Beyond digital applications, SOI is fulfilling the promise of penetrating the More-Than-Moore diversification market. SMARTCUT is providing 90% of the RF Front-End devices for mobile phones. The substrate engineering has been refined by including high resistivity and a trap rich interface at the buried oxide backside [17], [18] to enhance the final apparent substrate resistivity and, thus, reduce the cross talk to the substrate significantly. Many teams worldwide such as IBM and CEA, LETI/STMicroelectronics,

have been developing the integration of RF and mixed signal technology on SOI since the early 2000s. The exceptional vertical isolation and high quality passivation brought by such a thick oxide, combined to high resistivity silicon and trap rich oxide backside interface, makes it ideal to enable cointegrated RF switches with LNA [19], [20]. Auberton-Hervé concludes: "In the past 3 decades. SOI has also been the test bench for Si based diversification for sensors, photonics systems, on-chip applications for communication and data transmission, and concentration PV system markets. It is still able to expand to other areas."

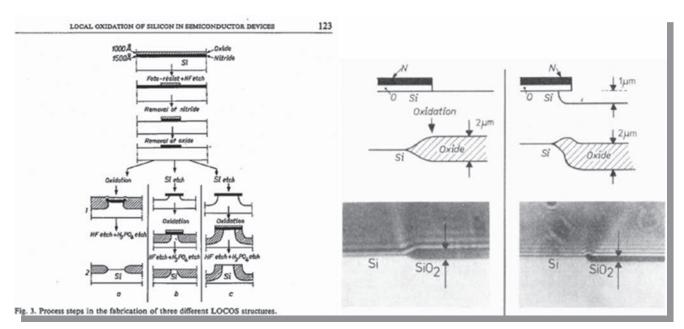

Lateral field isolation is anyway necessary whatever the substrate. The invention of LOCal Oxidation of Silicon (LOCOS) brings us back to the late 1960s when E. Kooi, J.A. Appels and their team at Philips Research Labs were strongly committed to advanced microelectronics research. Unfortunately, both of these highly talented individuals passed away. We had the kind contribution of Prof. Pierre H. Woerlee, at Technical Univ. of Eindhoven (Netherlands), the first non-US General Chair of the IEDM, who worked with E. Kooi and J.A. Appels in the 1980's at Philips Research Labs. The LOCOS isolation has been nurturing microelectronics business for decades and has been applied into other types of applications such as microsystems or power devices. Else Kooi was the 1990 IEEE Cledo Brunetti Award recipient.

The introduction of LOCOS needed new process alternatives. LOCOS isolation posed new constraints at the integration level: knowledge on selective oxidation, nitride selective etching, stress induced in the active area during oxidation, generation of stacking faults or dislocations depending on the oxidation conditions, nitridation of active area edge (Kooi effect), etc. The fact that the silicon nitride oxidation rate is much less than Si's (under 1 atm it is several 10x higher), is a remarkable property that was advantageously exploited by E. Kooi and his team (1966)

(left) LOCOS isolation invented by Appels and Kooi, first presented at 3rd Conference Solid State Devices in 1969 at Exeter(UK) [21]: three options for process flow showing the selective oxidation of silicon and increasing recess of field oxide. No pad oxide was used (right) LOCOS isolation: semirecessed and recessed [22]. A pad oxide is used to reduce dislocations. The bird's beak and bird's head appear on the semirecessed and recessed versions respectively. (by permission of Koninklijke Phillips Electronics N.V.)

patent [23]) and published in 1969 and 1970 [21]. The initial motivation to introduce LOCOS isolation was to reduce the lateral diffusion of dopants that reduced the distance between active areas and increased the lateral parasitic capacitance of p-n junctions in planar technology. That, of course, had great impact on bipolar devices too and could be extended to MOS-FET technology. Marc J. de Vries and Kees Boersma reported in 2005 [24]: "All this happened in connection with MOS (Metal Oxide Semiconductor) ICs...it was quite some time before the Nat. Lab. was prepared not only to work on bipolar ICs for analogue purposes, but also to work on MOS, which was considered to be more suitable for digital techniques."

A dopant free lateral recessed isolation was needed. The solution they imagined was to recess an insulator (silicon dioxide) because the direct moat isolation was degrading the step coverage problem (gate metallization and lithography), without stopping the diffusion of dopants. LOCOS isolation, in spite of the bird's beak introducing a feature size loss, was an elegant solution at the introduction of polysilicon gate. For decades, major teams worldwide have been working on a huge number of solutions to reduce the bird's beak, to planarize and reduce strain at the active area edge. These solutions were rich of imaginative constructions named SWAMI (Sidewall Masked Isolation), Poly Buffer LOCOS, SILO (Sealed Interface Local Oxidation of Silicon), SuperSILO, FuROX, etc., aiming at a bird's beak reduction and planarization of the topography with extra process costs as compared to the initial process. The whole microelectronics business has been using them intensively until the early 2000s, and still adopt them for specific solutions in the More-Than-Moore diversification domain. None of the modified LO-COS solutions could totally suppress the Kooi effect (the so called "white ribbon"), because the combined use of silicon nitride and steam oxidation inherently causes it. A sacrificial oxidation removes the nitrided silicon at the active area edge and allows the growth of a reliable non-thinned gate oxide. Kooi and Appels proposed very quickly (in 1970) to adopt such a solution to eliminate the Kooi effect.

Only SILO could prove zero bird's beak compatible with zero defect provided that a thin nitride (10 nm) was sealed to the active area by 1 nm Rapid Thermal Nitridation (RTN) [26], [27] or later on by a transfer under vacuum in the LPCVD reactor. The ultimate scaling limits of LOCOS type isolation schemes came from the field oxide thinning and 2-dimensional (2D) increase in bird's beak value appearing in small geometries. SuperSILO brought a drastic reduction of the bird's beak and of the 2D effects down to 100 nm active area width [27]. Meanwhile, STI was making progress thanks to Chemical Mechanical Polishing (CMP) planarization.

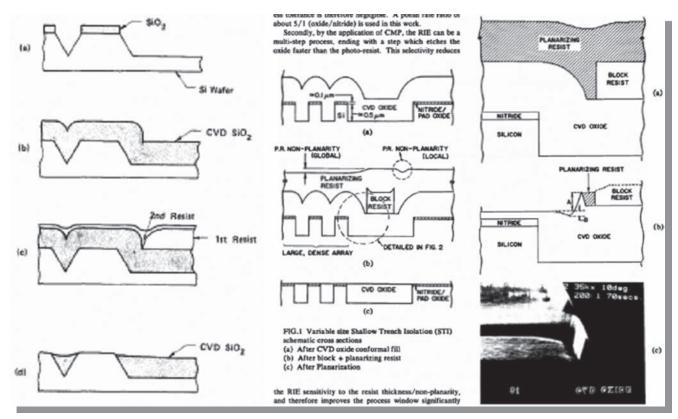

From the early 1980s, various approaches to achieve a workable STI were carried out in the semiconductor companies worldwide (such as Toshiba, [28]) using a non-selective etchback of a thin resist and deposited oxide bilayer. This technique suffered from uniformity issues and residues due to slight deviations from 1/1 selectivity etching. Bijan Davari, IBM, declares: "I realized the potential of STI around 1985 for both logic and memory applications. This

(left) STI by using sacrificial deposited oxide and several resists by Shibata et al. at 1982 IEDM [28]; (right) Planarization by block resist and etch back to alleviate the dishing problem was published by Davari et al. at 1988 IEDM [29]; CMP was added later in 1989 to obtain full planarization.

included all the CMOS technologies for both High-performance and Low-power applications and standalone DRAM." The most important hurdle for STI was the planarization for variable pattern factor isolation structures. The planarization problem resulted in too much "dishing" in large isolation areas and not adequate removal of the deposited field insulator in small isolation areas.

Besides the optimization of gate insulator breakdown, junction leakage (areal and peripheral) and field doping, a large number of CMP techniques (see also January 2019 Newsletter issue), were tested for the very first time in the FEOL process. Bijan continues: "We achieved a breakthrough around 1988 by demonstrating a perfectly planar STI process for a very demanding variable pattern factor 16Mb DRAM technology at IBM. This was achieved by a combination of chemical-mechanical polishing (CMP) and reactive-ion-

etching (RIE) with dummy patterns that were generated prior to RIE by an automated placement algorithm based on the pattern factors of the underlying isolation and the adjacent structures. We created the design tools for the pattern generation that was subsequently used in all our products [30]. The STI technology then became the industry standard for device isolation. It took us about 3 years to go from test site, single device isolation experiments to fully functional circuits, and then another 2 years to product. Our first product was a 16 Mb DRAM with STI and deep trench for storage capacitance." Davari was the IEEE 2005-JJ.Ebers and 2010 A. Grove Awards recipient.

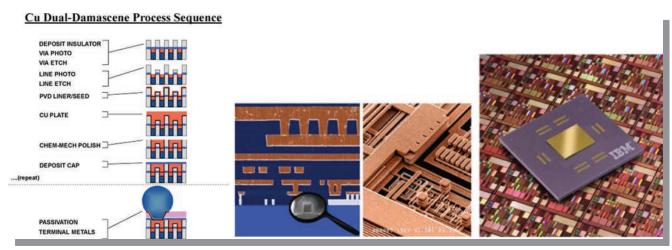

Geometric downscaling revealed limitations in materials properties such as aluminum: another major breakthrough was needed for interconnects. The introduction of copper (Cu) on-chip multilevel interconnects (BEOL, back end of line) took a long

path since the 1980's, when the limitations of aluminum (AI) wiring at smaller geometries due to scaling started to appear. The first attempt to solve scaling issues concentrated on the flattening of topography while keeping Al for metal wiring. In strong synergy with the efforts carried out on STI (hereabove), CMP was introduced by IBM in 1991 to planarize interlevel dielectrics (ILDs) on pre-etched metal lines, and to polish separate interlevel studs, or "vias" made of tungsten [30]. The obtained planarization enabled stacking of multiple wiring levels at constant minimum pitch, and improved lithographic patterning.

Important efforts were carried out to keep the conventional subtractive-etched/ILD backfill scheme to introduce Cu metallization. Its higher reflectivity pushed towards hard-mask lithography and perfect planarization of topography. The absence of volatile Cu etching byproducts at room temperature required etching temperatures

(Left )double damascene schematic process flow; (right) Publicity photos from CMOS/Cu BEOL technology announcement, showing 6-level Cu dual damascene wiring, and world's first Cu BEOL production chip (PPC750) [35] (D.Edelstein by courtesy).

higher than 200 °C (at 250 °C: by NTT [31], or at 220 °C by Rensselaer Institute [32]). The passivation of Cu lines was very critical and requested anti-corrosion treatments included in the etching steps. Further, since Cu ions can diffuse rapidly through SiO, dielectric, and can potentially poison Si devices, each Cu wire had to be encapsulated by a diffusion barrier. This requirement would have been quite difficult for subtractively-etched Cu lines, with their exposed and reacted sidewalls and top surfaces. These Cu etching difficulties coupled with the need for high-performing planarization pushed towards a different paradigm. That was the Damascene or Dual Damascene scheme with its ILD patterning, conformal metal fill, and excess metal CMP developped by IBM (see figure, Newsletter january 2019 issue and [33], [34]). Dual damascene had been introduced earlier for DRAM W interconnects [30], and emerged for Cu (VMIC 1993) [35]. Finally, IBM discovered that by modifying the recipe for electrolytic Cu plating used for packaging interconnects, they could fill high aspect-ratio lines and vias with no voids or seams, with a "superfilling" plating process that improved as the wires got narrower. It produced a quantum leap improvement in electromigration reliability (assuming integration with a proper diffusion barrier). This winning combination has kept the door open for

Moore's Law BEOL scaling, extending Cu BEOL for over 20 years and 9 generations in manufacturing [35].

Dan Edelstein, IBM, says: "In the mid 1980's, IBM started the initial drive to migrate from Al(Cu) to Cu/ low-k BEOL, initiated by my colleague C-K Hu, to meet our growing needs for bipolar-based mainframe CPU high-current circuits (with high EM reliability). In the early 1990's, the needs switched to low-parasitic capacitance, higher-density and lower-cost CMOS wiring." Edelstein adds: "Besides matched CTEs and high modulus for SiO<sub>2</sub> ILD vs. passivation, I had found in the literature that SiO, possessed a very low Cu solubility limit, despite the high diffusivity of Cu atoms, and OH-catalyzed Cu ionization in BEOLlevel electric fields leading to much faster Cu ion drift diffusion."

The team had to respond the fundamental questions of deposition, patterning and containing the interconnect material. "The retained options were: 1) PVD Cu seed + damascene (superfilling) electrolytic plating, 2) (Dual) Damascene dielectric patterning with 2-step CMP of Cu/ barrier, or 3) Full encapsulation of Cu lines and vias with diffusion barriers of TaN/Ta bilayer liner plus Si<sub>2</sub>N<sub>4</sub> dielectric cap. The combination of these barriers with SiO, interlevel dielectric, plus the additional  $Si_3N_4$  barriers between FEOL and BEOL provided

redundant protection against Cu corrosion, migration, interline leakages, and FEOL device poisoning."

The first functional microprocessor product was demonstrated in Q4 1997, as early-user hardware, on a 0.22 µm production high-performance CPU chip (PowerPC 750 for Apple). It took approximately 3/4 year to qualify this for high-volume production. "The much less mature Cu technology demonstrated the expected frequency improvement (ISSCC 1998) [35], and had tighter clock skew distributions, electromigration lifetimes and statistics way beyond the spec limit." During the past two decades, the SiOx dielectric has evolved by doping and density reduction into SiOF, SiCOH with low k SiCN(H) caps, and ultralow-k porous SiCOH (IEDM 1999 and 2006, IITC 2004) [35]. Copper/airgap for 2 fatline levels was introduced into manufacturing by Intel in 14 nm [36]. For the sub-10 nm nodes, Co or Ru wiring for the finest BEOL levels, or Cu encapsulation by Co, were envisaged (already presented by Komatsu at MRS MAM 2007) to limit/suppress electromigration [35], [37], in spite of higher Co and Ru resistivities that might be recovered for 7 nm barrierless Cu lines. D. Edelstein, A. Grill and C-K Hu are the 2019 Cledo Brunetti Award recipients for their contribution to Cu/Low K technology.

#### References

- [1] J.-P. Colinge, in "Silicon-On-Insulator Technology: Materials To VLSI", *The Kluwer international series in engineering and computer science*, Kluwer Academic Publishers, New York (1991), DOI 10.1007/978-1-4757-2121-8.

- [2] H.M. Manasevit and W.I. Simpson, "Single-Crystal Silicon on a Sapphire Substrate", J. Appl. Phys. 35, 1349 (1964)

- [3] H.M. Manasevit and W.I. Simpson, "Epitaxial deposition of silicon on alphaaluminum", US patent 379,668, filed July 1, 1964.

- [4] K. Izumi, M. Doken, H. Ariyoshi, "CMOS devices fabricated on buried SiO<sub>2</sub> layers formed by oxygen implantation into silicon", Electronics Letters, vol.14, n°18, pp593–594 (1978)

- [5] M.Bruel, "Procédé de fabrication de films minces de matériau semiconducteur", European patent EP/FR9111491, filed Sept. 18, 1991

- [6] http://www.hpmuseum.net/exhibit .php?class=3&cat=37

- [7] M. Bruel, "Silicon on insulator material technology", Electronics Letters, vol. 31, N°14, pp.1201–1202, (1995)

- [8] J. Stoemenos, C. Jaussaud, M. Bruel, and J. Margail, "New conditions for synthesizing SOI structures by high dose oxygen implantation", J. Crystal Growth, Vol. 73, p.546, 1985

- [9] D. Hill, P. Fraundorf and G. Fraundorf, Proc. IEEE SOS/SOI Workshop, p. 29, 1987

- [10] F. Namavar, E. Cortesi, B. Buchanan, and P. Sioshansi, Proc. IEEE SOS/SOI Workshop, p. 117, (1989)

- [11] T. Sekigawa and Y. Hayashi, "Calculated threshold-voltage characteristics of an XMOS transistor having an additional bottom gate," Solid-State Electronics. vol. 27, p. 827, 1984.

- [12] A.J. Auberton-Herve, J.P. Joly, P. Jeuch, J. Gautier and J.M. Hode, "Device performances of a submicron SOI technology", IEDMTech. Dig., p. 808–811 (1984).

- [13] J.-P. Colinge, "Transconductance of Silicon-On-Insulator (SOI) MOSFET's", IEEE Electron Devices Letters, vol. EDL-6, n°11, p. 573–574 (1985).

- [14] J.-P. Colinge, M.H. Gao, A. Romano, H. Maes, and C. Claeys, "Silicon-oninsulator gate-all-around device", IEDM Tech. Dig., pp. 595–598 (1990)

- [15] V. Barral, T. Poiroux, F. Andrieu *et al.*,"Experimental investigation on the scalability of the strained FDSOI CMOS technology down to 2.5nm film thickness and 18nm gate length with a TiN/HfO2 gate stack," IEDM Tech. Dig., pp. 61–64 (2007)

- [16] P. Batude, M. Vinet, A. Pouydebasque *et al.*, "Advances in 3D CMOS Sequential Integration", IEDM Tech. Dig., pp. 345–348 (2009)

- [17] D.Lederer, J.-P. Raskin, "Method of Manufacturing a Multilayer Semiconductor Structure with Reduced Ohmic Losses" patent no. FR0311347, filed September 26, 2003.

- [18] D. Lederer and J.-P. Raskin, "New Substrate Passivation Method Dedicated to HR SOI Wafer Fabrication With Increased Substrate Resistivity" IEEE Electron Device Letters, vol. 26,No. 11, Nov. 2005, pp. 805–807.

- [19] F. Gianesello, D. Gloria, C. Raynaud, S. Montusclat *et al.*, "Integrated Inductors in HR SOI CMOS technologies: on the economic advantage of SOI technologies for the integration of RF applications", Proc. IEEE SOI Conf., pp 103–104, Indian Wells(CA), Oct 1–4, 2007.

- [20] C. Raynaud, "Technology path-finders for low cost and highly integrated RF Front End Modules", IEDM Tech. Dig.,pp 466–469, San Francisco(CA), Dec. 15–17, (2014).

- [21] J.-A. Appels and E. Kooi, 3rd Conference on Solid State Devices, Exeter (UK) (1969) and also J.-A. Appels, E. Kooi, M. M. Paffen *et al.*, "Local oxidation of silicon and its application in semiconductor device technology", Philips Res. Repts 25, pp. 118–132, (1970)

- [22] J-A Appels and Pfaffen, "Local Oxidation of Silicon; new technological aspects", Philips Res Repts 26, pp.157–165, June 1971

- [23] E. Kooi, Patent # NL6614016A filed on October 5, 1966

- [24] Marc J. de Vries and Kees Boersma, "80 years of Research at Philips Nat. Lab" Pallas Publications, Amsterdam (NL) (2005)

- [26] S Deleonibus,P.Molle,J.Lajzerowicz *et al.*, "High Performance Submicron SILO Process for High Density EPROM Memories Using Rapid Thermal Nitrida-

- tion of Silicon", Proc. ESSDERC, pp. 152–155, Berlin(FRG) (1989)

- [27] S.Deleonibus, "A GIGABIT scalable SILO field isolation using RapidThermal Nitridation (RTN) of silicon", Proc ESSDERC, pp. 75–78, Leuven(Be) (1992).

- [28] T. Shibata, R. Nakayama, K. Kurosawa *et al.*, "A Simplified BOx (Buried-Oxide) Isolation Technology for Megabit Dynamic Memories", IEDM Tech. Dig., pp.27–30, San Francisco (CA)(1982)

- [29] B. Davari, C.Koburger, T.Furukawa et al., "A variable-size shallow trench isolation (STI) technology with diffused sidewall doping for submicron CMOS", IEDM Tech. Dig., pp. 92–95, San Fransisco(CA) (1988)

- [30] Carter W. Kaanta, Susan G. Bombardier *et al.*, "Dual Damascene: a ULSI Wiring Technology", Proc. VMIC, pp144–152, Santa Clara(CA) (1991)

- [31] Kazuhide Ohno, Masaaki Sato and Yoshinobu Arita, "High Rate Reactive Ion Etching of Copper Films in SiCl4, N2, Cl2 and NHr Mixture", Ext. Abs. SDDM Conf., pp. 215–218, Sendai(Japan)(1990).

- [32] Howard, B.J. and Steinbruchei, Ch., Reactive Ion Etching of Copper with BC1<sub>3</sub> and SiCl<sub>4</sub>: Plasma Diagnostics and Patterning, *J. Vac. Sci. Technol.*, A, 1994, vol. 12, no. 4, pp. 1259–1264.

- [33] M.Chow, J.E. Cronin, W.L. Guthrie et al., US patent n° 4,789,648 (1988)

- [34] K.Beyer, W.L. Guthrie, S.R. Makarewicz *et al.*, US patent n° 4, 944, 836 (1990)

- [35] a set of references can be found in: Daniel C. Edelstein, "20 Years of Cu BEOL in Manufacturing, and its Future Prospects", IEDM Tech. Dig., pp. 334–337, San Francisco(CA)(2017)

- [36] S. Natarajan, M. Agostinelli, S. Akbar *et al.*, "A 14nm Logic Technology Featuring 2nd Generation FinFET Transistors, Air-Gapped Interconnects, Self-Aligned Double Patterning and a 0.0588 μm² SRAM cell size", IEDM Tech. Dig., pp.71–74, San Francisco(CA) (2014).

- [37] C. Auth, A. Aliyarukunju, M. Asoro *et al.*, "A 10nm high performance and low-power CMOS technology featuring 3rd generation FinFET transistors, Self-Aligned Quad Patterning, contact over active gate and cobalt local interconnects," IEDM Tech. Dig., pp. 673–676, San Francisco(CA) (2017)

#### UPCOMING TECHNICAL MEETINGS

#### 2019 IEEE International Electron Devices Meeting (IEDM)

BY GARY DAGASTINE AND CHRIS BURKE

Fast-growing and diversified applications of semiconductor technologies in areas such as artificial intelligence, mmWave/5G communications, automotive and the Internet of Things are driving the development of new processors and memories, special-purpose accelerators, 3D architectures, power devices, quantum computing devices and other novel materials and devices. In response, and to better serve the needs of participants, the 2019 IEEE International Electron Devices Meeting (IEDM) (December 7-11, 2019 in San Francisco) is making modifications to its technical subcommittee structure to better align with these technology trends.

The IEDM is the world's premier and the most influential forum for the unveiling of breakthroughs and new concepts in advanced semiconductors. "The content of papers submitted to and presented at the IEDM needs to reflect the ongoing and future trends to best serve our authors and attendees," said Suman Datta, IEDM 2019 Technical Program Chair and Stinson Chair Professor of Electrical Engineering at the University of Notre Dame. "Therefore, based on input from attendees, members of the IEDM Executive Committee, and the IEDM 2018 Technical Subcommittee Chairs, we have decided to make modifications to our technical subcommittee structure this year to better align the IEDM technical program with these developing trends."

Prospective paper authors will benefit from knowing these major changes:

A new Emerging Device & Compute Technology (EDT) subcom-

mittee, co-chaired by Kuan-Lun (Alan) Cheng of TSMC and Iuliana Radu of Imec, will seek papers on emerging devices, circuits and architectures that support new computing models like neuromorphic, in-memory, approximate and quantum computing, Ising state machines, continuous time dynamical systems, lifelong learning machines, etc.

- Memory Technology (MT) -Chaired by Ming Liu of the Chinese Academy of Science, the scope of this subcommittee has been expanded beyond traditional memory technologies to include novel memory devices (e.g., PCRAM, FeFETs, RRAM, various flavors of MRAM), along with in-memory computing and processing-in-memory techniques.

- A new Advanced Logic Technology (ALT) Technical Subcommittee replaces both the former Circuit & Device Interaction and Process & Manufacturing Technology subcommittees. Chaired by Sandy Liao of Intel, this new subcommittee will seek papers in the areas of platform technologies, advanced CMOS, unit and integrated process advancements in both FEOL/BEOL, Ge, gate-all-around (GAA) devic-

es, monolithic 3D, NCFETs and TFETs.

- A new Microwave, Millimeter Wave and Analog Technology (MAT) subcommittee, chaired by Erik Lind of Lund University, replaces the former Compound Semiconductor & High-Speed Devices subcommittee. It expands the scope to include mixed-signal technologies, energy-harvesting circuits, analog front-end, tunable passives, antenna arrays, beam-formers, filters, switches, non-reciprocal devices, LNAs and PAs.

- A new Power Devices & Systems (PDS) subcommittee, chaired by Jun Suda of Nagoya University, will seek papers on topics including existing and new wide-bandgap transistors; new applications ranging from power delivery to automotive to smart grid; compact models of power devices and interactions with passives, thermal management; etc.

- A new Reliability of Systems & Devices (RSD) subcommittee, chaired by Gaudenzio Meneghesso of the University of Padova, aims to revitalize and revamp the field of reliability, given that it is as much about devices as systems. This subcommittee will encompass all aspects of reliability from variation to aging to design-for-manufacturability (DFM).

The following three IEDM technical subcommittees stay as they are:

Modeling and Simulation (MS) subcommittee chaired by Lee Smith of Synopsys

- Optoelectronics, Displays and Imagers (ODI) subcommittee chaired by Lars Zimmermann of IHP

- Sensors, MEMS, and BioMEMS

(SMB) subcommittees chaired by

Duygu Kuzum of the University

of California, San Diego.

#### Paper submission deadline

Paper submission deadline for IEDM 2019 is July 26, 2019.

#### **Further information about IEDM**

For registration and other information, visit www.ieee-iedm.org.

#### Follow IEDM via social media

- Twitter: www.ieee-iedm.org/ twitter

- LinkedIn: www.ieee-iedm.org/ linkedin

- Facebook: www.ieee-iedm.org/ facebook

## 2019 IEEE INTERNATIONAL FLEXIBLE ELECTRONICS TECHNOLOGY CONFERENCE

AUGUST 11–14, 2019, VANCOUVER, CANADA HTTPS://ATTEND.IEEE.ORG/IFETC-2019/

#### **Welcome Participants!**

On behalf of the Organizing Committee, it is our pleasure to welcome you to join us at the 2019 *IEEE International Flexible Electronics Technology Conference* (IEEE IFETC 2019) during August 11–14, 2019 at the *Simon Fraser University at Harbour Centre*, 555 W. Hastings Street, Vancouver, BC, Canada.

The 2nd IEEE IFETC 2019 is a premier conference for scientists, researchers, engineers, developers, and end-users to exchange technical research milestones and perspectives in the field of flexible electronics and their applications, including but not limiting to the following topical areas:

- Flexible transistors

- · Flexible photovoltaics

- · Flexible RFID and NFC Devices

- Flexible antennas and microwave devices

- · Flexible energy harvesting

- Flexible sensors

- Flexible lighting and displays

- Smart textiles and wearables

- Chips and circuit design for flexible electronics

- Novel materials and processes for flexible electronics

The conference is expected to offer more than 150 presentations including 5 plenary/keynotes, 5 tutorials, over 40 invited talks by internationally renowned experts in the field, and more than 100 contributed technical presentations.

We sincerely invite your participation to the excellent technical programs of IEEE IFETC 2019 to be held at one of the most beautiful places in Canada, located on the scenic waterfront overlooking the Coastal Mountains and Howe Sound in downtown Vancouver.

We look forward to seeing you in Vancouver, Canada for IEEE IFETC 2019!

Sincerely, Ravi Todi, Steering Committee Chair & George Xiao, Woo Soo Kim, General Co-Chairs

#### SOCIETY NEWS

#### Message from EDS President-Elect

Dear EDS members:

Meyya Meyyappan EDS President

I want to focus on the EDS educational activities this time. This is the most important service we can provide to our members, in my opinion. I think our members ex-

pect it too and find it valuable. Our profession constantly faces changes, in terms of disruptive technologies, new areas and applications (Internet of things, for example) and others. It is hard to keep up with everything happening in our own fields. Therefore, education beyond the traditional classroom becomes very important, and this is where EDS can play a key role.

For starters, we have a very successful Distinguished Lecturer (DL) program, which allows Chapters to organize an event for their members to hear leading EDS experts describe their cutting edge research activities. The EDS and the local chapter together partly cover the expenses of the lecturer. While the DL program is centered on a single lecturer, the Mini-colloquium (MQ) program collects 4-6 DLs in a single full-day event. More recently, EDS was one of the first Societies to introduce a webinar program that allows any member around the world to listen to an expert lecture right at their desk. We have been running monthly webinars for over three years now and it has been received enthusiastically in all ten regions. The lectures are archived on the EDS website for future on-demand viewing by the members.

At the last BoG meeting in San Francisco, a Summer School program was conceived for a potential start in 2020 as another educational offering. The Summer School, spanning 3-5 days, is expected to focus on a theme with a few experts serving as lecturers. This is not meant to be a longer version of a MQ or workshop or a different version of a conference, and we do not want a large number of speakers giving their canned onehour seminars. This is more pedagogical on an emerging topic in the EDS field of interest where a deep immersion over 3-5 days can give the attendees a fast start in this area. We are aiming this for the graduate students, postdocs, early career professionals and anyone wishing to enter a new field. Detailed tutorial-style lectures may be complemented by hands-on activities in the labs, computer work, equipment/tool demo or industry visits. We will issue a call for proposals, and individual members, chapters or some combination can respond with their selection of the topic, lecturers and the venue. The EDS subsidy will help defray travel costs of the lecturers.

I would like to remind we offer MS and PhD student fellowships every year. More information can be found on the EDS website. Please nominate deserving students, and you will see that the process is simple and streamlined. We also recognize leaders in education with the EDS Education Award. This is to

recognize those who go that extra mile beyond routine educational activities, for example, a wildly popular textbook, innovative educational tools, continuing education, promotion of EDS-related curriculum in developing regions of the world and other worthy efforts. Again, please nominate a deserving colleague, and the details can be found on the EDS website under Awards.

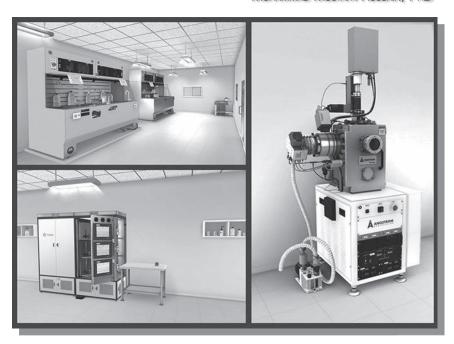

Finally, many of our members routinely develop innovative educational tools and concepts on their own, either as a part of their day job or as a hobby or simply out of the goodness of their heart to serve the community. We at EDS take pride in promoting them as we have a great reach all across the globe. A classic example is the Snap Circuit program our current EDS President Fernando Guarin initiated in 2011 to teach high school students about electronic circuits. Professor Muhammad Hussain from KAUST has just created a virtual tool to get training on device fabrication and associated equipment in cleanrooms (see related story in this issue of the Newsletter), which EDS is promoting now. This is a remarkable tool for students to get device fabrication training right at their desk and I expect it to become popular, especially in Regions 9 and 10 where access to such facilities is limited. If you have any innovative educational tools or ideas, or know of someone who does, please contact me or one of the EDS Officers and we will work with you to promote it to the community-at-large in all ten regions.

#### Message from the Editor-IN-Chief

Dear Readers,

Carmen M. Lilley EDS Newsletter Editor-in-Chief

First, I want to thank all the readwho have given me feedback on changes to the newsletter to improve access via our new html format and making suggestions for the newsletter and articles. I encourage you to please continue to send me your suggestions and ideas at clilley@uic.edu. In this issue, you will find information about our very active student chapters around the globe, with their efforts in professional development of EDS members and outreach to their local community. I think you will find their news highlights to be positively

inspiring in promoting education in the fields of IEEE and EDS to a diverse community of youths from around the world. I hope you enjoy the April issue and we look forward to sharing our July issue with you celebrating 25 Years of a Renewed Newsletter.

> Sincerely, Carmen

#### ANNOUNCEMENT OF NEWLY ELECTED EDS BOG MEMBERS

The EDS Board of Governors members-at-large election was held on December 2, 2018 in San Francisco, California. I am pleased to present the results of this election and short bios of the upcoming team that will lead EDS in years to come.

#### **Bog Members-At-Large**

A total of seven members were elected for a three-year term (2019-2021). Two of the seven electees are serving a second term, while the other five have joined the board for the first time. The backgrounds of the electees span a wide range of professional and technical interests. The following are the results of the election and brief biographies of the individuals elected.

#### **Second Term Electees:**

Navakanta Bhat received his Ph.D. in Electrical Engineering from Stanford University, in 1996. Then he worked at Motorola's Advanced

Products R&D Lab in Austin, TX until 1999. He is currently a Professor and Chair at Centre for Nano Science and Engineering, Indian Institute of Science (IISc), Bangalore. His current research

is on Nanoelectronics and Sensors. He has more than 240 publications and 24 patents. He was instrumental in creating the National Nanofabrication Centre (NNfC) at IISc, benchmarked against the best university facilities in the world. He is the recipient of IBM Faculty award and Infosys Prize 2018. He is Fellow of IEEE and INAE. He was the Editor of IEEE Transactions on Electron Devices, during 2013-2016. He is EDS Distinguished Lecturer and the chair of Nanotechnology Technical Committee of EDS. He is the founder and promoter of a startup called "PathShodh Healthcare", which builds point-of-care diagnostics for diabetes and its complications.

Murty Polavarapu is based in the Washington, DC area and is engaged in developing advanced memory and logic products for defense and aero-

space markets especially for space applications. His experience also includes introduction of advanced DRAM and Flash memory products into commercial manufacturing at Toshiba and Micron. He holds Masters degrees in Physics from India, Electrical Engineering from Howard University and Technology Management from University of Pennsylvania. He has been an active IEEE volunteer at EDS, Nanotechnology Council, IEEE-USA and Member and Geographic Activities (MGA). He currently serves on the IEEE MGA Board and also on the IEEE Governance Committee. Polavarapu also served as a United States Peace Corps volunteer teacher in rural Fiji on a leave of absence. He has been recognized with IEEE Regional Activities Achievement Award, Dominion Semiconductor President's Award and IBM Outstanding Technical Achievement Award. He has been awarded eleven US patents.

#### **First-Time Electees:**

Paul R. Berger is a Professor in Electrical & Computer Engineering at Ohio State University. He is also a Distinguished Visiting Professor at Tam-

pere University in Finland. He received the B.S.E. in engineering physics, and the M.S.E. and Ph.D. (1990) in electrical engineering, respectively, all from the University of Michigan, Ann Arbor.

He has authored over 120 articles, 5 book sections and been issued 22 patents with 6 more pending from 60+ disclosures with a Google Scholar H-index of 33. Notable recognitions include NSF CAREER Award (1996), DARPA ULTRA Sustained Excellence Award (1998), Faculty Diversity Excellence Award (2009) and Outstanding Engineering Educator for State of Ohio (2014). He has been on IEDM, IS-DRS, EDTM committees. He chairs the Columbus IEEE ED/PHO Chapter. He is Chair of the EDS technical committee on Electronic Materials and a member of Flexible Electronics committee. He is a Fellow and Distinguished Lecturer of IEEE EDS.

Maria Merlyne De Souza received the B.Sc. in Physics and Mathematics ('85) from the University of Bombay, BE in Electronics and Communica-

tions Engineering ('88) I.I.Sc, Bangalore, and PhD ('94) from the University of Cambridge, UK. She subsequently joined De Montfort University, where she became Professor of Electronics and Materials in 2003. She is currently Professor of Microelectronics at the University of Sheffield since 2007. She was elected Fellow of the Institute of Physics in 2002 and the Institute of Engineering Technology in 2006. She has published over 200 articles in Journals and conferences. She has served on the Editorial Board of JPhys D '15-'18, Associate Editor of IEEETrans in Nanotechnology ('09-'14), technical and Executive committee member of IEDM ('12-'17), technical committee member of IEEE-IRPS (2003-2013), member of the IRT Nanoelectronic Council of France ('17-'20), reviewer of key field technologies of Helmholtz Association, Forschungszentrum Jülich, 2017. She is a registered STEM ambassador in UK.

Kazunari Ishimaru is an IEEE Fellow and Deputy Director with Institute of Memory Technology Research and Development, Toshiba Memory Corporation. He conducted research on high

speed SRAM, advanced logic, Flash and emerging memories, TCAD, and compact modeling. He is currently directing Corporate R&D

strategy and business-academia collaboration. He graduated Waseda University with MS degree and joined Toshiba in 1988. He was a Vice President of R&D with Toshiba America Electronic Components Inc. from 2006 to 2010. He holds 25 U.S. patents and authored/co-authored over 50 technical papers and several invited talks and short course lectures at various international conferences. He served the IEDM General Chair in 2011, Steering committee member of ESSDERC/ ESSCIRC from 2008 to 2016. He is one of the founder member of EDTM conference and a Technical Program Committee Chair in 2018. He is currently serving the IEEE EDS VLSITechnology and Circuit Committee Chair.

Bill Nehrer has developed various technologies over his 30+ years in the semiconductors, spanning from analog CMOS to High Speed BiCMOS

and Bipolar, enabling world class products in phased array radar, audio/ video single chip solutions, modem, hard disk drive, power management, and high resolution ADCs. His focus is High Reliability and yield optimization in mass production and was elected technical Fellow at Silicon Systems, a Texas Instruments company.

Managing Texas Instruments' High Precision Analog and High Speed BiC-MOS roadmap, he directed multiple projects at worldwide TI locations. Joining PDF Solutions in 2004, he managed yield ramp and technology development consulting projects at logic fabs in 90, 65, 45, 32, 28, 20, 14, &10 nm technology. He is currently in

FabVantage technology consultancy at Applied Materials since 2018 as Senior Director, Bill holds an MSEE degree in Solid State Electrophyics from the University of Southern California and BS in Chemistry from UCLA.

Camilo Velez is a postdoctoral researcher in microrobotics at Carnegie Mellon University. He had a postdoctoral appointment at University of

Florida (UF) to fabricate magnetic materials for high frequency/5G communication devices. Ph.D. in electrical and computer engineering at UF in micro fabrication of magnetic materials. M.Sc. at UF, focused on microfabrication and reliability of III-V semiconductor devices. M.Eng. at Universidad de los Andes in microsystems and B.S. in Electronics Engineering at Pontificia Universidad Javeriana-Colombia. Skilled, handson and creative researcher with experimental experience in microsystems, MEMS (microelectromechanical systems), magnetic materials, biomedical devices, and electronics in engineering. With 9 years of experience in research and 2 years in industry, he has contributed to 19 journals and peer review publications, filled 2 international patents, and participate in more than 21 conferences. He is the global Young Professionals EDS committee chair, leading the social media initiative to empower Young Professionals in our society.

I welcome all electees and urge them to get fully engaged in the affairs of the Electron Devices Society. EDS is considered to be a volunteerled volunteer-driven organization and we expect nothing less from all to continue this tradition.

> Samar Saha EDS Nominations and Elections Chair University of California Riverside, CA, USA

#### AWARDS & RECOGNITION

## CONGRATULATIONS TO EDS MEMBER, JAGADISH CHENNUPATI—ONE OF EIGHT SCIENTISTS PRESENTED WITH A UNESCO MEDAL

Jagadish Chennupati, Nassiopoulou Androula Galiouna and Esko Ilmari Kauppinen were among the 10 eminent scientists who received the 8th UNESCO Medals for contributions to the development of nanoscience and nanotechnologies. © UNESCO/Jake Lewis

#### Eighth UNESCO Medals for Contributions to the Development of Nanoscience and Nanotechnologies

On 22 November 2018, ten eminent scientists and scientific institutions received the UNESCO Medals for contributions to the development of nanoscience and nanotechnologies during a ceremony held at UNESCO head-quarters, Paris. The medal is awarded each year by the Director-General of UNESCO to prominent scientists, public figures and organizations that contributed to the development of nanoscience and nanotechnologies in the spirit of UNESCO's priorities.

The fields of nanoscience and nanotechnology have been developing for just a few decades, but they now contribute to the economy of all countries and almost every human life. "Today, we meet to celebrate exceptional scientists and practitioners from around the world, who are pushing back the frontiers of scientific knowledge of what lies beyond

our world and to transform our lives for the benefit of all", said Miguel Clusener-Godt, Director of UNES-CO's Division of Ecological and Earth Sciences. "They impact electronics and computing, medicine, materials and manufacturing, energy and transportation... Nanoscience and nanotechnology have the potential to foster new developments in science, technology and innovation via the dissemination of new knowledge and applications."

This is why the Medal was established in 2010 at the initiative of the International Commission responsible for developing the Nanoscience and Nanotechnologies theme for the Encyclopedia of Life Support Systems (EOLSS). Since then, 46 Medals have been awarded to prominent scientists, institutions and public figures, such Isamu Akasaki, winner of the 2014 Nobel Prize in Physics, Zhores Alferov, winner of the Nobel Prize in Physics in 2000, and Chunli Bai, President of the Chinese Academy of Sciences.

The 2018 UNESCO Medals for contributions to the development of nanoscience and nanotechnologies were awarded to:

#### Sergeev Alexander Mikhaylovich-Russian Federation

President of the Russian Academy of Sciences, Deputy Chairman of Russian Presidential Council for science and education.

His expertise in plasma physics, nonlinear dynamics of optical systems and highly sensitive optical measurements are internationally recognized. He has made important contributions to the fields of optical tomography of bio-tissues, and for created of the most powerful laser that can generate impulses with peak power of hundreds petawatts.

#### Tatartchenko Vitali Antonovitch-France

Consultant at the Aix-Marseille University in France, Vice-Chairman of COSPAR (International Committee of Space Research).

He provided the theoretical basis of PeTa effects (Perelman-Tatartchenko effect)—the physical phenomenon of characteristic radiation accompanying first order phase transitions—and demonstrated its existence experimentally. On the basis of the PeTa effect he developed a new conception of cavity-less lasers and models for cavitation luminescence, sonoluminescence and laser induced bubble luminescence.

#### Fursenko Andrei Aleksandrovich-Russian Federation

President of the Supervisory Board of the Russian Scientific Foundation, Assistant of the President of the Russian Federation, Chairman of the Academic Council of the Foundation "Centre for Strategic Research North-West".

He directed the development of the national programme "Development of nanotechnologies in Russia" as Minister of Education and Science of the Russian Federation. He is the author of over 100 scientific publications, notably on technological innovation.

#### Ismail Elnaggar Mohammed-**Egypt and United States of America**

Founding Director of the Khalifa Semiconductor Research Center in the United Arab Emirates.

His many achievements include the development of a self-powered wearable device that can predict the onset of a heart attack ahead of time.

#### Kauppinen Esko Ilmari – Finland

Manager of the NanoMaterials Group at the Department of Applied Physics of the Aalto University School of Science.

His research focuses in gas phase synthesis of nanomaterials, including carbon nanotubes and polymer-drug composite nanoparticles and their characterization with advanced electron microscopy methods. These fields create new opportunities for drug delivery, inhaled at the micro and nano scales, which are very promising to treat diabetes and many other diseases.

#### Nassiopoulou Androula Galiouna - Greece

Director of Research and Head of the "Nanostructures for Nanoelectronics, Photonics and Sensors" research group at the National Centre for Scientific Research Demokritos in Athens, President of the General Assembly of the European Institute of Nanoelectronics.

She pioneered the fabrication of vertical silicon nanowires on the Si wafer and developed innovative applications of Si nanowires, nanocrystals and porous Si, which include low-loss transmission lines and antennas on the Si wafer working up to 210 GHz, thus enabling fast communication on the Si chip, nanocrystal memories, high capacitance density microcapacitors for energy storage, high performance miniaturized Si thermal sensors applied in a respiration system and a flow meter for gas engine etc.

When receiving her medal, she stressed the importance of caution when dealing with nanostructures, since their properties are not yet fully known and of aiming for societal benefits in all research. Through miniaturization, Microelectronics made devices faster and cheaper and revolutionized computing and communication systems. This has been now expanded to the general field of Nanotechnology, fostering applications in all fields of life, including new medical applications, new drugs and drug delivery systems, she explained. "Safety issues should thus be always one of the main priorities to be studied, discovered and applied.

(...) Finally, as scientists we should stay committed and engaged that Nanoscience and Nanotechnology and its innovative applications stay within the spirit of Unesco for sustainable development for all, against poverty and for a peaceful world, for the profit of all societies."

#### Zehetbauer Michael Josef -**Austria**

Head of the Faculty Group "Physics of Nanostructured Materials" at the University of Vienna.

He has been working on increasing the efficiency of functional materials such as nanostructured thermoelectrics, hydrogen storage materials, and biodegradable implant materials.

#### Jagadish Chennupati – Australia

Head of the Semiconductor Optoelectronics and Nanotechnology Group of the Australian National University; Convenor of the Australian Nanotechnology Network.

He has made important contributions in the field of semiconductor nanotechnology, and established a pioneering research programme in Australia in semiconductor nanotechnology and optoelectronics.

#### Mansurov Zulkhair - Kazakhstan

Director-General of the Institute of Combustion Problems, Doctor of Science, Professor.

He has made important contributions in the production of nanocarbon materials and carbon nanotubes and graphene. His research focuses on hydrocarbon combustion kinetics and mechanisms, the structure of cold and sooting flames, and investigation the functions of nanocarbon materials.

#### Chekhonin Vladimir Pavlovich-**Russian Federation**

Vice President of the Russian Academy of Sciences. Founder and Head of the Department of Medical Nanobiotechnologies of the Russian National Research Medical University.

His fields of research include development of nanotechnological visualization systems and the targeted delivery of therapeutic agents and genetic material to target cells, and investigation of nanotechnological approaches to genodiagnostics and bioprotection in socially significant diseases. This includes the targeted delivery of diagnostic compounds to cancer cells, which can bring us closer to better understanding and treating oncological diseases.

Article reprinted with permission by **UNESCO**

## IEEE ROBERT BOSCH MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD

## Robert Bosch (1861-1942) Inventor, Entrepreneur, Founder of Robert Bosch GmbH

The Robert Bosch Micro and Nano Electro Mechanical Systems Award was established by the IEEE Electron Devices Society in 2014 to recognize and honor advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices. The contributions to be honored by this award should be innovative and useful for practical applications.

This award is sponsored by the IEEE Electron Devices Society with financial support from Robert Bosch LLC. It is intended that the award will be presented annually to an individual or to as many as three individuals whose achievements and contributions are judged to meet the selection criteria for the award. The award will be presented at an IEEE conference of the winner's choice. It is not necessary for the recipient(s) to be a member(s) of IEEE.

The recipient will receive a US\$10,000 honorarium, travel expenses to attend the award presentation, a bronze medal, and a certificate. In the event that more than one awardee is selected, the cash honorarium will be equally divided among the recipients. Each recipient will receive a bronze medal and a certificate.

Please visit the EDS website for more information on this award: <a href="http://eds.ieee.org/robert-bosch-micro-and-nano-electro-mechanical-systems-award.html">http://eds.ieee.org/robert-bosch-micro-and-nano-electro-mechanical-systems-award.html</a>.

Nominations for this award should be made using our <u>online nomination form</u> and submitted before midnight (EST) on October 2. Letters of recommendation must be sent directly to l.riello@ieee.org according to the same schedule.

#### 2019 IEEE EDS ROBERT BOSCH MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD WINNER

The 2019 IEEE EDS Robert Bosch Micro and Nano Electro Mechanical Systems Award was presented to Hiroyuki Fujita, Advanced Research Lab of Canon Medical Systems Corp., Japan, at the 2019 IEEE MEMS Conference, Korea, January 2019. This prestigious award recognizes and honors advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices.

Hiroyuki Fujita is Director of Advanced Research Laboratory of Cannon Medical Systems Corporation from 2017. He is also a Professor of Tokyo City University and Professor Emeritus of The University of Tokyo, where he served as a Professor of Institute of Industrial Science of the University over 38 years. He was a visiting professor in MIT and UC Berkeley. He received the B.S., M.S. and Ph.D. degrees in Electrical Engineering from The University of Tokyo in 1975, 1977 and 1980, respectively. He is currently engaged in the

Hiroyuki Fujita

For pioneering contributions in microactuators, optical-MEMS, and bio-nano-MEMS and strong leadership in the science of MEMS

investigation of MEMS/NEMS and applications to bio/nano technology and IoT. Major research projects include MEMS-in-TEM experiment for simultaneous visualization and measurement of nanomaterials, vibrational energy harvesters using ionic liquids, and bio molecular/cellular characterization using MEMS tools. He has published more than 300 academic papers. He received many awards including l'Ordre des Palmes

Academiques from Government of France, Docteur Honoris Causa from Ecole Normale Supērieure de Cachan, The Prize for Science and Technology -Research Category from Ministry of Education, Culture, Sports, Science and Technology and Outstanding Achievement Award from The Institute of Electrical Engineers of Japan.

> Kurt Petersen 2019 EDS Bosch Award Chair

#### 2018 EDS DISTINGUISHED SERVICE AWARD

Dr. Shuji Ikeda

The IEEE Electron Devices Society (EDS) is extremely proud of the services that it provides to its members. Its members generate the premier new developments in the field of electron devices and share these results with their peers and the worldat-large by publishing their papers in EDS journals and presenting results in its meetings. This is a global activity that is effective because of the efforts of numerous volunteers. Many of these volunteers labor in relative obscurity, with their only reward being the satisfaction that they receive

in being an important part of a successful organization, namely of the IEEE Electron Devices Society. One means of thanking these volunteers is to recognize their contributions through the EDS Distinguished Service Award.

The recipient of the 2018 EDS Distinguished Service Award was Dr. Shuji Ikeda, Tei Solutions Co. Ltd., Tsukuba, Japan, and the award presentation took place at the International Electron Devices Meeting (IEDM) in San Francisco, on December 3, 2018.

Shuji Ikeda received the B.S. degree in Physics from the Tokyo Institute of Technology, Japan in 1978, M.S. degree in Electrical Engineering from the Princeton University, USA in 1987, and PhD degree. in Electrical Engineering from the Tokyo Institute of Technology, Japan in 2003. He joined the Semiconductor Division, Hitachi Itd., Tokyo, Japan in 1978, where he was engaged in research and development of the state-of-the-art SRAM processes and devices. He was also working on developing process technology for LOGIC, embedded DRAM, embedded Flash memories, and CMOS power RF devices as well as transfer of technology to mass production line. In April 2005, he joined the SEMATECH/ATDF at Austin, Texas, as the Director of Technology, where he developed different types of technologies including scaled CMOS, non-classical CMOS, new materials and tools. In 2008, he established tei Technology, LLC at Austin, where he creates new business models and

provides total (business/technology) solutions to the customers. He also founded tei Solutions Inc., R&D foundry, in Tsukuba, Ibaraki, Japan in 2010. His main focus is integrating emerging technology onto semiconductor manufacturing technology to create innovative products, including bio sensors, DNA sequencers, and various kinds of IoE (Internet of Everything) devices. He received several awards for his unique business model, Joyo Bank Manufacturing Award, 2013, and Tokyo Institute of Technology Venture Business Award, 2014. Shuji is a fellow of IEEE.

Shuji Ikeda's services to IEEE EDS are noteworthy and lasting. One of the important roles of his career in IEEE EDS is serving as the General Chair of IEDM 2002. As the first General Chair from Asia, he boosted Asian contributions to the IEDM and focused on manufacturing technology. His other major service to EDS is the launching of the EDTM (Electron Devices Technology and Manufacturing) conference in 2017. The EDTM was planned to focus on

manufacturing, especially in Asia. As a chairman of the Ad Hoc Committee on Asian Flagship Conference, and VLSI Technology and Circuits Technical Committee, Shuji discussed with committee members, other EDS colleagues, and EDS executives once a week over the phone and face to face for three (3) years. Through the EDTM, we could try anything good to enhance EDS activities, that are quite different from other conferences. Thanks to the leadership from EDS executives, Shuji started the EDTM with great success in 2017 at Toyama, Japan. And, EDTM continues, the 3rd EDTM 2019 was held during March 13-16 in Singapore.

He and his wife, Hiroko, were classmates at Kunitachi High School, Tokyo. They are proud parents of Yuki, Ayano both are teachers for handicapped students and Sho, SDF personnel. All of them are not engineers, though.

Samar Saha EDS Awards Chair Milpitas, CA

#### 2018 IEEE EDS J.J. EBERS AWARD WINNER

Dr. Michael Shur

The 2018 J.J. Ebers Award, the prestigious Electron Devices Society award for outstanding technical contributions to electron devices, was presented to Dr. Michael Shur of Rensselaer Polytechnic Institute, Troy, NY, at the International Electron Devices Meeting in San Francisco, on December 3, 2018. This award recognizes Dr. Shur's "For pioneering the concept of ballistic transport in nanoscale semiconductor devices".

Dr. Michael S. Shur received MSEE Degree (with honors) from St. Petersburg Electrotechnical Institute (LETI) and PhD. and Dr. Sc. Degrees from A. F. loffe Institute. He was awarded Honorary Doctorates by St. Petersburg State Technical University and University of Vilnius. He is Patricia and Sheldon Roberts Professor of Solid State Electronics and Professor of Physics, Applied Physics, and Astronomy at Rensselaer Polytechnic

Institute. Dr. Shur is co-founder, President and CEO of Electronics of the Future, Inc. and a co-founder of Sensor Electronics Technology, Inc. Dr. Shur is Life Fellow of IEEE, APS, ECS, and SPIE, Fellow of the National Academy of Inventors and several other professional societies. He is Distinguished Lecturer of IEEE EDS and IEEE Sensors Council. His awards include IEEE Research and Teaching Awards, ECS Electronic and Photonics Award, Tibbetts Award for Technology Commercialization, RPI Faculty Awards, Senior Humboldt Research Award, and Best Paper Awards. Dr. Shur was listed by the Institute of Scientific Information as Highly Cited Researcher. His h-index is 108. In 2009, he was elected Foreign Member of the Lithuanian Academy of Sciences. His work has ranged from the new concept of the ballistic transport in nanostructures and plasmonic devices to the development and commercialization of deep UV LEDs and novel color rendition engines based on the statistical color figures of merit.

He and his wife, Paulina, were born, met and married in the Soviet Union. They came to the United States as refugees in 1976, when Michael joined Professor Lester Eastman's group at Cornell. Paulina had a Russian Ph. D. in theatre and film. She went back to school and received MFA degree in theatre directing from the University of Virginia. After graduation, she became Founder and Artistic Director of the Magic Mirror Theatre in Charlottesville, VA. Her best production was an opera based on her own libretto "The Age When Women Lived and Died for Love." Then she joined the RPI Electronics Arts Department as a faculty member. Paulina and Michael have two daughters-Luba (a lawyer who also graduated from the University of Virginia) and Natasha (a medical doctor who got her MD from the Albert Einstein School of Medicine).

Joachim N. Burghartz 2018 EDS J.J. Ebers Award Chair Institute for Microelectronics Stuttgart Stuttgart, Germany

Support the IEEE Electron Devices Mission Fund of the IEEE Foundation.

**IEEE** Foundation

Learn More at http://bit.ly/IEEE-EDS-MissionFund

# IEEE ELECTRON DEVICES SOCIETY J.J. EBERS AWARD

#### **Nominate:**

J.J. Ebers Award on-line nomination form: http://bit.ly/2THINQF

**Submission Deadline:** July 1, 2019

#### Contact:

If you have any questions regarding the EDS J.J. Ebers Award, please contact Laura Riello of the EDS Executive Office at l.riello@ieee.org

#### Visit:

http://eds.ieee.org/jjebers-award.html

#### **CALL FOR NOMINATIONS**

The IEEE Electron Devices Society invites the submission of nominations for the 2019 J.J. Ebers Award. This award is presented annually by EDS to honor an individual(s) who has made either a single or a series of contributions of recognized scientific, economic, or social significance to the broad field of electron devices. The recipient(s) is awarded a plaque and a check for \$5,000, presented at the IEEE International Electron Devices Meeting (IEDM).

#### 2018 EDS EDUCATION AWARD WINNER

Dr. Muhammad Ashraful Alam and Dr. Fernando Guarin, EDS President

The EDS Education Award recognizes an IEEE/EDS Member from an academic, industrial, or government organization with distinguished contributions to education within the fields of interest of the IEEE Electron Devices Society. Dr. Muhammad Ashraful Alam was recognized at the International Electron Devices Meeting in San Francisco, CA December 3, 2018 as the 2018 EDS Education Award winner. The award cites Dr. Alam "For educating, inspiring and mentoring students and electron device professionals around the world".

Dr. Muhammad Ashraful Alam is the Jai N. Gupta Chair Professor of Electrical Engineering at Purdue University where his research and teaching focus on physics, fundamental limits, and technology of classical and emerging semiconductor devices. He received the BSEE degree from Bangladesh University of Engineering and Technology in 1988, MSEE degree from Clarkson University in 1991, and a Ph.D. degree from Purdue University in 1994.

From 1995 to 2001, he was with Bell Laboratories, Murray Hill, NJ, where he made fundamental contributions to laser dynamics, the design of optoelectronic integrated circuits, and the reliability ultra-thin gate dielectrics. From 2001-2003, he headed the IC Reliability Group at Agere Systems. Since joining Purdue in 2004, Dr. Alam has published over 350 papers on a broad range of More-Moore and More-than-Moore technologies related to self-heating in nanoscale and power transistors, sensitivity limits of biosensors, percolative transport in flexible electronics, atom-to-farm modeling of solar cells.

For his contributions, he has been elected a fellow of IEEE, American Physical Society, and the American Association for the Advancement of Science. He is also the recipient of the 2006 IEEE Kiyo Tomiyasu Award for contributions to device technology for communication systems, and 2015 SRC Technical Excellence Award for contributions to semiconductor reliability physics.

Prof. Alam views research and teaching as two sides of a coin because teaching forces one to understand a concept deeply so that it can be explained simply. The simple explanations connect the concepts in unexpected ways suggesting new ideas of creative research. With this perspective, Prof Alam has made important contributions to graduate and undergraduate education: More than 350,000 students worldwide have learned some aspect of semiconductor devices from his web-enabled courses. For additional details, see the "Teaching" and "Blogs" sections of his website: https://sites.google.com/ view/alam-research-group/home

> Durga Misra 2018 EDS Education Award Chair **NJIT** Newark, NJ

## 2019 EDS EDUCATION AWARD CALL FOR NOMINATIONS