APRIL 2022 VOL. 29, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI

#### TABLE OF CONTENTS

| 75TH ANNIVERSARY OF THE TRANSISTOR                  |  |  |  |  |  |

|-----------------------------------------------------|--|--|--|--|--|

| TECHNICAL BRIEFS                                    |  |  |  |  |  |

| UPCOMING TECHNICAL MEETINGS                         |  |  |  |  |  |

| SOCIETY NEWS                                        |  |  |  |  |  |

| AWARDS AND CALLS FOR NOMINATIONS                    |  |  |  |  |  |

| • Murphy's Laws and Their Importance in Engineering |  |  |  |  |  |

| EDS YOUNG PROFESSIONALS                             |  |  |  |  |  |

| EDS HUMANITARIAN PROJECTS                           |  |  |  |  |  |

| CHAPTER NEWS                                        |  |  |  |  |  |

| REGIONAL NEWS43                                     |  |  |  |  |  |

| EDS MEETINGS CALENDAR63                             |  |  |  |  |  |

| IEEE T-ED CALL FOR PAPERS FOR TWO SPECIAL ISSUES 66 |  |  |  |  |  |

| FDS MISSION VISION AND FIFI D OF INTEREST 68        |  |  |  |  |  |

Photo Courtesy: Bell Labs '47

The year 1905 is well known as the "Miracle Year" because Albert Einstein published four papers that changed the laws of physics and were significant contributions to the foundation of modern physics. Similarly, November 1947-January 1948 were the three magical months that paved the way for modern-day electronics. This was done by three brilliant scientists who were members of the Mervin Kelly's Solid State Physics Group and Semiconductor Sub-Group at Bell Labs, which were given the challenging task of creating a solid-state semiconductor switch that could replace the vacuum tube. The famous physicists-Walter Brattain and John Bardeen managed to make the first working transistor, now known as the point-contact transistor. The invention was made on December 16, 1947. A week after that, the device was officially demonstrated to Bell Labs executives as a "magnificent Christmas present." In January 1948, William Shockley demonstrated the junction transistor. All three received The Nobel Prize in Physics (1956) and as per Nobel Prize Committee—"In 1947 John Bardeen and Walter Brattain produced a semiconductor amplifier, which was further developed by William Shockley. The component was named a "transistor"."

The Electron Devices Society has decided to celebrate the year 2022–2023 as the 75th Anniversary of the Transistor. As the history of this invention and of its consequences is much more involved and interesting, it is imperative that the leading EDS Luminaries share the scientific & technological developments which took place in the last 75 years, with the current generation of researchers. Popularizing talks at Conferences and Mini-Colloquia, Technical Articles in the EDS Newsletter, Webinar Series shall be a part of the

#### **ELECTRON DEVICES** SOCIETY

#### President

Ravi Todi Western Digital Technologies

Email: rtodi@ieee.org

#### President-Flect

Rin 7hao

Freescale Semiconductor Email: bin.zhao@ieee.org

#### Treasurer

Roger Booth Qualcomm

Email: boothrog@yahoo.com

#### Secretary

M.K. Radhakrishnan NanoRel

Email: radhakrishnan@ieee.org

#### Sr. Past President

Fernando Guarin GlobalFoundries

Email: fernando.guarin@ieee.org

#### Vice President of Education

Navakanta Bhat

Indian Institute of Science Email: navakant@gmail.com

#### Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

#### Vice President of Membership and Services

Merlyne de Souza University of Sheffield

Email: m.desouza@sheffield.ac.uk

#### Vice President of Publications and Products

Arokia Nathan

University of Cambridge Email: an299@cam.ac.uk

#### Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

#### Vice President of Strategic Directions

Doug P. Verret IEEE Fellow

Email: dougverret@gmail.com

#### Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html

#### EDS Board of Governors (BoG) **Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2022                                                                                                                                              | TERM                            | 2023                                                                                                                            | TERM                                          | 2024                                                                                                                       | TERM                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Constantin Buluce<br>Daniel Mauricio<br>Camacho Montejo<br>John Dallesasse<br>Mario Lanza<br>Geok Ing Ng<br>Claudio Paoloni<br>Hitoshi Wakabayasi | (2)<br>(2)<br>(2)<br>(2)<br>(2) | Roger Booth<br>Xiaojun Guo<br>Edmundo A.<br>Gutierrez-D.<br>Francesca lacopi<br>Benjamin Iniguez<br>Manoj Saxena<br>Sumant Sood | (2)<br>(1)<br>(2)<br>(1)<br>(2)<br>(2)<br>(2) | Mario Aleman<br>Paul Berger<br>Yogesh Singh Chauhar<br>Patrick Fay<br>Kazunari Ishimaru<br>Bill Nehrer<br>Merlyne de Souza | (1)<br>(2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(2) |

#### NEWSLETTER **EDITORIAL STAFF**

#### **Editor-In-Chief**

Daniel Tomaszewski

Institute of Microelectronics and Photonics Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### Associate Editor-in-Chief

Manoj Saxena

Deen Dayal Upadhyaya College

University of Delhi Email: msaxena@ieee.org

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1, 2 & 3)

Rinus Lee

TEL Technology Center, America Email: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University

Email: mmadachi@sfu.ca

#### Latin America North (Region 9)

Joel Molina Reves

INAOE

Email: jmolina@inaoep.mx

#### Latin America South (Region 9)

Paula Ghedini Der Agopian UNESP, Sao Paulo State University Email: paula.agopian@unesp.br

#### **REGION 8**

#### Scandinavia & Central Europe

Marcin Janicki

Lodz University of Technology Email: janicki@dmcs.pl

#### United Kingdom, Middle East & Africa

Stewart Smith

Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

#### Western Europe

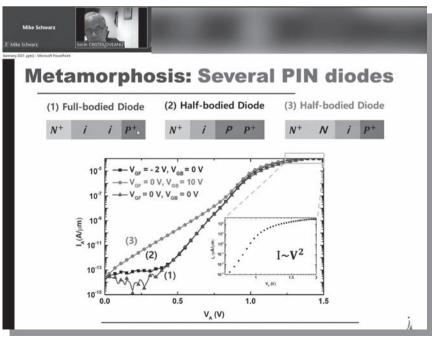

Mike Schwarz Mittelhessen University of Applied Sciences Email: mike.schwarz1980@ googlemail.com

#### REGION 10

#### Australia, New Zealand & South East Asia

Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University

Email: thhou@mail.nctu.edu.tw

#### South Asia

Soumya Pandit University of Calcutta

Email: soumya\_pandit@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission

#### NEWSLETTER DEADLINES

**DUE DATE I**SSUE October July 1st October 1st January April January 1st Jüly April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2022 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

# 5TH ANNIVERSARY THE TRANSISTOR

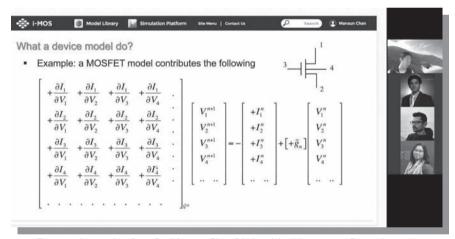

# Invention of the Transistor 75 Years Ago; The Origin of Device Miniaturization Towards Super-Intelligent Society

HIROSHI IWAI

#### 1. Before the Transistor

In the middle of the 19th century, electrical engineering provided us with a big technological leap, i.e., instantaneous long-distance transportation of 'energy' and 'information' through electric wires. The 'information transportation' was conducted at the end of the 1830's by the electric telegraph with 'relays' used as the amplifier of the decaying signal (Morse code) propagating on a long wire [1]. The relay was the first electric device which amplified electric signal, but it had a function of only digital signal amplification by the mechanical switch controlled by the signal current flowing in the electromagnet coil.

Then, 60 years later, wireless telecommunication started with a strong demand for the analog signal amplification. The analog signal amplification was realized by the invention of the 'triode vacuum tube' in 1906 [2]. The electron current in a vacuum tube between the cathode and anode was directly modulated by the potential of the 'grid electrode' inserted in the electron current flow. The analog signal imposed on the grid bias was transferred into the electron current and amplified. The grid bias can also switch on/off the electron current. The triode vacuum tubes had been widely used for telecommunication and machine control since then. This was the beginning of 'electronics' that enabled the manipulation of electron movement in the devices for many applications.

#### 2. The Road to the Transistor

However, the vacuum tubes were not suitable for low power-consumption operation and also for very highfrequency operation at microwave range due to the difficulty of the size reduction. It would be quite natural to imagine that replacing the vacuum tubes by solid-state amplifiers could solve the above problems. The idea was to modulate the lateral current in a solid-state material by the vertical electric field applied by the 3rd terminal, i.e., 'grid' or 'gate'. This is the analogy to the triode vacuum tubes and the idea of the 'Field Effect Transistor (FET), although the term 'transistor' did not exist at that time. However, different from the case of electron current in the vacuum, controlling the electron current in solid-state materials by the vertical electric field was not easy because of the high-density charges of electrons and ions existing in the solid-state materials. Thus, it was assumed to be necessary to use an 'extremely-thin semiconductor film' as the solid-state material. The first recorded ideas of the FET were filed as patents without any experimental data in 1925 for MESFETs [3] and 1928 for MOSFETs [4]. Although semiconductors had been already

[5]-[7] from the beginning of the 20th century, the physics of semiconductors such as band theory [8] using quantum mechanics was not known at all until the 1930's. At that time, there were even no concepts of holes and p-n junctions, and the quality of the semiconductor materials was not sufficient at all [9]. Later in 1945-1948, W. Shockley of BellTelephone Laboratories thought of an idea of MOSFETs [9]-[12] independently from the previous MOSFET ideas. His idea was to modulate the carrier density at the semiconductor surface by the band bending caused by the vertical electric field from the gate electrode. He predicted the amount of the carrier density modulation based on the calculation using the band theory. However, the experimental carrier density modulations on Si, Ge and Cu<sub>2</sub>O were 3-4 magnitudes of order smaller than those of the theoretical calculations [9]-[12] because of the existence of the fixed electrons trapped at the surface states [13]. (The accumulation layer conduction with the majority carriers of the MOSFET is shown in W. Shockley's works [10], but the inversion layer conduction with the minority carriers was not recognized by his works [10], [12]. The inversion type of the conduction was found by J. Bardeen in 1947 [14] and the inversion layer conduction used in today's MOSFETs was clearly described later by L. Brown's paper [15] published in 1953). W. Shockley's group continued the research for preventing the trapped surface charge effect, and

used for commercial crystal rectifiers

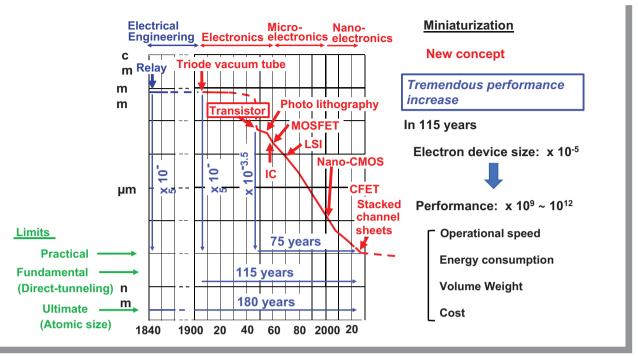

Trend of minimum line width used for devices and performance increase

fortunately, J. Bardeen and W. Brattain found, on December 16, 1947, current amplification phenomena when they put the 2 gold point-contact electrodes (emitter and collector electrodes)—with the separation of 50 µm-directly onto the n-type Ge surface [9]-[11], [16], [17]. The Ge substrate was connected to the base electrode from the backside. The injection of holes from the emitter electrode under the positive bias condition modulated the potential of Ge near the collector electrode and enhanced the electron current between the base and collector electrodes. This was the first solid-state amplifier and named 'transistor' as a contraction of 'trans-resistance'. The amplification mechanism was different from that of FET, and this transistor is later called 'point-contact bipolar transistor' because both majority and minority carriers contribute the amplification.

# 3. The Transistor as the Origin of the Device Miniaturization and the World After the Transistor Invention

The point-contact bipolar transistor had soon evolved to the junction

bipolar transistors (BJT's) [9], [11], [18] in 1948 in order to prevent the mechanical instability of the contact. Monolithic integrated circuits started using BJT's in 1958 [19] and 59 [20]. In 1960, the first MOSFET was realized by choosing thermally-grown oxide on Si as the gate oxide [21] in order to significantly decrease the surface trapped charge density. MOSFETs replaced the BJTs in Large Scale Integrated circuits (LSI's) by the end of 1960's because of the ease of their integration due to the planar structure.

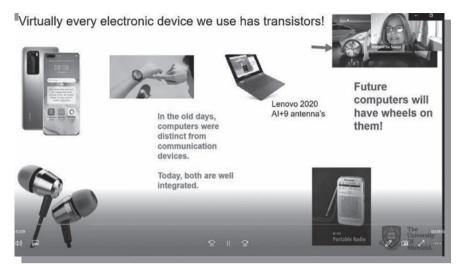

Now, the minimum line width used for nano-CMOS VLSI is about 15 nm. The minimum line width has decreased about 105 times since the first vacuum triode in the past 115 years, and 103.5 times since the first transistor in the past 75 years, respectively, as shown in the figure. Because of the size decrease, the performance—such as operational speed, energy/power consumption, volume, weight, and cost of electric systems/machines improved billions-trillions of times. The invention of the transistor 75 years ago was the origin of electron device

miniaturization, and it was a great technological leap for the progress of intelligent society. Miniaturization of the electron devices towards micro-/nanoelectronics was an extremely important concept. Without the tremendous miniaturization of the transistors in the past 75 years, today's intelligent society with the internet, and Al would not exist.

#### 4. Future of the Transistor

According to IEEE IRDS (International Roadmap for Devices and Systems) 2021, '3 nm' logic CMOS technology will start production this year (2022), and we can still expect the merit in size, operational-speed and powerconsumption. It should be noted that the 'logic technology names' such as '5 nm' or '3 nm' are just 'inflated names' and have nothing to do with the real physical size used in the devices. Indeed, it is a bad custom of the logic CMOS industry. Real minimum line width such as the gate length is about 15 nm for the '3 nm technology' according to the IRDS 2021. At this moment, the downsizing limit of the minimum line width-such as the

gate length and metal wire width-is thought to be about 10 nm because of the significant increase in leakage current of MOSFETs and resistance increase and reliability degradation of interconnects. So, the scheme of device miniaturization, having continued since the invention of the transistor, could reach the limit in several years. Even if we could solve those problems by the introduction of new materials/ technologies, it should be noted that 3 nm is the 'fundamental limit' caused by the direct-tunneling leakage current, and that 0.3 nm is the 'ultimate limit' due to the atomic size. Thus, there will be no 'pico-technology' after 'nano-technology', and the end of the device miniaturization is not so far.

However, the progress of the integrated circuits with Moore Law will continue by the 3D integration. In IEDM 2020 and 2021, there were many publications of 3D MOSFETs such as CFETs (Stacked nano-sheet channel n- and p-MOSFETs) [22]. The progress of the 3D integration will reach a limit in 10-20 years because of the increasing heat density and cost increase. However, demands for high-performance semiconductor devices with low-power consumption will keep increasing in the future super-intelligent society, and the technology optimization of the devices for each specific application will continue after that. Future intelligent society will create many new business fields such as 6G communication or autonomous driving, which will require new functions and performances. We will have so many things to do for future logic, memory, telecommunication, power, and sensor devices to optimize for the new businesses.

In the long term, the next leap of technology will be the introduction of bio systems. This does not necessarily mean to introduce the algorism of the bio system on semiconductor devices, but also means to use existing bio systems, and the cooperation between the electronics and bio systems becomes important. Even though the champion player of the 'Go' game cannot win the Al player because the human brain cannot keep concentration only for one thing for long hours without rest and cannot memorize and remember huge volume of data accurately, bio systems such as brains composed by neurons are much efficient than the semiconductor Al system in most of the cases.

Dr. Hiroshi Iwai is a semiconductor device engineer who contributed to the development of LSI technologies at Toshiba, Tokyo Institute of Tech-

nology, and NYCU for almost half a century since 1973. He was the IEEE EDS President (2004–2005) and the IEEE Division I Director (2010–11). He is an IEEE Life Fellow, an IEEE EDS Eminent Lecturer and an IEEE IRDS committee member.

#### References

[1] S. F. B. Morse, US Patent 1647, filed April 7, 1838.

[2] L. de Forest, US Patent 879,532 filed January 29, 1907.

[3] J. E. Lilienfeld, US Patent 1,745,175, filed October 8, 1926. (Priority October 22, 1925).

[4] J. E. Lilienfeld, US Patent 1,900,018, filed March 28, 1928.

[5] J. C. Bose, US Patent 755,840, Filed September 30, 1901.

[6] H. H. C. Dunwoody, " U S Patent 837,616, filed March 23, 1906.

[7] G. W. Pickard, US Patent 836,531, filed August 30, 1906.

[8] A. H. Wilson, Proc. Royal Soc. vol. A133, p. 458, 1931.

[9] F. Seitz and N. G. Einspruch, "Electronic Genie: The Tangled History of Silicon," University of Illinoi Press, 1998.

[10] W. Shockley, IEEETrans. on ED, vol. 23, p. 597, 1976.

[11] M. Riordan and L. Hoddeson, "Crystal Fire: The Invention of the Transistor and the Birth of the Information Age," W. W. Norton & Company, 1997.

[12] W. Shockley et al., Phys. Rev., vol.74. p. 232, 1948.

[13] J. Bardeen, Phys. Rev., vol. 71. p. 717, 1947.

[14] L. Hoddeson, Historical Studies in Physical Sciences, vol.12, p.41, 1981.

[15] L. W. Brown, Phys. Rev., vol. 91. p. 518, 1953.

[16] J. Bardeen *et al.*, Phys. Rev., vol.74. p. 230, 1948.

[17] J. Bardeen et al., US Patent 2,524,035, filed June 17, 1948.

[18] W. Shockley, US Patent 2,569,347, filed June 26, 1948.

[19] J. S. Kilby, US Patent 3,138,743, filed February 6, 1959.

[20] R. N. Noyce, US Patent 2,981,877, Filed July 30, 1959.

[21] D. Kahng, US Patent 3,102,230, filed May 31, 1960.

[22] L. Liebmann, et al., IEDM, pp. 51, 2021.

(continued from page 1)

various activities undertaken by the "75th Anniversary of the Transistor Adhoc Committee" with an aim to provide technical information and education to enlighten EDS members. This shall be a mark of tribute

to the men and women who have contributed to the Transistor Story—Discovery, Development, and Applications which has had a lasting impact on people's lives and has benefited mankind where it serves

good in social relations, caring for the Earth, science, technology, engineering, and economy.

Manoj Saxena 75th Anniversary of the Transistor Adhoc Committee Chair

# TECHNICAL BRIEFS

### SUPERCONDUCTOR ELECTRONIC DEVICE TECHNOLOGY ROADMAPPING WITHIN THE IRDS

D. SCOTT HOLMES

IEEE IRDS CRYOGENIC ELECTRONICS AND QUANTUM INFORMATION PROCESSING (CEQIP) CHAIR

D. SCOTT, HOLMES@IEEE.ORG

Abstract—For superconductor electronics to meet the needs expected for applications such as quantum computing or large-scale digital computing, significant improvements will be required, especially in circuit density and complexity. Key to improvement are innovations in superconductor devices and logic families. Technology roadmaps are under development to provide goals and timelines.

**Index Terms**—superconductor electronics, superconductor devices, technology roadmapping, Josephson junctions

#### I. Introduction

Scaling of CMOS electronics has driven a broad spectrum of applications through increased performance and complexity. The International Roadmap for Devices and Systems (IRDS), which succeeded the International Technology Roadmap for Semiconductors (ITRS) in 2017, does not limit its scope to semiconductor devices. The roadmap drivers now focus on application requirements and include a broader range of nonsemiconductor technologies. Within the ITRS, the Cryogenic Electronics and Quantum Information Processing (CEQIP) International Focus Team has published reports since 2018. Superconductor electronics (SCE) is one of three areas specifically covered by the CEQIP team.

Applications of superconductor electronics such as large-scale digital computing could provide benefits

such as higher clock frequencies, faster data movement, and lower energy per computation. Neuromorphic computing for large-scale artificial intelligence applications needs energy-efficient solutions and might be a natural fit for superconductor circuits that naturally use pulse-based logic. Quantum computing using superconducting circuits requires operation at temperatures around 10 mK where the energy loss in semiconductor control and interface circuits seems prohibitive at full scale.

However, considering that the largest superconductor computing system built to date has just over one million switching elements, such large-scale applications will require significant increases in overall system complexity. Superconductor electronic circuits in

their present forms are unlikely to meet the expected future requirements. New devices, circuits, fabrication processes, and architectures are needed.

A full discussion of the applications, drivers, and technology ecosystem for superconductor electronics is not possible in this short article. For further information, see the latest available IRDS CEQIP report [1]. This article will focus on device developments needed for superconductor electronics.

# II. Essentials of Superconductor Electronics

Superconductivity occurs in some metallic materials within limits of temperature, current density, and magnetic field. Superconductor wires have zero resistance for dc electric currents up to some critical

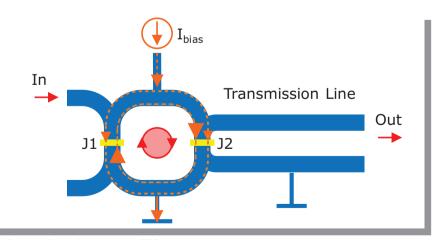

Figure 1. Single flux quantum (SFQ) circuit example: A superconducting loop (blue) with two Josephson junctions (J1, J2) between input and output circuits. Currents in the loop (orange) come from a bias current ( $I_{bias'}$  <<<) and a SFQ in the loop (---). Note that the sum of the currents passes through J2, whereas the difference of the currents passes through J1. When J2 switches, it transfers the SFQ from the loop to the transmission line, on which it propagates at the speed of light on the line.

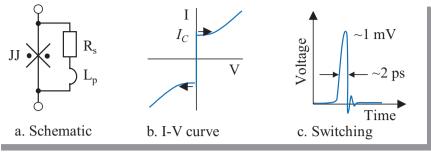

Figure 2. Josephson junction switching element used in SFQ logic. (a) Josephson junction (JJ) with external shunt resistor for critical damping, (b) Current-voltage characteristic, (c) Voltage pulse during switching.

current, Ic, determined by the geometry and properties of the wire.

Current and inductance are important in superconductor circuits, whereas charge and capacitance are important in conventional CMOS circuits, making them significantly different from each other. Fig. 1 shows a simple example superconductor digital circuit.

A Josephson junction consists of two superconducting electrodes connected by a weak link that has a critical current much lower than the electrodes (Fig. 4a). The current through a Josephson junction is a function of the superconducting phase difference across the junction. Common junctions with barrier materials such as aluminum oxide have a sinusoidal relationship,  $I = I_c \sin(\varphi)$ , so the current is zero when there is no phase difference. The nonlinear current-phase relationship is a feature exploited by devices such as gubits.

An important superconductor circuit element, the critically damped Josephson junction (JJ), is shown in Fig. 2. Increasing the current above  $I_c$  causes the junction to leap forward in phase by  $2\pi$ , which produces a voltage pulse across the critically damped JJ that integrated over time equals a flux quantum  $\Phi_0$  = 2.07 mV·ps. Feeding a baby is analogous to how Josephson junctions operate: A small stream of drink is no problem, but exceeding some maximum rate causes the baby to spit up, in the case of Josephson junctions, one flux quantum at a time.

Single flux quantum (SFQ) logic uses the presence of a flux quanta to

signifpy a digital '1'. The voltage pulses generated by junction switching cause flux quanta to move between loops in a circuit. If the current generated in the loop by the flux quantum  $I = \Phi_0/L$  is greater than the critical current of a JJ in the loop, the JJ switches, removing the flux quantum from the loop. If the loop inductance is sufficiently large that no critical currents are exceeded, the flux quantum can remain in the loop. Switching pulse widths are on the order of picoseconds, allowing simple circuits to operate at clock frequencies exceeding 100 GHz.

Challenges of Josephson junctions include low gain. Fan-out greater than one requires the use of splitters, typically using 3 JJs to make a 1:2 splitter. Leakage currents can be a problem unless current flows are carefully balanced or resistors are used to isolate subcircuits. Currents and inductances are interdependent, which makes the design of even moderately complex circuits difficult without good electronic design automation (EDA) tools.

#### **III. Devices and Circuits**

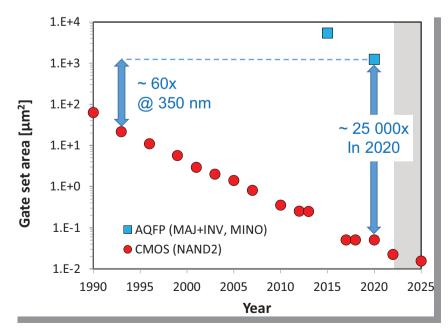

One driver for improved circuits and devices can be seen by comparing the CMOS NAND2 gate with the MAJ-3 adiabatic quantum flux parametron (AQFP) gate. AQFP is one of several superconductor electronic logic families. Fig. 3 shows that the area of the superconductor gate set was roughly 25,000 times larger in 2020. Even comparing the areas at an equivalent feature size of 350 nm, the area is about 60 times larger, indicating that reductions in feature size alone will not be sufficient.

While every superconductor logic family is different, a few approaches to reducing circuit area are broadly applicable.

- 1) Inductors

- a) Decrease wire width

Figure 3. Gate set areas for CMOS and AQFP, a superconductor logic family. The comparisons are at 2020 and at minimum feature sizes of 350 nm.

- b) Multiple wiring layers

- c) High kinetic inductance materials

- d) Transformers: avoid, if possible

- 2) Josephson junctions

- a) Increase critical current density,  $J_c$

- b) Resistive weak link to avoid shunt resistors

- c) Multiple junction layers

- d) Phase-shift junctions to reduce inductors and bias currents

- 3) Interconnects

- a) Narrower transmission lines, which require higher  $J_c$  junctions to drive the increased impedance

- b) Striplines with decreased dielectric thicknesses to decrease impedance

Following are some superconductor devices, roughly in chronological order of need.

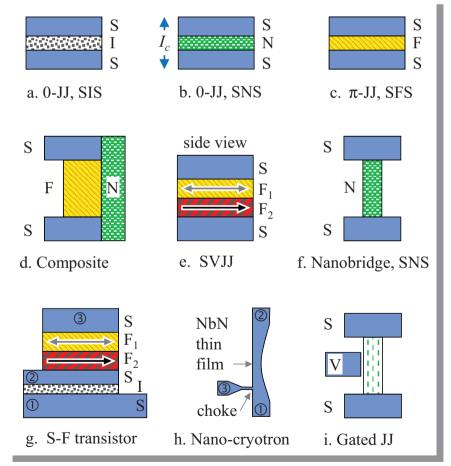

# A. Improved Nb Josephson Junctions (0-Junctions)

Improvements are needed in standard Josephson junctions fabricated with insulating barriers. Consider the current process for fabricating Nb/ Al-AlO\_/Nb 'trilayer' junctions. Niobium deposited on the bottom layer forms columnar grains with surface roughness of several nanometers, which is significant as the insulating barrier layer is only about 1 nm thick. An aluminum layer deposited on top of the lower Nb electrode greatly smooths out the surface, but Al is not superconducting at typical operating temperatures (~4 K), so the thickness variation contributes to tunneling current density variation across the junction. The Al layer is oxidized in a controlled atmosphere, typically at room temperature, before deposition of the Nb top electrode. The resulting amorphous aluminum oxide barrier has both structural and compositional defects that affect the conductivity over nanometer length scales. Supercurrent tunneling depends exponentially on barrier conductivity, which accentuates small variations.

Sputter deposition of Nb can't fill gaps smaller than about 100 nm. The superconducting properties of Nb are also sensitive to stress and to poisoning by oxygen or hydrogen, limiting fabrication temperatures to below about 180 °C, far below the ~400 °C temperature limit for CMOS processing at the back end of the line. A consequence is that standard CMOS processes require performance-limiting modifications for use with Nb junctions. SiO, deposited at low temperatures contains H and OH that comes out if heated too much. After etching to define the junction, wet anodization of the Nb is sometimes performed to seal the barrier region from contamination, although this is not a standard semiconductor foundry

Producing junctions with critical current variations less than 1% has been difficult for junctions with critical current densities greater than 100 µA/µm<sup>2</sup> and diameters less than about 1 µm. Junction critical currents must be about 100 µA at 4 K due to noise considerations. Combined, these constraints have limited minimum junction diameters to roughly 1 µm. Shrinking junction sizes would require greater control over formation of the barrier layer to achieve both higher critical current density and lower variation, which might be possible even with aluminum oxide barriers.

Replacing the barrier layer with a thicker, resistive material is an alternative and has the advantage of providing junctions that do not require shunt resistors, which often require more area than the junction itself [2]. Barrier replacement requires development of a process capable of yielding predictable, uniform, and stable properties using materials compatible with the Nb superconductor.

# B. NbN or NbTiN Josephson Junctions (0-JJ)

NbN or NbTiN are superconductor materials that might be able to replace Nb. They can be fabricated with lower surface roughness and critical temperatures  $T_c > 9$  K for layers deposited on a compatible buffer layer and with film thickness greater than about 20 nm. Epitaxial NbN layers and junctions have been demonstrated recently [3], [4] and should reduce variations.

The primary challenge has been development of a compatible junction barrier with predictable, uniform, and stable properties. Development of processes suitable for 300 mm wafer fabrication will require additional time and effort. Another challenge is that most NbN film deposition uses reactive sputtering, which has difficulty filling gaps below about 250 nm. Chemical vapor deposition (CVD) or atomic layer deposition (ALD) are suitable for 300 mm fabrication and are better able to fill small gaps, but they can be more susceptible to superconducting property degradation due to contamination.

# C. Passive Transmission Lines (PTL)

Transmission lines like the one shown in Fig. 1 allow pulses to move with very low loss or dispersion at the speed of light on the line, typically about c/3 for Nb striplines. Such transmission lines provide data movement capability that could be a significant advantage for superconductor electronics.

A challenge is that the center conductor must be about 4 µm wide using present Nb stripline and junction technology [5]. More compact transmission lines are needed.

#### D. Phase-shift devices

Current supplied to SCE circuits is commonly used to both compensate for energy dissipated and to shift superconducting phase differences within the circuit. The phase shifts bias Josephson junctions in the circuit to control the direction of travel for flux quanta. Superconductor phase engineering is an important part of SCE circuit design without analogy in CMOS circuit design.

Phase shift elements set or change the superconducting phase  $\varphi$  between locations in a superconducting circuit. The phase difference across an inductor is given by  $\varphi_{I} = 2\pi I L / \Phi_{0}$ , where I is the current, L is the inductance, and  $\Phi_0$  is the magnetic flux quantum. Using an inductor to provide a phase difference involves a tradeoff between inductance and current. Large inductances can require too much circuit area, whereas large dc external currents can become difficult to supply without creating magnetic fields that affect circuit operation. For example, with an average junction critical current  $I_c = 200 \mu A$ and bias of 0.7  $I_c$  = 140  $\mu$ A, a chip with just one million junctions would

require a bias current of 140 A! Even at a typical 2.6 mV dc supply voltage, such large currents create significant problems.

Alternating currents (ac) can provide bias currents to many more junctions but require transformers or capacitors to supply current to subcircuits. Transformers rely on magnetic coupling, which does not scale to small sizes, and capacitors add another device type.

Phase-shift devices that do not reguire provision of a continuous supply current include persistent current loops [6] and phase-shift junctions. Junctions with a magnetic barrier material (Fig. 4c) can have a currentphase relationship that is shifted by

$\pi$  radians, thus the name pi-junction  $(\pi$ -JJ), with  $I = I_c \sin(\phi - \pi) = -I_c \sin(\phi)$ . The energy-phase relation (EPR),  $E/E_{n} = \cos(\varphi) - 1$ , has minima at  $\pm \pi$ and provides a stable phase shift current within a superconducting loop that can include regular Josephson junctions (0-JJs). Junctions with phase shifts other than  $\pi$  are called anomalous Josephson junctions,  $\varphi_{\circ}$ -JJs, or  $\psi$ -JJs [7]. Other phase relationships such as  $I = I_c \sin(2\varphi)$  might be achievable with devices like the composite junction shown in Fig. 4d.

Advantages of using such phaseshift devices include reduced external current supply to the chip, reduced power distribution network area, and improved operating margins due to the stability of the current [8]. In AQFP logic,  $\pi$ -JJs can completely eliminate the large output transformers [9].

A challenge is that the current direction generated by a single  $\pi$ -JJ is undetermined. One approach is to design loops to work with current flow in either direction, for example by replacing a single, resistively shunted junction with a loop containing two unshunted junctions and a  $\pi$ -JJ [10]. Another approach is to design connecting loops such that the currents are constrained to flow in one direction. A junction with a set polarity could be better, if fabricable.

Other challenges include incorporation of magnetic materials in commercial fabrication processes and the need for an additional junction layer with the different barrier material.

#### E. Memory Elements

Using Josephson junctions to make memory cells has advantages and disadvantages similar to CMOS SRAM. However, the device count for a JJ memory cell is even higher and the density is much lower. Needed is memory with significantly higher storage density and access times not too much lower than all-JJ memories.

One example is the spin-valve Josephson junction (SVJJ) shown in

Figure 4. Superconductor (S) switching devices. (a) 0-JJ: Josephson junction with insulating (I) barrier, (b) 0-JJ: Josephson junction with normal metal (N) barrier, (c) π-JJ: Josephson junction with a ferromagnetic (F) layer creating a  $\pi$  phase shift, (d) Composite: junction with SFS and SNS in parallel, (e) SVJJ: spin valve Josephson junction, (f) Nanobridge junction, (g) S-F transistor: SVJJ on top of an SIS junction, (h) Nano-cryotron with 3 terminals, (i) Gated JJ: Nanobridge with voltage (V) applied to a third electrode.

Fig. 4e, which contains a hard magnetic reference layer and a soft magnetic layer switchable by magnetic fields provided by superconducting control lines. The critical current of the SVJJ is higher when the two F layers are magnetized in opposite directions.

The IRDS CEQIP report includes several other memory elements under development or consideration [1].

#### F. Weak Link Junctions

Shrinking the size of Josephson junctions below 90 nm might require significantly different devices. Josephson junctions can be produced using weak links in a variety of forms including nanobridges between the superconducting electrodes (Fig. 4f) [11]. The materials are typically metals or even superconductors weakened by the small size. Dimensions of conductive nanobridges must be on the order of the superconducting coherence length in the bridge material, which is ~40 nm for Cu in close proximity to a strong superconductor, ~10 nm for Nb thin films, and ~5 nm for NbN or NbTiN.

Multi-layer or exotic materials might provide improved nanobridge properties. For example, topological insulators have conducting surface or edge states that might be less sensitive to dimensional variations.

Challenges include interfacial effects in composite junctions (e.g., SNS), sensitivity to operating temperature, additional materials (if required), and fabrication on nanometer scales with adequate control of variation.

# G. Multi-terminal switching devices

Both JJs and quantum phase-slip junctions (QPSJs) are two-terminal devices, which require more components to perform typical logic functions. Multi-terminal superconductor switching devices might reduce device count and increase circuit density. One approach is to stack a spin-valve junction on top

of a regular Josephson junction to make a JJ transistor (Fig. 4g). Another approach uses nano-cryotrons with three or four terminals (Fig. 4h). Challenges include fabrication process complexity and development of new logic families.

Recent discovery of a control effect in superconducting devices [12] could lead to development of multi-terminal, gated JJs (Fig. 4i). Challenges include reduction of the switching voltage to a level compatible with the overall circuit, avoidance of supercurrent tunneling from the control electrode, and development of a new logic family.

# H. Quantum Phase-Slip Junctions (QPSJ)

QPSJs are a dual to Josephson junction devices with the roles of phase and charge interchanged as well as current and voltage devices [13]. QPSJs have a critical voltage,  $V_{\rm cr}$  above which an electron pair tunnels through the junction. A charge island consisting of two QPSJs and a capacitor is the main element in QPSJ-based logic circuits. Different connections between charge is-

lands can be used to make different logic gates. Advantages of QPSJs relative to JJs include voltage control and far less sensitivity to magnetic fields. Nanowire QPSJ devices also might have some fabrication advantages over Josephson junctions, although fabrication experience with NbN nanowires indicates that challenges remain, particularly in device variability and operating temperature.

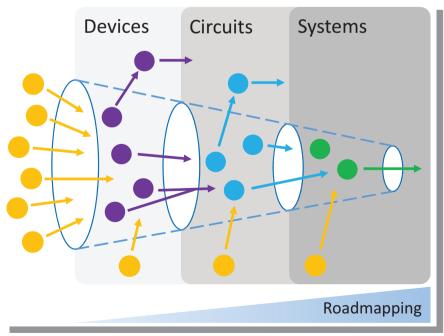

#### IV. Technology Roadmapping

The development of superconductor electronic systems is an example of an open innovation technology funnel (Fig. 5). New approaches enter, die, recombine, spin off, and some pass to the next level. Technology roadmapping activity is an inverse funnel, becoming more detailed and specific as systems requirements become clearer and the component technologies mature. The process is aided by models and figures of merit (FoM). See [14] for a recent and open access article on the process of technology roadmapping in the face of evolving applications and emergent technologies.

Figure 5. Open innovation technology funnel.

#### V. Conclusion

The technology roadmapping process for applications that might use superconductor electronics started with the identification of roadblocks and needs. Identification of superconductor devices, circuits, and technologies that might contribute to solutions is in progress. The next step is to model and evaluate candidates against figures of merit and to develop timelines. The effort is a volunteer IEEE activity open to those interested in contributing.

#### Acknowledgements

IRDS CEQIP team members since 2018 have contributed to the reports that form the base for this article. Special thanks to Anna Herr, Pascal Febvre, Igor Soloviev, and George Tzimpragos for discussing, reading, and editing this article.

D. Scott Holmes (M 2010-SM 2012) received the B.S. degree in mechanical engineering from the Massachusetts Institute of Technology in

1979, M.S. degrees in materials science and in nuclear engineering from the University of Wisconsin-Madison in 1986 and a joint Ph.D. in materials science and nuclear engineering & engineering physics from the University of Wisconsin-Madison in 1989.

From 1990 to 1999 he was a Senior Engineer/Scientist with Lake Shore Cryotronics. From 1999 to 2010 he was a Learning Strategist with Talsico, LLC. From 2010 to 2019 and 2020 to present he has been a Lead Technologist with Booz Allen Hamilton in the Washington, DC area. During 2019 he was a Program Manager at

DARPA in the Microsystems Technology Office.

Dr. Holmes is a member of the IEEE Council on Superconductivity as a representative of the Electron Device Society and chairs the Cryogenic Electronics and Quantum Information Processing (CEQIP) International Focus Team (IFT) for the International Roadmap for Devices and Systems (IRDS).

#### References

[1] "IRDS 2021: Cryogenic Electronics and Quantum Information Processing," IEEE International Roadmap for Devices and Systems, 2021. [Online]. Available: https:// irds.ieee.org/editions/2021/cryogenicelectronics-and-quantum-informationprocessing.

[2] M. Belogolovskii, E. Zhitlukhina, V. Lacquaniti, N. De Leo, M. Fretto, and A. Sosso, "Intrinsically shunted Josephson junctions for electronics applications," Low Temp. Phys., vol. 43, no. 7, pp. 756-765, Jul. 2017, doi: 10.1063/1.4995622.

[3] K. Yan et al., "Intrinsically shunted Josephson junctions with high characteristic voltage based on epitaxial NbN/ TaN/NbN trilayer," Appl. Phys. Lett., vol. 119, no. 15, p. 152602, Oct. 2021, doi: 10.1063/5.0064733.

[4] L. Zhang et al., "Electrical properties of NbN/NbNx/NbN Josephson junctions," Supercond. Sci. Technol., vol. 35, no. 2, p. 025001, Dec. 2021, doi: 10.1088/1361-6668/ ac2eaf.

[5] L. Schindler, P. le Roux, and C. J. Fourie, "Impedance matching of passive transmission line receivers to improve reflections between RSFQ logic cells," IEEE Trans. Appl. Supercond., vol. 30, no. 2, p. 1300607, Mar. 2020, doi: 10.1109/ TASC.2020.2964542.

[6] O. Mielke, T. Ortlepp, J. Kunert, H.-G. Meyer, and H. Toepfer, "Controlled initialization of superconducting  $\pi$ -phaseshifters and possible applications," Supercond. Sci. Technol., vol. 23, no. 5, p. 055003, May 2010, doi: 10.1088/0953-2048/23/5/055003.

[7] S. V. Mironov and A. I. Buzdin, "Collective magnetic and plasma excitations in Josephson psi junctions," Phys. Rev. B, vol. 104, no. 13, p. 134502, Oct. 2021, doi: 10.1103/PhysRevB.104.134502.

[8] I. I. Soloviev et al., "Superconducting circuits without inductors based on bistable Josephson junctions," Phys. Rev. Applied, vol. 16, no. 1, p. 014052, Jul. 2021, doi: 10.1103/PhysRevApplied. 16.014052.

[9] K. Arai, N. Takeuchi, T. Yamashita, and N. Yoshikawa, "Adiabatic quantumflux-parametron with  $\pi$  Josephson junctions," J. Appl. Phys., vol. 125, no. 9, p. 093901, Mar. 2019, doi: 10.1063/1.5080467.

[10] F. Li, Y. Takeshita, D. Hasegawa, M. Tanaka, T. Yamashita, and A. Fujimaki, "Low-power high-speed half-flux-quantum circuits driven by low bias voltages," Supercond. Sci. Technol., vol. 34, no. 2, p. 025013, Feb. 2021, doi: 10.1088/1361-6668/

[11] I. I. Soloviev et al., "Miniaturization of Josephson junctions for digital superconducting circuits," Phys. Rev. Appl., vol. 16, no. 4, Art. no. 4, Oct. 2021, doi: 10.1103/ PhysRevApplied.16.044060.

[12] M. F. Ritter et al., "Out-of-equilibrium phonons in gated superconducting switches," Nat. Electron., vol. 5, no. 2, Art. no. 2, Feb. 2022, doi: 10.1038/s41928-022-00721-1.

[13] A. Malekpoor, S. A. Hashemi, and S. Jit, "Memoryless logic circuit design based on the quantum phase slip junctions for superconducting digital applications," IEEE Trans. Appl. Supercond., vol. 31, no. 9, p. 1303309, Dec. 2021, doi: 10.1109/TASC.2021.3121344.

[14] A. Golkar, I. Yuskevich, K. Smirnova, and R. Vingerhoeds, "Model-based approaches for technology planning and roadmapping: Technology forecasting and game-theoretic modeling," Technol Forecast Soc Change, vol. 173, p. 121082, Dec. 2021, doi: 10.1016/j.techfore.2021.121082.

# 2021 IEEE Semiconductor Interface Specialists Conference (SISC)

William Vandenberghe

The 52nd IFFF Semiconductor Interface Specialists Conference (SISC) was held on 8-11 December, 2021 in a hybrid format with on-site presentations at the

Bahia Resort Hotel, San Diego, CA, alongside virtual presentations and recordings. The virtual participants were able to tune in live and watch on-demand recordings. Despite the difficulties imposed by the COVID-19 pandemic and the start of the omicron surge, the 52nd SISC was a big success with a total of 53 on-site and 71 virtual attendees.

The meeting started with a Wednesday evening on-site tutorial by Prof. Robert (Bob) Wallace from the University of Texas at Dallas. A long-time participant and authority in the SISC community, Prof. Wallace educated the SISC audience on "Physical Characterization of Advanced Device Materials". Prof. Wallace gave an overview of the wide range of surface characterization techniques that are available and outlined the detection limits of various techniques.

After the tutorial, the conference continued with 43 contributed papers and 51 posters presented in 13 sessions. A total of 11 invited speakers gave an overview of the state-of-the-art in power electronics, atomic-layer deposition, III-V semiconductors, ferroelectrics, and oxide electronics.

Unfortunately, in 2021 Prof. T.P. Ma and Prof. Mark Reed, two highly esteemed members of the IEEE community and very frequent attendees of the SISC conference, passed away. SISC had two special sessions in their respective honor with three invited speakers in each. In the T.P. Ma session, chaired by Prof. Wallace,

SISC tutorial presented by Prof. Wallace (at the podium) from the University of Texas at Dallas

IBM's Huiming Bu presents in the "Tribute to TP" Ma session

UT Dallas Ph.D. student Ali Saadat (right) operating the main conference computer and presenter Dr. Yasuo Cho from Tohoku University, Japan (left)

Prof. Alan Seabaugh from the University of Notre Dame, Prof. James Tour from Rice University, and Barry Merriman from Roswell Biotechnologies paid homage to Mark Reed and his legacy in Nanoelectronics and Molecular Electronics. The T.P. Ma session was chaired by a former

SISC's annual limerick contest hosted by 2019 SISC Limerick contest winner Dina Triyoso (right front)

T.P. Ma student and the 2021 SISC general chair: Prof. Wenjuan Zhu from the University of Illinois Urbana-Champaign. Dr. Huiming Bu from IBM, Dr. An Chen from the Semiconductor Research Corporation (SRC), and Prof. Peide Ye from Purdue University paid tribute to T.P. Ma.

To manage the interaction between the on-site attendees and the virtual attendees, Mr. Ali Saadat, a Ph.D. candidate from the University of Texas at Dallas operated the main conference computer. Ali had to rapidly switch between on-site presentations, remote presentations, and recordings. He had to ensure that for all three presentations modes, onsite and remote participants could see the slides, hear the audio from on-site presenters, hear the question and answers, and broadcast the two cameras capturing on-site activities. Ali's task became even more interesting when on Thursday morning, no internet was available at the Bahia

Hotel and the conference had to run through a hotspot!

With the sizeable on-site attendance, SISC was able to bring back its limerick contest in 2021. The limerick contest is a long standing tradition at SISC and was hosted by the SISC 2019 Limerick contest winner, Dr. Dina Triyoso from Tokyo Electron Ltd. The 2018 Limerick contest winner Prof. Paul Hurley put up a strong limerick again lamenting the absence of the SISC hospitality suite this year

Back to SISC were we all meet And after a banquet that's such a great treat Now to discussions that are quicker And slicker with liquor Hey! ... Where's the hospitality suite?

but ultimately after long deliberation, UC San Diego Ph.D. student Aaron McLeod won with

The largest question of them all: Why is your font that small?

The attendees are blind And we're running behind Please, dear god, pass the Tylenol

A best student paper was established in 1995 in honor of Prof. E.H. Nicollian and the winner of the 2021 SISC Ed Nicollian Award is Nujhat Tasneem from Georgia Institute of Technology. The winner of a new award, instituted in honor of Prof. T.P. Ma, the 2021 T.P. Ma Award for Best Student Poster goes to Simon Mellaerts from KU Leuven.

The 2021 Executive committee consisted of Ex-Officio John Robertson from Cambridge University, General Chair Wenjuan Zhu from the University of Illinois, Technical Program Chair William Vandenberghe from the University of Texas at Dallas, and Arrangements Chair Peide Ye from Purdue University.

William Vandenberghe 2021 Technical Program Chair Associate Professor Department of Materials Science and Engineering University of Texas at Dallas

# UPCOMING TECHNICAL MEETINGS

# The 2022 IEEE VLSI Symposium on Technology & Circuits, Now Merged as a Single Event With the Theme: Technology & Circuits for the Critical Infrastructure of the Future

Now in its 42nd year of delivering a unique convergence of technology and circuits for the microelectronics industry, the Symposia on VLSI Technology & Circuits will be merged into one Symposium to maximize the synergy across both domains. The newly merged 2022 IEEE VLSI Symposium on Technology & Circuits is organized around the theme: "Technology & Circuits for the Critical Infrastructure of the Future." The five-day hybrid event, combining both live sessions onsite at the Hilton Hawaiian Village, as well as on-demand access to selected presentations, is scheduled for 13-17 June 2022 in Honolulu, Hawaii. The Symposium will feature advanced VLSI technology developments, innovative circuit design, and the applications they enable, such as artificial intelligence, machine learning, IoT, wearable/implantable biomedical applications, big data, cloud / edge computing, virtual reality (VR) / augmented reality (AR), robotics, and autonomous vehicles.

The week-long Symposium will continue its reputation as the microelectronics industry's premiere international conference integrating technology, circuits, and systems with a range and scope unlike any other conference. In addition to the technical presentations, the Symposium program will feature a demonstration session, evening panel discussions, joint focus sessions, short courses, workshops, and a special forum session that provides a focused discussion on a specific topic relevant to the Symposium theme.

#### Short Courses on Key VLSI topics

- Monolithic & Heterogeneous Integration

- Advances in Application-Specific Computing Systems & Technologies

- Electronics That Drive the Next Generation Smart Car

#### **Plenary Sessions**

- "Holistic Patterning to Advance Semiconductor Manufacturing for the 2020s and Beyond," by Martin Van den Brink, President & CTO, ASML

- "Semiconductor Innovations, from Device to System," by Yuh-Jier Mii, Senior Vice President for R&DTSMC

- "From System-on-Chip (SOC)

to System on Multichip (SoMC)

Architectures: Scaling Integrated

Systems Beyond the Limitations

of Deep-Submicron Single

Chip Technologies," by Chris

Patrick, Senior Vice-President,

Qualcomm

"The Rise of Memory in the Ever-Changing Al Era – From Memory to More-Than-Memory," by Seok-Hee Lee, President & CEO, SK Hynix

**Focus Sessions** include BEOL processes, new concepts for transistor scaling, 6G, compute-in-memory, biomedical technology, and 3D heterogeneous integration.

In addition, three **Evening Panel Sessions** have been announced:

- "What Will It Take To Bring New Material From Lab To Manufacturing?"

- "Building The 2030 WorkForce: How to Attract Great Students And What to Teach Them"

- "Supply Chain & Foundry Future"

The Symposium program also features a multi-speaker Forum Session on "VLSI for Infrastructure and Infrastructure for VLSI."

A series of workshop sessions will be held during the Symposium program to provide additional learning opportunities for participants:

#### **Technology Workshops**

- Heterogeneous Integration The Next Scaling Frontier: Material & Process Challenges

- Machine Learning Applications in Semiconductor Processes and Equipment Development

#### **Circuit Workshops**

- The Emerging Ecosystem of Open-Source Chip Design

- · Analog/RF Circuits for IoT

- Recent Advances in Radar, mmWave, and Sub-THz: Technology, Packaging, & Circuits

#### **Joint Workshop**

· Cryogenic Electronics for Quantum Computing

Special events at the Symposium include mentoring events for Women in Engineering and Young Professionals, sponsored by the IEEE Electron Devices Society and the Solid State Circuits Society.

Best Student Paper Awards for each track Symposium are chosen based on the quality of the papers and presentations. The recipients will receive a monetary award, travel cost support, and a certificate. For a paper to be reviewed for this award, the lead

author and presenter of the paper must be enrolled as a full-time student at the time of submission, and must indicate on the web submission form that the paper is a student paper.

Further information about the Symposium is available at: http:// www.vlsisymposium.org.

#### **Sponsoring Organizations**

The IEEE VLSI Symposium on Technology & Circuits is sponsored by the IEEE Electron Devices Society, in cooperation with the IEEE Solid-State Circuits Society and Japan Society of Applied Physics,

in cooperation with the Institute of Electronics, Information and Communication Engineers.

#### **Media Contacts**

(North America and EU) BtB Integrated Marketing-Chris Burke, co-Media Relations Director E-mail: chris.burke@btbmarketing.com

(Japan and Asia) Secretariat for VLSI Symposia c/o JTB Communication Design, Inc. Tokyo, Japan E-mail: vlsisymp@itbcom.co.jp

The fourth edition of the IEEE Latin American Electron Devices Conference, LAEDC 2022, is a three-day meeting to be held in Cancún, México from 4-6 July in a hybrid format with both in-person and virtual options that will enable participants from all over Latin America and other geographies to attend at low cost.

LAEDC is an international and flagship conference sponsored by the IEEE Electron Devices Society (EDS) in Latin America, that provides a unique global opportunity to bring together specialists, senior scientists, students as well as young researchers to share and discuss their latest research and innovations in all Electron Device related fields. Proceedings will be published by IEEE and the accepted papers will be available on IEEE Xplore. The best papers presented at the conference will be considered for publication in a special issue of the IEEE Journal of the Electron Devices Society.

Continuing with the tradition of the past editions, the 4th IEEE LAEDC will be covering technical areas including all electron-based devices, electron devices for quantum computing, RF-MMW-5G, semiconductor, MEMS and Nanotechnologies, packaging-3D integration, sensors and actuators, display technology, modeling and simulation, reliability and yield, device characterization, biomedical devices, circuit-device interaction, novel materials and process modules, technology roadmaps, electron device engineering education, electron device outreach, optoelectronics, photovoltaic and photonic devices and systems, energy harvesting and will also have a strong component of technology based Humanitarian Projects and STEM.

For more information, please contact laedc@ieee.org | https://attend. ieee.org/laedc-2022/

> Fernando Guarin IEEE Fellow EDS Senior Past President

# 49TH IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE (PVSC), PHILADELPHIA

It is with distinct pleasure and anticipation that you are invited to join the 49th IEEE Photovoltaic Specialists Conference on 5-10 June in Philadelphia at the spectacular Pennsylvania Convention Center. For 60 years, PVSC has been the premier scientific and technical conference focused on all areas of photovoltaics from fundamental science to commercial applications and, increasingly, to deployment, policy, and resources. The PVSC is strongly committed to creating an inclusive, respectful conference environment that welcomes participation from people of all races, ethnicities, genders, ages, abilities, religions, and sexual orientations because we are more innovative and enriched when we reflect the diversity of our photovoltaics and broader community.

Technical Program: We continue that tradition by offering a diverse technical program divided into eleven areas and featuring several special and joint technical sessions highlighting our cross-cutting synergies. We will have a slate of exciting keynote, plenary and invited speakers giving up-to-date research summaries and breakthroughs. A day dedicated to tutorials from leading experts in seminal areas will enable students and scientists joining the field or any participants to expand their knowledge to new areas. The conference will also include several exciting cross-cutting themes and joint areas such as "Advanced Resource Management for 100% Renewable Electricity", "Hybrid Tandem/Multijunction Solar Cells" and "Challenges and opportunities on grid and microgrid integration of PV systems".

New this year: Publication of a conference proceeding will be optional. Full papers are encouraged but short abstracts will otherwise

be used as the publication of record. Authors will have the option of submitting their evaluation abstract or a longer conference proceeding by the 31 May 2022, publication deadline. Exceptional submissions will be recommended for expedited review and publication in the *IEEE Journal of Photovoltaics*. Also, we have merged former Technical Areas on III-V and on space in new Technical Area 3 on III-V, Space and Concentrator Photovoltaics.

If you would still like to contribute technically, please submit your abstract before our late submissions deadline on 8 April 2022.

Venue & Hotel: The conference will be held at the Pennsylvania Convention Center in the heart of Philadelphia. The exhibits area will provide a chance to learn about some of the latest developments in characterization, materials and manufacturing. All these events will be enhanced by ample opportunities for networking to form new collaborations and friendships as well as renew old acquaintances. For accommodation, plenty of rooms are reserved in the Marriott Philadelphia Downtown Hotel conveniently connected to the Convention Center. The

Hotel has all the amenities you want from a conference hotel to allow networking including extra meeting and gathering sites. Its location in Center City puts the conference within walking distance of countless great restaurants, museums and, yes, historical sites.

Awards: We will be presenting the awards for the prestigious William R. Cherry Award, along with the Stuart R. Wenham Young Professional Award. We will also present awards for Best Student Presentation and the Best Poster Award. Additionally, to encourage and invest in the next generation of photovoltaic researchers, engineers and specialists, middle and high school competition for students around the world and of all ages (4th to 12th grade) will be held.

On behalf of all the dedicated volunteers who comprise the PVSC Organizing, Cherry, and International Committees, we look forward to personally welcoming you to Philadelphia for the 49th IEEE PVSC. Further details and registration can be found at: https://ieee-pvsc.org/PVSC49

Bill Shafarman 49th IEEE PVSC Chair

### 2022 IEEE INTERNATIONAL INTERCONNECT TECHNOLOGY CONFERENCE (IITC)

HTTPS://IITC-CONFERENCE.ORG/

We are excited to announce the 25th edition of IITC sponsored by the IEEE Electron Devices Society as the premier conference for advanced interconnect technology devoted to leading-edge research in the field of advanced metallization and 3D integration for ULSI applications.

IITC 2022 will be held in a hybrid format 27-30 June 2022 in San Jose. California. Given the international nature of the interconnect research community, IITC is organized sequentially in Asia, Europe and North America. The conference was held last year in the historic city of Kyoto, Japan and in 2022 it will return to the west coast of the United States. We are tentatively planning to proceed with a traditional in-person conference in San Jose with an option to attend virtually for those who may be subject to pandemic-related travel restrictions. On-demand content will be available.

The conference presents various talks, papers and posters covering innovative research and development in all areas of research related to BEOL/MOL/3D interconnects, including design, unit process, integration, reliability and packaging. This conference attracts professionals from industry, academia and national laboratories in semiconductor processing, interconnect design and equipment development.

#### Workshop

Prior to the technical program, a workshop focused on "Advanced Packaging and 3D Integration" will be held on Monday, 27 June. We plan to have seven industry experts give technical presentations covering the latest progress in the field of packaging and 3D integration.

For more information, please visit the IITC 2022 website at https://iitcconference.org/ The IITC committee members look forward to seeing you either virtually or in-person at IEEE IITC 2022!

> Hui Jae Yoo, Intel 2022 IITC General Chair

# 52ND EUROPEAN SOLID-STATE DEVICE RESEARCH CONFERENCE AND 48TH EUROPEAN SOLID-STATE CIRCUITS CONFERENCE

The aim of ESSDERC and ESSCIRC is to provide an annual European forum for the presentation and discussion of recent advances in solidstate devices and circuits. The level of integration for system-on-chip design is rapidly increasing. This is made available by advances in semiconductor technology. Therefore, more than ever before, a deeper interaction among technologists, device experts, IC designers and

system designers is necessary. While keeping separate Technical Program Committees, ESSDERC and ESSCIRC are governed by a common Steering Committee and share Plenary Keynote Presentations and Joint Sessions bridging both communities. Attendees registered for either conference are encouraged to attend any of the scheduled parallel sessions, regardless to which conference they belong. In 2022, ESSDERC and ESSCIRC will be held 19-22 September 2022, at the University of Milan-Bicocca (Milan, IT), that is well connected (metro, bus, train) with Milan downtown. The conference will provide a balanced mix of keynote and plenary talks, device circuits and joint sessions with prestigious invited speakers, workshop and tutorials, exhibits, and technical presentations. Camera-ready four-page papers are due by 12 April 2021. Papers presented at the conference will be considered for the

"Best Paper Award" and "Best Young Scientist Paper Award". The selection will be based on the results of the paper selection process and the judgement of the conference participants. The 2022 Award Ceremony will take place during ESSDERC/ES-SCIRC 2023.

ESSDERC and ESSCIRC have evolved over the last years to follow recent R&D device, circuit and system fast-growing topics. Besides the traditional ESSDERC and ESSCIRC tracks, a number of JOINT tracks have been introduced, to encourage and facilitate interactions between circuit, system and device researchers.

ESSDERC/ESSCIRC encourages submissions in all areas of solid-state devices, circuits and systems, with special emphasis on: Analog, Power and RF Devices - Electron Device Simulation and Modelling - Advanced Technology, Processes and Materials -Neuromorphic Computing, Advanced Memories, Al Accelerators, in-Memory-Computing, Security - Advanced Computing Devices and Circuits: Advanced CMOS, Post-CMOS, Quantum Computing - Sensors, MEMS, Bioelectronics, Biomedical Electronics, Optoelectronics, Display and Imaging - Analog Circuits - Data Converters -RF and mm-Wave Circuits - Frequency Generation - Wireless and Wireline Interfaces - Integrated Power Electronics and Power Management - Digital Circuits & Systems

#### **Conference Highlights and Opportunities**

4 joint keynote presentations 3 ESSDERC keynote presentations 3 ESSCIRC keynote presentations

Invited papers with overall coverage of all aspects of advanced devices and circuits

#### Presentation of IEEE and **ESSDERC/ESSCIRC Awards**

ESSDERC/ESSCIRC Welcome Reception on Tuesday, 20 September 2022 ESSDERC/ESSCIRC Gala Dinner on Wednesday, 21 September 2022

#### **Tutorials and Workshops**

For the call for papers and other information, visit the ESSDERC and ESSCIRC 2022 website at www.esscirc-essderc2022.org and join the ES-SCIRC - ESSDERC LinkedIn group.

The ESSXXRC 2022 committee members look forward to seeing you in Milan, Italy!

> Andrea Baschirotto 2022 ESSXXRC General Chair University of Milan-Bicocca

# SOCIETY NEWS

#### FROM THE DESK OF THE PRESIDENT....

Ravi Todi PhD IEEE Fellow EDS President

Dear Electron Devices Society colleagues,

ı am most pleased to inform you of upcoming plans to conduct a Strategic Planning Workshop. The results will play a significant role in

the continuous quest of the Society to achieve ever higher levels of excellence. We strive to be an indispensable resource for those who want to achieve success in our field. We exist for the benefit of our members and for our profession as well as for the greater good of humanity. Some of you may remember that four years ago we engaged in a similar initiative which produced, among other things, four strategic goals which we have striven to use in guiding us in how we develop and resource programs for your benefit. We intend to build

upon these to guicken the pace to becoming a stellar Society in IEEE and a magnet for new members because of the value we create for you.

The Workshop will be structured in three parts. (1) Where are we now? (2) Where do we want to be in 2032? (3) How will we get there?

The output of the Workshop will be presented to the Board of Governors in the form of recommendations for action and will be made public in a subsequent Newsletter Issue. The recommendations will include a statement of our vision for EDS in 2032, a statement of our core values, a list of strategic goals and most importantly a recommendation for a deployment plan. Included in the deployment plan will be a short list of Key Performance Indices (KPIs) which will be quantitative, will be reviewed regularly and will be owned by members accountable for results. This will be one of the means used for driving initiatives aimed at realizing our vision and converting our strategic goals into action.

In keeping with our tradition of coordinating our Board of Governors Meeting with a major conference, we will be tentatively holding the summer meeting on June 12 prior to and in conjunction with the 2022 IEEE Symposium on VLSI Technology and Circuits set for June 12-17. The Strategic Planning Workshop will be on June 10-11 and will precede the Board Meeting. The Workshop participants will be a select group of past, present, and future leaders of the Society. All other EDS members are invited to observe the deliberations if you find yourself in this locale on these dates. But whether you are attending or not we will be soliciting your inputs. Comments or questions are welcome and can be submitted to eds@ieee.org.

> Ravi Todi PhD IEEE Fellow **EDS President**

#### MESSAGE FROM EDS NEWSLETTER EDITOR-IN-CHIEF

Daniel Tomaszewski EDS Newsletter Editor-in-Chief

Readers. Members of the IEEE EDS Community,

Welcome to the IEEE EDS Newsletter issue April 2022.

First of all I would like to express our great

concern and warmest greetings to people, to IEEE community, and to EDS members and volunteers in

Ukraine. Kateryna Arkhypova, the Newsletter Regional Editor for Region 8 Eastern Europe is one of them. She lives in Kharkiv, the second largest city of Ukraine, which has been so heavily experienced by the war. May peace return there and allow Ukrainian society to have dreams, rebuild the country and work in safe living conditions.

On behalf of the Newsletter editorial team I would like to congratulate the newly elected EDS Executive Committee Members, EDS BoG Members-at-Large, Chairs of the Standing and Technical Committees and wish them a fruitful work on promoting excellence in the field of electron devices for the benefit of humanity and on fostering professional growth of its members (after EDS Vision and Mission Statements).

In this issue, we are launching a series of articles celebrating the 75th Anniversary of the invention of transistors, which contributed not only to unprecedented advances in technology, but also to the tremendous social changes we are witnessing.

The series is coordinated by Manoj Saxena, 75th Anniversary of the Transistor AdHoc Committee Chair. We are more than happy that the first article in the series was written by Prof. Hiroshi Iwai. We are looking forward to the next articles.

In the Society News we share with you an article by EDS President, Ravi Todi on the upcoming undertakings concerning Strategic Planning. We are looking forward to news on this important activity in the next Newsletter issues.

The Technical Briefs section brings us the article by Scott Holmes on low-temperature electronics, a new installment of the series related to the International Roadmap for Devices and Systems IFT Reports. Besides, please find information about the recent edition of the SISC technical conference. I hope that SISC, concerning an important branch of the electron devices domain, will be present in EDS issues regularly. For the last time it was an-

nounced in 2017, whereas it was reported in 1996 (!). To finalize a topic of reporting the technical meetings I would like to add that 4th IBM IEEE CAS/EDS AI Compute Symposium (AICS'21) is broadly summarized in Regional News.

The Upcoming Technical Meetings section presents advertisements of the important conferences which will be held in 2022: LAEDC, VLSI, IITC and ESSDERC. Besides, please find in the Regional News section an advertisement of European Microwave Integrated Circuits Conference (Eu-MIC) 2022. Dates of other conferences sponsored or supported by EDS you may find in the Conference Calendar published at the end of this issue or on the website https://eds.ieee.org/conferences.

In the EDS Young Professionals section Dr. Avirup Dasgupta, 2021 IEEE EDS Early Career Award Winner answers questions by Manoj Saxena, whereas in the EDS Women in Engineering section Dr. Kelin Kuhn, a

world-renowned materials scientist, comments on Murphy's laws.

In the Humanitarian Projects News, Chapter News, and Regional News sections we present traditionally articles on achievements and on activities carried out day by day by the EDS chapters worldwide. Among them, there was the IEEE EDS STEM Program conducted in Malaysia.

Dear Readers, if you have any suggestions, comments regarding the Newsletter contents, please do not hesitate to contact the editorial team. We will be very glad to receive your feedback. Interesting views will be presented with the consent of the authors, along with our replies in the Letters to Editors section.

Finally, I would like to express again my thanks to all the article Authors and to all the members of the Editorial Team. I hope that the Readers will find the issue interesting and informative.

Sincerely, Daniel Tomaszewski

# ECE PROFESSOR MARVIN WHITE WINS EMMY AWARD FOR HISTORIC ENGINEERING ACHIEVEMENTS

REPRINTED WITH PERMISSION FROM THE OHIO STATE UNIVERSITY

The National Academy of Television Arts and Sciences announced Professor Marvin White, of the Ohio State University, won an Emmy® for his work in Technology and Engineering. According to the Engineering Achievement Committee, the award helps honor the "tool makers" of the industry who crafted the modern television viewing experience. White said he never dreamed of winning a Tech Emmy® someday. "The whole thing was quite a surprise," he said. White, a professor of Electrical and Computer Engineering(ECE) at Ohio State, and Northrop Grumman received the award for work on Correlated Double Sampling for Image

Sensors, which showed excellence in engineering creativity.

White's pioneering technological contributions and patents span decades in the field of engineering. Many are still found today in personal cameras, televisions, satellite imaging systems; even the Hubble Space Telescope.

"Screen actors are always cited for Oscars. Stage performers are similarly proud of their Tony Awards. Television journalists are quick to add an Emmy® Award to their resume – and with good reason," the committee letter to White states. "Your work on Correlated Double Sampling (CDS) for Image Sensors showed excellence

in engineering creativity and you join a distinguished group of honorees that are chosen each year by dozens of industry experts and peers."

This year's recipients will be honored at the 73rd Annual Technology & Engineering Emmy® Awards Ceremony tentatively scheduled for April 25th at the Wynn Hotel in Las Vegas, Nevada.

"Historically, TV began with Image Orthicons and Vidicons to capture scenes at low-light levels, but were later replaced by light-weight, high-resolution, solid-state imagers," White said. "In the late 1960s and early 1970s at Westinghouse, I and a team of engineers worked on a way to process images from these solid-state imagers and we called the method Correlated Double Sampling or CDS, which is widely used today."

The Technology & Engineering Emmy® Award was actually the first among any awards issued in 1949, said Adam Sharp, CEO & President, NATAS.

"It laid the groundwork for all the other Emmys to come," he said. "We are extremely happy about honoring these prestigious companies, where the intersection of innovation, technology, and excitement in the future of television can be found."

White joined the Ohio State ECE faculty in 2010 after many years teaching at Lehigh University in Bethlehem, PA, where he was the Sherman-Fairchild Professor of Electrical and Computer Engineering and Director of the Sherman-Fairchild Center for Solid State Studies. He also served two decades at Westinghouse Electric Company, as well as serving

stints at the National Science Foundation and Naval Research Laboratory. He has authored or co-authored over 300 technical papers, contributed chapters to four books, and has 27 U.S. patents.

The professor is a member of the U.S. National Academy of Engineering, an IEEE Life Fellow, and served as a distinguished national lecturer of the IEEE Electron Devices Society. He received several awards for his contributions to the development of high-sensitivity, solid-state cameras, and imagers and for major contributions to progress in semiconductor devices including the IEEE Electron Devices Society's 1997 J. J. Ebers Award, and the IEEE 2000 Masaru Ibuka Consumer Electronics Award. In 2011, he received Ohio State's Distinguished Alumnus Award.

### ANNOUNCEMENT OF NEWLY ELECTED OFFICERS & BOG MEMBERS

Fernando Guarin 2021 EDS Nominations and Elections Chair