APRIL 2023 VOL. 30, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI

**e** III

**e** t

## TABLE OF CONTENTS

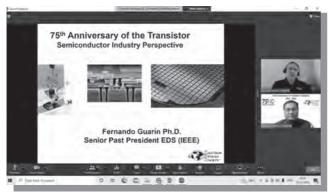

#### 75TH ANNIVERSARY OF THE TRANSISTOR ...... 1

- Perspectives on Low-voltageTunnelTransistors for Beyond CMOS Logic

- 75 Years of Compact Models: From Shockley to Sticker Shock

TECHNICAL BRIEFS ..... 10 • Third Breakdown: A Physical Mechanism found in High-k Metal-gate CMOS

####

- 2023 IEEE Symposium on VLSI Technology and Circuits

- 2023 IEEE International Memory Workshop

- 2023 IEEE BiCMOS and Compound Semiconductor Integrated Circuits and Technology Symposium

#### Message from EDS Newsletter Editor-in-Chief

- Announcement of Newly Elected BoG Members

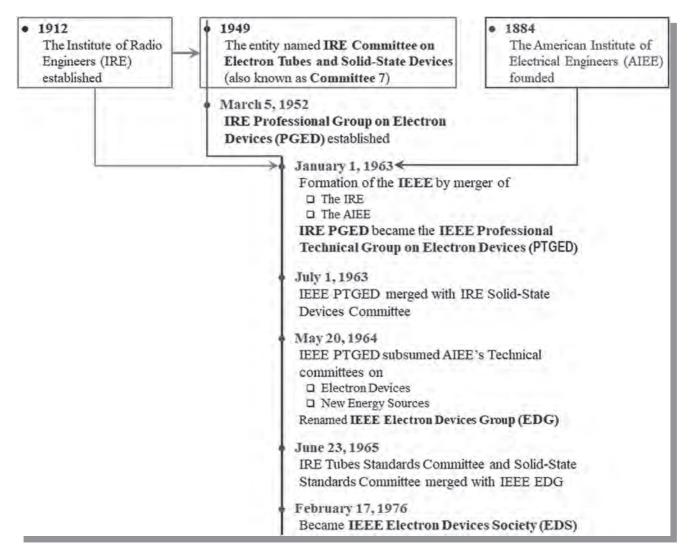

- A Brief History of the IEEE Electron Devices

- Society: Part I

- In Memoriam Prof. Dr. Adolf Goetzberger

- Letter to the Editor

####

- 2023 IEEE Robert Bosch Award Winner

- 2023 IEEE Robert Bosch Award-Call for Nominations

- 2022 IEEE EDS Lester F. Eastman Award Winner

- 2023 IEEE EDS Lester F. Eastman Award-Call for Nominations

- 2022 IEEE EDS J.J. Ebers Award Winner

- 2023 IEEE EDS J.J. Ebers Award-Call for Nominations

- 2022 EDS Education Award Winner

- 2023 EDS Education Award-Call for Nominations

- 2022 IEEE EDS Early Career Award Winner

- 2023 EDS Early Career Award-Call for Nominations

#### EDS WOMEN IN ENGINEERING ...... 39

Women in Semiconductor Panel Session and Young Professionals Meet at ICEE2022

#### EDS YOUNG PROFESSIONALS ...... 40

• Call for Nominations-2023 EDS Student Fellowships

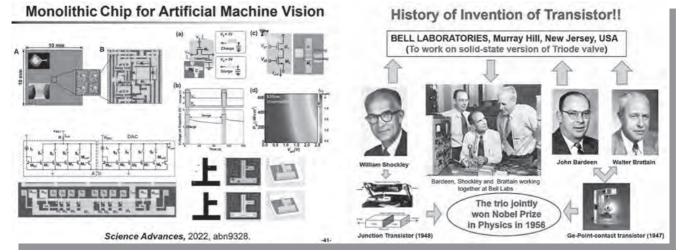

| CHAPTER NEWS       41         • STEM Programs funded by IEEE EDS Educational<br>Activities in Malaysia         • ED NIT-Silchar Student Branch Chapter Social Outing |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REGIONAL NEWS 44                                                                                                                                                     |

| EDS MEETINGS CALENDAR                                                                                                                                                |

```

EDS MISSION, VISION, AND FIELD OF INTEREST ..... 64

```

## NNIVERSARY ANSISTOR

## PERSPECTIVES ON LOW-VOLTAGE TUNNEL TRANSISTORS FOR BEYOND CMOS LOGIC

Alan Seabaugh

DEPARTMENT OF ELECTRICAL ENGINEERING. UNIVERSITY OF NOTRE DAME. NOTRE DAME, IN 46556

In this, the 75th year anniversary of the transistor, complementary metal oxide semiconductor fieldeffect (CMOS) transistors continue to advance, from fin structures to nanosheets and to angstrom technology nodes. In the wake

of this development, discussions continue on steep-subthresholdswing transistors which still hold promise to outperform CMOS at low voltage, but have so far fallen short of the performance needed for applications. It is worth reviewing the development of the tunnel field-effect transistor (TFET) with the aim to stimulate new ideas and fresh consideration of the paths taken and the technical challenges. For a deeper dive, there is a chapter in the just published Springer Handbook of Semiconductor Devices [1] on tunnel fieldeffect transistors, and there are many recent reviews, search e.g. "TFET review."

The TFET is an MOS technology and shares many of the structural attributes needed for a transition into a foundry process. A complementary TFET with comparable current drive at lower supply voltage than Si CMOS would enable lower power dissipation without sacrificing speed. The TFET could readily move into the design ecosystem with the primary new device attribute being the steep subthreshold

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### ELECTRON DEVICES

#### SOCIETY

#### President

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

**President-Elect** Bin Zhao Freescale Semiconductor Email: bin.zhao@ieee.org

Treasurer Roger Booth Qualcomm Email: boothrog@vahoo.com

**Secretary** M.K. Radhakrishnan NanoRel Email: radhakrishnan@ieee.org

**Sr. Past President** Fernando Guarin GlobalFoundries Email: fernando.guarin@ieee.org

Vice President of Education Navakanta Bhat Indian Institute of Science Email: navakant@gmail.com

Vice President of Meetings Kazunari Ishimaru Kioxia Corporation Email: kazu.ishimaru@kioxia.com Vice President of Membership and Services Merlyne de Souza University of Sheffield Email: m.desouza@sheffield.ac.uk

Vice President of Publications and Products Arokia Nathan University of Cambridge Email: an299@cam.ac.uk

Vice President of Regions/ Chapters Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

Vice President of Strategic Directions Doug P. Verret IEEE Fellow Email: dougverret@gmail.com

Vice President of Technical Committees John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2023                                                                                                                                        | Term       | 2024                                                                                                                  | Term                                                                                                  | 2025                                                                                                                    | Term                                          |

|---------------------------------------------------------------------------------------------------------------------------------------------|------------|-----------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Roger Booth<br>Xiojun Guo<br>Edmundo Gutierrez<br>Francesca lacopi<br>Benjamin Iniguez<br>P. Susthitha Menon<br>Manoj Saxena<br>Sumant Sood | (1)<br>(2) | Mario Aleman<br>Paul Berger<br>Yogesh Chauhan<br>Maria De Souza<br>Patrick Fay<br>Kazunari Ishimaru<br>William Nehrer | <ol> <li>(1)</li> <li>(2)</li> <li>(1)</li> <li>(2)</li> <li>(2)</li> <li>(2)</li> <li>(2)</li> </ol> | Constantin Bulucea<br>Daniel Camacho<br>John Dallesasse<br>Mario Lanza<br>Lluis Marsal<br>Geok Ng<br>Mayank Shrivastava | (2)<br>(2)<br>(2)<br>(2)<br>(1)<br>(2)<br>(1) |

### NEWSLETTER

#### EDITORIAL STAFF

**Editor-In-Chief**

Daniel Tomaszewski Institute of Microelectronics and Photonics Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

Associate Editor-in-Chief Manoj Saxena Deen Dayal Upadhyaya College University of Delhi

Email: msaxena@ieee.org

REGIONS 1–6, 7 & 9 Eastern, Northeastern & Southeastern USA (Regions 1, 2 & 3) Rinus Lee TEL Technology Center, America Email: rinuslee@ieee.org

#### Central USA & Canada

(Regions 4 & 7) Michael Adachi Simon Fraser University Email: mmadachi@sfu.ca

Southwestern & Western USA (Regions 5 & 6) Lawrence Larson Texas State University Email: Larry.Larson@ieee.org

Latin America North (Region 9) Joel Molina Reyes INAOE Email: jmolina@inaoep.mx

#### Latin America South (Region 9)

Paula Ghedini Der Agopian UNESP, Sao Paulo State University Email: paula.agopian@unesp.br

#### <u>REGION 8</u>

Scandinavia & Central Europe Marcin Janicki Lodz University of Technology Email: ianicki@dmcs.pl Eastern Europe

Mykhaylo Andriychuk Pidstryhach Inst. for App. Problems of Mech. and Math. Email: andr@iapmm.lviv.ua

#### United Kingdom, Middle East & Africa

Stewart Smith Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

Western Europe

Mike Schwarz Mittelhessen University of Applied Sciences Email: mike.schwarz1980@ googlemail.com

#### REGION 10

Australia, New Zealand & South East Asia Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University Email: thhou@mail.nctu.edu.tw

South Asia

Soumya Pandit University of Calcutta Email: soumya\_pandit@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission.

| Newsletter | Deadlines |

|------------|-----------|

|            |           |

ISSUE

| Due Da | ΤE |

|--------|----|

|        |    |

October July 1st January October 1st April January 1st July April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2023 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

SUSTAINABLE FORESTRY INITIATIVE SEVENES

## PERSPECTIVES ON LOW-VOLTAGE TUNNEL TRANSISTORS FOR BEYOND CMOS LOGIC

#### (continued from page 1)

swing. In the MOSFET, the current control mechanism is thermionic emission over an energy barrier, and this sets a fundamental limit on the minimum subthreshold swing at 60 mV/decade change in current at room temperature. The TFET relies on electric field control of tunneling and with this current control, the subthreshold swing can be lower (steeper) than 60 mV/decade.

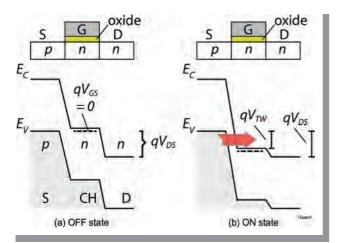

The n-channel TFET, in planar form, differs from the MOSFET in the polarity of the source-channel junction. In the off state, shown in figure 1 (a), electrons in the valence band of the source are energetically blocked from tunneling into the channel. With a positive gate bias these electrons in the source tunnel into the channel, with current injection set by the overlap of the filled valence band and empty conduction band states in the channel; this is labeled the tunneling window,  $qV_{TW}$ , in figure 1 (b). The gate voltage simultaneously modulates both the tunneling probability for injection of electrons into the channel and the availability of empty channel states.

There is a long history of experimental and theoretical development of tunneling diodes and transistors leading to the TFET [2], [3]. The realization that low subthreshold swing could be achieved by gating of interband tunneling began to appear in publications in 2003 and 2004 [4]–[6]. In 2004, Joerg Appenzeller reported 40 mV/dec subthreshold swing in a carbon nanotube FET explained by interband tunneling [4]. The promise of a transistor that could outperform Si CMOS at low voltages attracted international attention and substantial research investments over almost a dozen years. The list of semiconductor materials and structural embodiments explored experimentally is

extensive: Si, Ge, SiGe, III-Vs, III-Ns, 2D materials, mixed heterojunctions, n-TFET, p-TFETs, pillars, nanowires, ribbons, tubes, vertical tunneling, lateral tunneling, and more. A similar breadth of exploration has taken place in theory and design to seed these device developments and interpret the measured device characteristics.

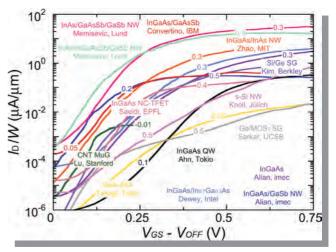

Selected best reported transfer characteristic of the n-TFETs across materials systems are shown in the accompanying figure 2 [1]. These TFETs were selected to show performance at drain voltages less than or equal to 0.5 V (where they would be expected to operate). To be included here the transistors also needed to exhibit subthreshold swing less than 60 mV/dec over at least one order of magnitude in drain current. Across materials systems, it can be seen that the direct-bandgap III-V materials have demonstrated the highest current drives. In comparison with CMOS, the currents are about an order of magnitude lower than desired to outperform Si at similar voltages. Indirect-bandgap materials such as Si and Si/Ge exhibit still smaller currents since phonons are required to enable the tunneling transitions, lowering the tunneling rates. Steep swings in 3D Ge/2D MoS, and carbon nanotubes are also a part of this comparison.

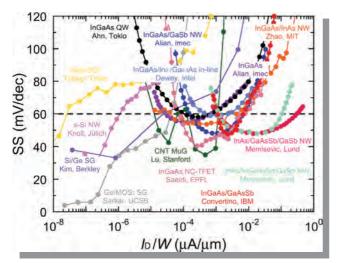

The corresponding subthreshold swings as a function of drain current/width is shown in the companion figure 3. One would like the voltage ( $V_{60}$ ) at which the subthreshold swing becomes less than 60 mV/dec to occur at a drain current of about 1  $\mu$ A/ $\mu$ m and then to stay below 60 mV/ dec for about 4 decades. The current at  $V_{60}$  is denoted  $I_{60}$ .

Figure 1. Schematic energy band diagram and cross sections of the tunnel FET.

Figure 2. Comparison of selected published n-TFET transfer characteristics. The numbers on the plots are the drain/source voltages. The curves have been shifted to put the current minimum at 0 V. References are given in [1].

Figure 3. TFET subthreshold swing versus drain current for the n-TFETs shown in figure 2 [1].

The III-V channel materials show an  $I_{60}$  approaching the desired 1  $\mu$ A/ $\mu$ m, and show steep swing for more than 2 decades. The lower limit on this behavior is attributed to trap-assist tunneling, a leakage mechanism whereby electrons from the source valence-band tunnel into traps in the channel traps (surface or bulk) and then are thermally-emitted to the conduction band. Group-IV-containing materials have generally shown lower leakages and this has led to more extended ranges over which the subthreshold swing stays below 60 mV/decade.

While new applications can drive technology development, benchmarks are useful to focus development. For the n-TFET the performance targets which would constitute clear measures of progress relative to the Si n-MOS-FET are: drain current exceeding 200  $\mu$ A/ $\mu$ m at voltages less than or equal to  $V_{\rm DS} = V_{\rm GS} = 0.4$  V, with  $I_{60} = 1 \ \mu$ A/ $\mu$ m and maintaining steep subthreshold swing over more than 4 decades. Other measures of progress are the development of a path to a complementary technology and to entry into manufacturing at the leading technology nodes.

To reach these ends will require fundamental studies in materials and devices. Much progress has been made on TFETs, but it is spread widely across semiconductor materials and heterojunctions. Community focus still awaits motivating experimental and theoretical direction. In any particular materials system, how is the abrupt tunnel junction doped, what limits the doping density and abruptness, what is the origin of the band tails, what is the preferred MOS stack and what are the interfacial defects, bulk traps, and border traps? Perhaps there are composite transistor structures that enable TFET operation when the device is operated at low voltages, but enable MOSFET action at high voltages. Perhaps there will be discoveries at the angstrom technology nodes that provide new approaches. Perhaps there are collective mechanisms in complex dielectrics that can be utilized to lower swing without introducing hysteresis. There are many avenues for breakthroughs.

In 1976, approaching the 30-year anniversary of the transistor, William Shockley was asked to write a paper about how the first transistors were conceived and brought to demonstration [2]. A key finding for him in writing this paper was surprisingly "how slow he was and how he missed the junction transistor's key concepts so many times." His message to readers facing conceptual and technical challenges was to "stick with it and not give up." This is clearly a message relevant to TFETs. Experiments show the technical gaps. New solutions are needed to enable manufacturing and commercialization. There are reasons to keep thinking about TFETs.

#### References

[1] P. Paletti and A. Seabaugh, "Heterojunction tunnel fieldeffect transistors," in Springer Handbook of Semiconductor Devices, ed. by M. Rudan, R. Brunetti, and S. Reggiani, 867-903, 2023.

[2] A. C. Seabaugh and Q. Zhang, "Low-voltage tunnel transistors for beyond CMOS logic," *Proc. IEEE*, vol. 98, 2095-2110, 2010.

[3] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy-efficient electronic switches," *Nature*, vol. 479, 329– 337, 2011.

[4] P.-F. Wang, T. Nirschl, D. Schmitt-Landsiedel and W. Hansch, "Simulation of the Esaki-tunneling FET," *Solid-State Electronics*, vol. 47, pp. 1187-1192, 2003.

[5] P.-F. Wang, K. Hilsenbeck, T. Nirschl, M. Oswald, C. Stepper, M. Weis, D. Schmitt-Landsiedel and W. Hansch, "Complementary tunneling transistor for low power application," *Solid-State Electronics*, vol. 48, 2281-2286, 2004.

[6] K. K. Bhuwalka, J. Schulze and I. Eisele, "Performance enhancement of vertical tunnel field-effect transistor with SiGe in the  $\delta$ p+ layer," *Jap. J. Appl. Phys.*, vol. 43, 4073-4078, 2004.

[7] J. Appenzeller, Y.-M. Lin, J. Knoch and P. Avouris, "Bandto-band tunneling in carbon nanotube field-effect transistors," *Phys. Rev. Lett.*, vol. 93, 196805, 2004.

[8] W. Shockley, "The path to the conception of the junction transistor," *IEEE Trans. Electron Devices*, vol. 23, 597–620, 1976.

## 75 YEARS OF COMPACT MODELS: FROM SHOCKLEY TO STICKER SHOCK

Colin C. McAndrew, Life Fellow, IEEE and Laurence W. Nagel, Life Fellow, IEEE C. C. McAndrew is with NXP Semiconductors, Chandler AZ 85224 USA L. W. Nagel is with Omega Enterprises Consulting, Kensington CA 94708 USA

#### I. Introduction

Today, everyone knows what a "compact" model (a.k.a. a SPICE model [1]) is: an analytical model, hopefully both accurate and computationally efficient, of a (semiconductor) device that is implemented in a circuit simulator and is used for the design of circuits, especially of integrated circuits (ICs).

The archetypical compact model is the Shockley equation for current in a *pn*-junction diode [2]

$$I = I_s \left( exp\left(\frac{V}{\phi_t}\right) - 1 \right)$$

<sup>(1)</sup>

where *V* is the voltage across the diode,  $\phi_t$  is the thermal voltage, and  $I_s$  is the "saturation current," which can be calculated from physical and structural parameters.

Simplified compact models are also used by professors to teach the basics of how devices work, and by designers to form mental images of how devices work, to help them innovate new circuits.

The size, complexity, and expectations (yield, reliability, performance, power consumption) of ICs have increased exponentially for many years—Moore's Law—which has led to a concomitant increase in expectations of the capabilities of computer-aided design (CAD) tools, like SPICE, and the compact models in those tools [3], [4].

Here, we give a brief overview of the trajectory of compact models since the invention of the transistor.

Nomenclature: *q* is the elementary charge, *k* the Boltzmann constant, *T* is temperature in Kelvin,  $\phi_t = kT/q$ ,  $\mu$  is mobility,  $V_{_{AB}}$  is the voltage between terminals *A* and *B*.

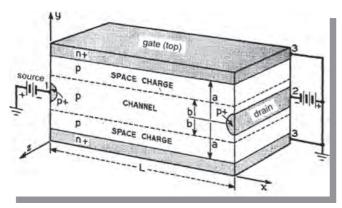

Figure 1. Fig 1 of [5], from 1952, which shows the device abstraction used for Shockley's analysis (terminal labels added).

# II. The JFET: A Compact Model Leads the Revolution!

Perhaps the most amazing feat ever in compact modeling was from the master himself: In 1952, Shockley [5] proposed what today we call a JFET, based on what today we call a compact model. The formulation, analysis, and simplifications adopted by Shockley are eerily reminiscent of the generic approach used today for compact models. The most incredible feature of this work was that it *developed a compact model to propose a new form of transistor which did not exist.*

Today, technology computer-aided design (TCAD), which solves the basic partial differential equations that model semiconductor behavior, is commonly used to help investigate proposed device structures. TCAD did not exist in Shockley's day; that he developed a compact model to understand and explain his proposed device is sheer genius.

Another proposal from that paper still permeates our industry. For the terminal names for his (theoretical, not experimentally verified) "unipolar field-effect transistor:"

The choice selected is "source" for the electrode through which the carriers flow into the channel, "drain" for the electrode into which the carriers flow out of the channel, and "gate" for the control electrodes that modulate the channel.

But let us back up a bit.

Once the transistor was invented, the advantages of being solid-state (no energy hungry cathode heaters to boil off electrons, no vacuum sealed glass tubes to compromise reliability, especially under "robust" physical perturbation) were sufficient to pique interest despite its (initially) high cost. However, to move from being a research laboratory breakthrough to being a commercial success, transistors needed to be used in products.

This meant circuit designers needed to mentally understand how transistors worked, and have some form of capability to do "back of the envelope" (SPICE would not arrive for over two decades) calculations to understand how their circuits behaved, and how to properly design and optimize component values and biasing in their circuits.

The reference for this is the classic "Electrons and Holes in Semiconductors" (with the important subtitle "with applications to transistor electronics") by Shockley [2]. Many of us older semiconductor engineers considered this the "bible," and cut our teeth digesting it. And many early transistor circuits were designed based on the mental images, i.e., models, espoused in that book.

However, the emphasis in [2] is more on the detailed physics of transistor and *pn*-junction operation than on the key aspects of device behavior, in essence large-signal behavior (from which DC operation and small-signal behavior naturally follow), that are critical to understand transistor behavior to enable circuit design.

#### III. A Side-Track Into Circuit Simulation

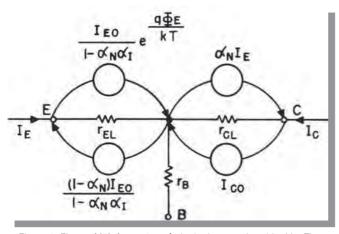

As mentioned previously, the concept of a compact model was introduced more than ten years before computer programs to analyze circuit performance appeared. The original purpose of the compact model was to encapsulate the operational features of a new device and to assist engineers to design circuits that employed that new device. A requirement of these compact models was that they had to be fairly simple and any accompanying equations had to be amenable to evaluation with a slide rule or a calculator. Because compact models were intended to assist engineers with circuit design, it is not surprising that these models were schematic representations of the device, as opposed to lengthy equations. The classic example of this type of compact model is the Ebers-Moll BJT model, published by Bell Laboratories researchers J. J. Ebers and J. L. Moll in 1954 [6], see Fig. 2.

Compact modeling changed drastically with the arrival of circuit analysis programs in the 1960's, followed by the evolution of circuit simulators in the 1970's. Early circuit analysis programs include ECAP from IBM [7] and NET-1 from the Los Alamos National Lab [8]. At about the same time, R. K. Jensen published a paper describing his implementation of the Ebers-Moll model, in ECAP, for DC and transient analysis [9].

Figure 2. Fig. 5 of [6], from 1954.  $\phi_{\rm E}$  is the base-emitter bias  $V_{\rm BE}$ . The quantities subscripted O are parameters,  $\alpha_{\rm N}$  and  $\alpha_{\rm I}$  are normal (forward,  $l_{\rm C}/l_{\rm E}$ ) and inverted (reverse,  $l_{\rm F}/l_{\rm C}$ ) current "gains."

Combining circuit simulators and compact models had an immense effect on the design community. On the one hand, simplicity was not as relevant, since it was no longer the designer who had to evaluate the device equations. Compact models could therefore include greater complexity to provide a more physical representation of the device. On the other hand, including compact models in a circuit simulator proved to be a difficult task. Simulation algorithms require that the device equations for current, charge, and flux be continuous with respect to voltage, and the algorithms work better if the first derivatives are continuous as well. There is also the tradeoff of accuracy of a model versus the computational complexity of the model. Finally, compact modeling came to require a reasonable knowledge of how circuit simulators work and how to implement a model in a simulator. This was a daunting task for circuit designers and device physicists who were unfamiliar with computer programming. These issues persist in the compact modeling world to this day.

#### **IV. Empirical Compact Models**

Notwithstanding the pioneering *pn*-junction diode and JFET models from Shockley, when it came to the bipolar junction transistor (BJT, which Shockley invented after the point-contact transistor of Bardeen and Brattain 75 years ago), the theory lagged a bit.

Experimentally, it was observed that the collector current  $I_c$  of a BJT was (closely) proportional to the emitter current  $I_e$  over many orders of magnitude of current; the ratio of those currents is now universally known as the quantity  $\alpha$ . This observation, along with the Shockley relation (1), was the basis of the Ebers-Moll BJT model [6]. While the Ebers-Moll model was, for its time, quite "physical," through the lens of history it missed the fundamental physics that underlies BJT operation.

Many data-driven approaches to modeling for circuit simulation have been, and continue to be, used. These include interpolation, a.k.a. table-based, models [10], and neural networks [11]. In the power RF community such approaches are considered to be "compact" models [12]; in the broader IC design community they are not [13].

#### V. Physical Compact Models: Hermann Gummel Sets the Path to the Future

While empirical compact models can be quick to generate, they have some drawbacks; it is difficult to include

- global statistical variation

- local statistical variation (i.e., parametric mismatch)

- geometric scaling, including layout dependent effects (LDEs)

- · temperature variation, including self-heating

- fundamental requirements like smoothness, monotonicity, and symmetry

For these reasons, compact models based on physical (structural and layout) parameters and physics-based

analysis are today the norm, and in fact all industry standard models from the Compact Model Coalition (CMC) [14] are physical, not empirical, compact models.

The guiding light, the archetype, for all modern compact models is the Gummel-Poon (GP) model for BJTs [15], which is based on the Gummel integral charge-control relation (ICCR) [16]. The collector-emitter transport current is

$$I_{CE} = A_E \frac{q n_i^2 \phi_t \mu}{t_B N_B} \frac{exp\left(\frac{V_{BE}}{\phi_t}\right) - exp\left(\frac{V_{BC}}{\phi_t}\right)}{q_B}$$

(2)

where  $A_{E}$  is the emitter area,  $n_{i}$  is the intrinsic concentration, and  $t_{B}$  and  $N_{B}$  are the thickness and doping of the base, respectively. The normalized base charge  $q_{B}$  (details not shown) embodies both modulation by the bias dependence of the depletion region edges in the base (the Early effect [17]) and modulation by highlevel injection.

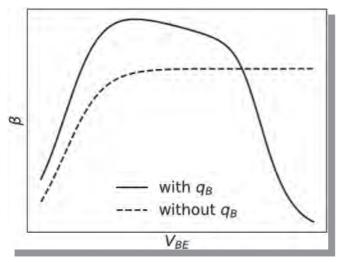

Figure 3 shows the effect of  $q_{B}$ ; how this is included in modern BJT models was pioneered in [15], which was a work of sheer genius.

Once you understand (2) you understand how BJTs work. That is the power of a physical, intuitive, compact model.

#### VI. MOS Transistor Compact Models

Given the importance of CMOS technology today, it is perhaps surprising how long, tortured, and fractured the development path is to modern MOS transistor models.

MOS transistors come in several flavors, including: bulk (planar), silicon-on-insulator (SOI), dual-gate, tri-gate, and gate-all-around (a.k.a. nanowire or nanosheet) transistors. The basic operation of all is the same: an electric

Figure 3. BJT current gain  $\beta = l_c/l_B$  from (2) with and without the  $q_B$  term included. The behavior with  $q_B$  is physically correct, the behavior without  $q_B$ , which is exhibited by the empirical Ebers-Moll model, is not physically correct.

field (from the applied gate bias) transverse to the surface, whatever the device structure, induces a conducting channel, and a longitudinal electric field (from the applied drain-source bias  $V_{\rm DS}$ ) drives current through the induced conducting channel.

There are 5 general classes of MOS transistor models:

- threshold voltage ( $V_{\tau}$ ) based models

- inversion charge based models

- surface potential based models

- the virtual source (VS) model

- the Taur approach for dual-gate MOS transistors

The first of these is probably the most familiar, as it is how MOS transistor operation is taught in most undergraduate classes and design textbooks. From [18] the drain current in a planar MOS transistor is

$$I_{D} = \frac{\mu C'_{ox} W}{2L} \{ [V_{GS} - V_{T} (V_{SB})]^{2} - [V_{GD} - V_{T} (V_{DB})]^{2} \}$$

(3)

where *W* and *L* are the transistor length and width, respectively,  $C'_{ox}$  is the oxide capacitance per unit area, and  $V_{\tau}$  is the threshold voltage, which depends on the voltage w.r.t. the body. The BSIM4 model [19] represents the pinnacle of development of  $V_{\tau}$  based models, and has been used for the design of more ICs than any other MOS transistor model. However, the drain/source symmetry inherent in (3) was lost over the years, which caused significant issues for simulation of RF CMOS circuits, so  $V_{\tau}$ -based models have fallen out of favor.

Models based on the (normalized) inversion charge density  $q_i$  have been independently developed multiple times, starting in 1987 [20], and culminating in BSIM-BULK [21]. From the 10,000 m level, this approach posits that

$$|q_i| + ln(|q_i|) \propto V_p - V_{ch}$$

(4)

where  $V_p$  is the pinchoff voltage and  $V_{ch}$  is the "channel" voltage. The beauty of this formulation is that it naturally transistions from the approximate exponential variation of  $q_i$  with gate bias in weak inversion to the near linear variation in strong inversion.

The surface potential approach is generally recognized as the most physically accurate formulation for MOS transistor modeling, and is also the basis of the CMC standard model for FinFETS [22]. It is too complex to summarize here, interested readers can digest the overview of [23].

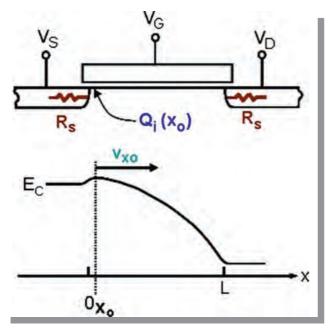

A rather different approach to modeling MOS transistors is the "virtual source" formulation [24]. All FET models assume there is no recombination in the channel. Therefore, the product of the inversion charge density  $Q_i(x)$  and the average carrier speed v(x) must be the same at every point along the channel. So, you only need to model those quantities at one point along the channel to characterize the behavior of the whole transistor. Fig. 4 shows how this approach works:  $x_a$  is the position along the channel of the virtual source, so  $Q_i$  and v at that point are used to model  $I_D$ .

An innovative approach to modeling dual-gate transistors was pioneered by Yuan Taur [25]. This approach, unlike the other approaches listed above, has not been adopted in any CMC standard model. But it is so different, and so elegant, it warrants attention.

Amazingly, most modern MOS transistor compact models (the exception being the VS model) are based on the "gradual channel approximation," which was first introduced by Shockley for JFETs [5]. In a nutshell, this posits that to solve Poisson's equation for the charge density in the channel, the longitudinal electric field can be ignored, and only the transverse electric field need be considered. Corrections for the inaccuracies of this approximation have been investigated [26], but the fundamental approximation of [5] is still the basis of modeling for all FETs.

#### VII. Compact Models for Other Devices

The models briefly outlined above are relatively simple. Probably the most complex devices to model are LDMOS transistors, for which modeling of the drift region, which allows them to sustain the high voltages necessary to interface to the real world, is at least as complex as modeling the core MOS transistor. The low-voltage digital circuits in our cars and phones have to interact with the real world at some point, and in many cases LDMOS transistors are the interface.

Even what we consider to be basic, simple devices such as capacitors and inductors are neither basic nor simple in modern ICs: their layouts are increasingly complex, and accuracy requirements for the models,

Figure 4. Fig. 1 of [24], virtual source view of MOS transistor operation.

over layout and frequency, continually escalate ... if they didn't, your phone battery may die faster than it already does!

Even resistors are not simple: As undergraduates we are all indoctrinated that  $V = I \cdot R$ , but integrated resistors are a bit more complex than that: their behavior is affected by depletion pinching, velocity saturation, and self-heating, and they are really JFETs [27].

#### VIII. Why Compact Models are Always Playing "Catch-up"

Compact models are vastly more accurate today than they were 75 years ago. But they are still imperfect; in several aspects embarrassingly so for model developers. With the increasing importance of LDEs and parasitics, and the inability of models to keep up with the cadence of technology development in these areas, there will always be "unsimulatable" effects.

The expectations of how accurate compact model are have continued to escalate, yet the gaps between simulation and reality, especially for compact models, have never been closed as more physical effects come into play and accuracy requirements have become more demanding. The Shichman-Hodges MOS transistor model [18] was revolutionary 50 years ago, but is completely inadequate for today's needs. As technology continues to scale, what "fine details" of modeling bubble up to be make-or-break capabilities continue to evolve.

The expectations for compact models today are much, much more stringent than they were 75 years ago. Circuits have 10<sup>8</sup> more components, supply voltages are significantly smaller so sensitivity to variability is much greater, sensitivity to inaccuracies in models is vastly higher, and many more circuit performance characteristics are important. The capabilities of simulators and compact models have improved astronomically, but the complexity of the circuits that are simulated, and the expectations of the accuracy of those simulation results, have increased at a greater rate. So, basically, the algorithms and models in SPICE are continually playing catch-up.

The reality is that simulation algorithms and compact models have, despite huge steps forward, struggled to keep pace with the increasing expectations of how accurate they should be.

This is not a problem for expert IC designers. It is a huge problem, recognized in both industry and academia, for the "SPICE jockeys" who blindly run, and trust, SPICE simulation results. *There is no substitute for knowledge of how circuits operate and of physical understanding of how devices behave.*

#### Acknowledgment

An extended version of this article will appear in the commemorative volume, **75th Anniversary of the Transistor**, IEEE Press-Wiley, 2023.

#### References

[1] L. W. Nagel, *SPICE2, A Computer Program to Simulate Semiconductor Circuits.* PhD thesis, EECS Department, University of California, Berkeley, May 1975.

[2] W. Shockley, *Electrons and Holes in Semiconductors* (*With Applications to Transistor Electronics*). New York, NY, USA: Van Nostrand, 1950.

[3] L. W. Nagel and C. C. McAndrew, "Why SPICE is just as good and just as bad for IC design as it was 40 years ago," in 2018 48th European Solid-State Device Research Conference (ESS-DERC), pp. 170–173, 2018. DOI: 10.1109/ESSDERC.2018.8486875.

[4] L. W. Nagel and C. C. McAndrew, "Is SPICE good enough for tomorrow's analog?," in 2010 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM), pp. 106–112, 2010. 10.1109/BI-POL.2010.5668096.

[5] W. Shockley, "A unipolar "field-effect" transistor," *Proc. IRE*, vol. 40, pp. 1365–1376, Nov. 1952. DOI: 10.1109/JR-PROC.1952.273964.

[6] J. J. Ebers and J. L. Moll, "Large-signal behavior of junction transistors," *Proceedings of the IRE*, vol. 42, no. 12, pp. 1761–1772, 1954. DOI: 10.1109/JRPROC.1954.274797.

[7] "1620 electronic circuit analysis program (ECAP)," Tech. Rep. 1620-EE-02X, IBM Corporation.

[8] A. F. Malmberg, F. L. Cornwell, and F. N. Hofer, "NET-1 network analysis program," Tech. Rep. LA-3119, Los Alamos Scientific Laboratory, 1964.

[9] R. W. Jensen, "A charge control transistor model for the IBM circuit analysis program," *IEEE Transactions on Circuit Theory*, vol. 13, pp. 428–437, Dec. 1966.

[10] J. Barby, J. Vlach, and K. Singhal, "Polynomial splines for MOSFET model approximation," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, vol. 7, no. 5, pp. 557–566, 1988. DOI: 10.1109/43.3193.

[11] A. Zaabab, O.-J. Zhang, and M. Nakhla, "A neural network modeling approach to circuit optimization and statistical design," *IEEE Transactions on Microwave Theory and Techniques*, vol. 43, no. 6, pp. 1349–1358, 1995. DOI: 10.1109/22.390193.

[12] D. E. Root, J. Xu, F. Sischka, M. Marcu, J. Horn, R. M. Biernacki, and M. Iwamoto, "Compact and behavioral modeling of transistors from NVNA measurements: New flows and future trends," in *Proceedings of the IEEE 2012 Custom Integrated Circuits Conference*, 2012. DOI: 10.1109/CICC.2012.6330642.

[13] C. C. McAndrew, "A perspective on RF modeling," in *IEEE 16th Topical Meeting on Silicon Monolithic Integrated Circuits in RF Systems*, pp. 84–87, 2016. DOI: 110.1109/SIRF.2016.7445475.

[14] "Si2 compact model coalition." https://si2.org/cmc/. Accessed: Dec. 2022.

[15] H. K. Gummel and H. C. Poon, "An integral charge control model of bipolar transistors," *Bell Syst. Tech. J.*, vol. 49, pp. 827–852, May-Jun. 1970. DOI: 10.1002/j.1538-7305.1970. tb01803.x. [16] H. K. Gummel, "A charge control relation for bipolar transistors," *Bell Syst. Tech. J.*, vol. 49, pp. 115–120, Jan. 1970. DOI: 10.1002/j.1538-7305.1970.tb01759.x.

[17] J. M. Early, "Effects of space-charge layer widening in junction transistors," *Proceedings of the IRE*, vol. 40, no. 11, pp. 1401–1406, 1952. DOI: 10.1109/JRPROC.1952.273969.

[18] H. Shichman and D. A. Hodges, "Modeling and simulation of insulated-gate field-effect transistor switching circuits," *IEEE J. Solid-State Circuits*, vol. 3, pp. 285–289, Sep. 1968. DOI: 10.1109/JSSC.1968.1049902.

[19] N. Paydavosi, T. H. Morshed, D. Lu, W. Yang, M. V. Dunga, X. Xi, J. He, W. Liu, K. M. Cao, X. Jin, J. J. Ou, M. Chan, A. M. Niknejad, and C. Hu, "BSIM4v4.8.0 MOSFET Model Users' Manual." http://www2.eecs.berkeley.edu/Pubs/TechRpts/1973/22871. html, 2013. Accessed: Sep. 2019.

[20] M. A. Maher and C. A. Mead, "A physical charge-controlled model for MOS transistors," in *Advanced Research in VLSI* (P. Losleben, ed.), Cambridge, MA, USA: MIT Press, 1987.

[21] H. Agarwal, C. Gupta, H.-L. Chang, S. Khandelwal, J. P. Duarte, Y. S. Chauhan, S. Salahuddin, and C. Hu, "BSIM-BULK106.2.0 MOSFET Compact Model Technical Manual." https:// bsim.berkeley.edu/models/bsimbulk/, 2017. Accessed: May 2020.

[22] S. Khandelwal, J. Duarte, A. S. Medury, S. V., N. Paydavosi, D. Lu, C. Lin, M. Dunga, S. Yao, T. Morshed, A. Niknejad, S. Salahuddin, and C. Hu, "BSIM-CMG 110.0.0 Multi-Gate MOSFET Compact Model Technical Manual." http://bsim.berkeley.edu/models/bsimcmg/, 2015. Accessed: May 2020.

[23] G. Gildenblat, W. Wu, X. Li, R. van Langevelde, A. J. Scholten, G. D.-J. Smit, and D. B. M. Klaassen, "Surface-potential-based compact model of bulk MOSFET," in *Compact Modeling: Principles, Techniques and Applications* (G. Gildenblat, ed.), ch. 1, pp. 3–40, New York, NY, USA: Springer, 2010. DOI: 10.1007/978-90-481-8614-3.

[24] A. Khakifirooz, O. M. Nayfeh, and D. Antoniadis, "A simple semiempirical short-channel MOSFET current-voltage model continuous across all regions of operation and employing only physical parameters," *IEEE Trans. Electron Devices*, vol. 56, pp. 1674–1680, Aug. 2009. DOI: 10.1109/TED.2009.2024022.

[25] Y. Taur, X. Liang, W. Wang, and H. Lu, "A continuous, analytic drain-current model for DG MOSFETs," *IEEE Electron Device Letters*, vol. 25, pp. 107–109, Feb. 2004. DOI: 10.1109/ LED.2003.822661.

[26] K. Mayaram, J. Lee, and C. Hu, "A model for the electric field in lightly doped drain structures," *IEEE Transactions on Electron Devices*, vol. 34, no. 7, pp. 1509–1518, 1987. DOI: 10.1109/ T- ED.1987.23113.

[27] K. Xia and C. C. McAndrew, "JFETIDG: a compact model for independent dual-gate JFETs with junction and MOS gates," *IEEE Trans. Electron Devices*, vol. 65, pp. 747–755, Feb. 2018. DOI: 10.1109/TED.2017.2786043.

## TECHNICAL BRIEFS

## THIRD BREAKDOWN: A PHYSICAL MECHANISM FOUND IN HIGH-K METAL-GATE CMOS

Steve S. Chung Chair Professor, National Yang Ming Chiao Tung University, Taiwan

There are two major well-known breakdowns, soft-breakdown and hard-breakdown, in MOSFET's history. Not until 2015, a world-first observation of the breakdown, different from the above two breakdowns, named dielectric fuse breakdown, **dFuse**, was discovered, as a result of CMOS technology moving into the 45 nm node High-k Metal-gate (HKMG) era. Here, we will describe how it was found and how to understand the physics underlying this breakdown mechanism.

#### 1. Introduction

In the history of the Metal-Oxide-Semiconductor Field Effect Transistor (MOSFET), the quality of its gate oxide has been a cornerstone of silicon-based semiconductor integrated circuits. The changes of gate dielectrics from conventional  $SiO_2$  gate oxide into high-k materials brought us more challenges to the transistor's reliability, especially when the MOSFET dimension is continually scaled.

At the beginning of 2000, the development of high-k dielectrics embarks a new era of the CMOS technology.

The purpose of high-k materials is to solve the leakage current through the transistor's gate [1]–[2]. This led us to further development of the gate stack towards a new era of the so-called high-k metal-gate (HKMG) CMOS generation. Namely, the rapid growth of high-end processors (CPU, GPU, and MCU) and industrial applications such as mobile phones, notebooks, and PAD, to mention a few [3], relies on the technology improvement or breakthrough of various high-quality gate stack films. Depending on the making of high-quality gate dielectrics, it will provide reliable, ultra-low power and low leakage, and high-end IC products.

In terms of the MOSFET's reliability, Time Dependence Dielectric Breakdown (TDDB) [4], Bias Temperature Instability (BTI), mobility degradation [5], stress-induced leakage current (SILC) [6], are major considerations, in which SILC has been a critical issue to the power consumption of CMOS devices. A huge number of published articles have stressed the importance of methods for suppressing the gate current in high-k dielectrics. Numerous highk materials have been investigated to further reduce the

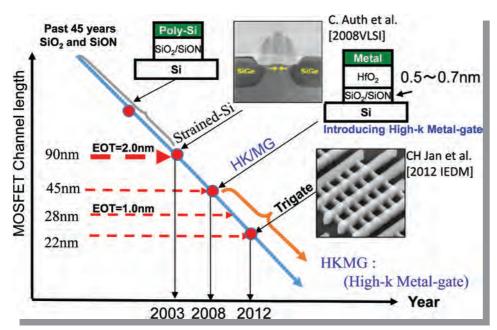

Figure 1. The scaling of MOSFET, courtesy from H. Iwai (TIT) and a redrawing.

gate leakage current through the improvement in making the interfacial layer between high-k materials and the Si substrate [7].These results led to the manufacturing of the HfO<sub>2</sub>-based dielectrics as the mainstream of gate dielectrics in advanced CMOS devices at 45 nm generation of CMOS technologies [2], see the trend of scaling in Fig. 1.

#### 2. Experimental Observations

A popular experimental method to examine the reliability of the gate dielectric in MOSFET is the so-called Time-Dependent Dielectric Breakdown (TDDB) [4] which is used to impose stress on the device and to accelerate the transistor's aging. It has a direct impact on the breakdowns that were observed. The most commonly used test methodology to conduct the TDDB is constant stress, which includes constant voltage stress or constant current stress. That is, a voltage or current is applied to the gate, while its leakage current is being monitored. The time for the oxide to reach breakdown is called the time-to-failure.

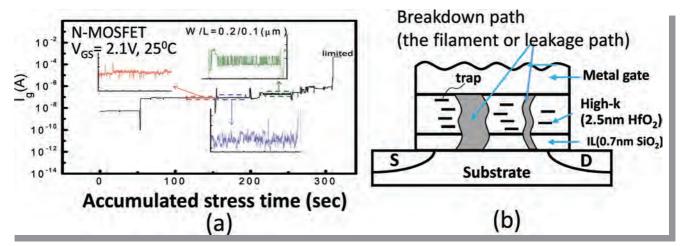

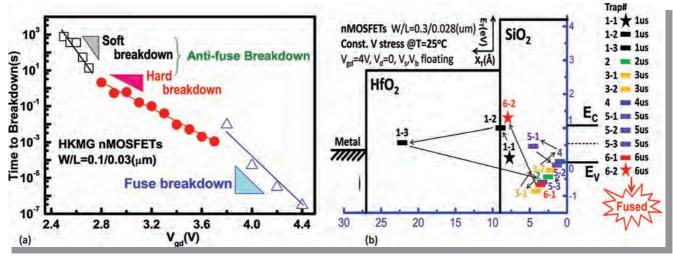

Fig. 2(a) is the experimental observation of the transient behavior (i.e., gate current) in the gate dielectric in a 28nm high-k MOSFET [9] under long-term stress of Positive Bias Temperature Instability (PBTI) (i.e., by applying voltage stress on the n-MOSFET with appropriate high temperature). This is to intentionally accelerate the transistor's aging. The gate dielectric has Equivalent Oxide Thickness (EOT) = 1.35 nm, composed of a HfO<sub>2</sub> with a thickness of 2.8 nm and a SiO, interfacial layer with a thickness of 1.2 nm. It was observed that there are several switching behaviors in the transient gate current, as in the inset of Fig. 2(b). These switching behaviors came from the interaction between electrons in the Si substrate and traps in the gate dielectric. In the beginning, the gate leakage is small, and then strong current noises are raised, i.e., soft-breakdown occurs. Eventually, the number of traps reaches a critical value, leading to a hard breakdown with a sudden increase in the current. This can be explained by the conceptual diagram in Fig. 2(b) where the breakdown path is assumed to be a percolation path of the traps, connecting together to form a filament, that is, a conduction path with traps nearby serving as a switch to control the current flow through the filaments. The trap location is responsible for the magnitude of the current flow.

#### 2. Fundamentals of Ig-RTN

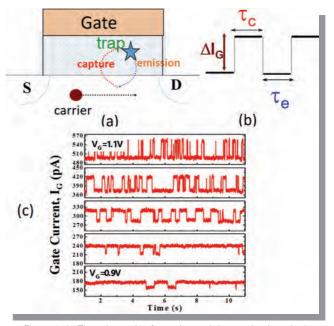

To understand the aforementioned noises in the percolation path, Random-Telegraph-Noise (RTN) measurement can be employed. RTN is a switching phenomenon of electrical characteristics in a transistor caused by the capture and emission of carriers by the oxide trap, as shown in Fig. 3(a), with two characteristic time constants,  $\tau_c$ , and  $\tau_e$ . A real measurement was given in Fig. 3(c), which was named as I<sub>g</sub> RTN measurement [10]–[11]. RTN signal, in the form of a repetitive digital waveform with two or more levels, depends on the number of traps [12]. In the following, we will examine first the properties of RTN traps in a high-k gate dielectric. The location of the traps in the MOSFET is strongly related to the conduction path in the gate dielectric, i.e., filament. Also, the conduction path is indirectly related to the breakdown.

Figure 3. (a) The schematic of trapping and de-trapping in a single RTN, (b) the definition of  $\tau_c$  and  $\tau_e$ , and (c) the measured two-level  $l_g$  waveforms.

Figure 2. The transient characteristics of TDDB stress-induced gate leakage current. Different RTN signals can be observed as stress time progresses. (b) A conceptual diagram to show the breakdown path caused by the leakage.

#### 3. The Concept of Leakage Path from Experiment

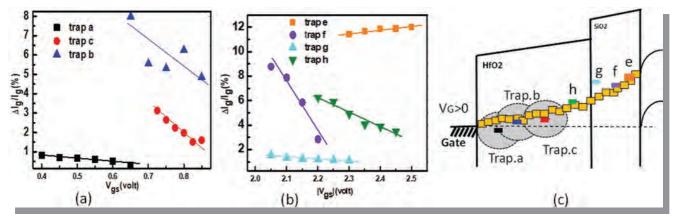

Once we have a measured two-level I current and its variation as a function of time at different V<sub>GS</sub> biases, we may calculate the normalized amplitude of variation of the gate current  $(\Delta I_a/I_a)$  for various traps, as shown in Fig. 4(a) in the inversion region. But, in the deeper region close to the Si channel region (i.e., inside SiO<sub>2</sub>), accumulation region traps in MOSFET can be measured as given in Fig. 4(b). Fig. 4(c) shows the location of the traps in the energy band diagram. Then, we may assume that a leakage path or filament is formed surrounding the generated traps. Moreover, the fluctuation of the gate current is affected by the trap position. For example, if the trap is very close to the path, the fluctuation will be very large, or it will be smaller when the trap is far away from the path. In this case, it is believed that trap a is closer to the path than that trap c. More importantly, the gate's current path can thereby be traced by the traps. As a result, as the stress time progresses, the gate leakage current path will grow near the traps in dielectrics and the gate current increases with larger amplitudes of fluctuations. In short, as long as we can identify the trap location from the gate through the dielectric and to the silicon substrate, we can always draw a leakage path or a synonym of filament which is responsible for the leakage current.

#### 4. Ig-RTN Transient Measurement Technique-Version 2.0

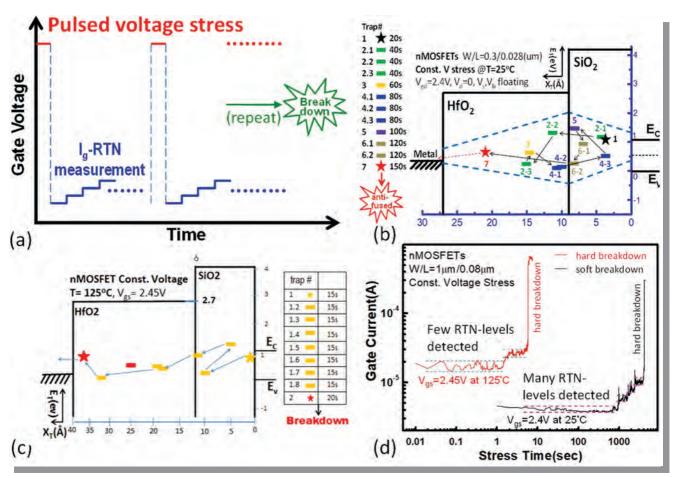

Fig. 5(a) shows the measurement setup, named Version 2.0  $I_g$ -RTN, i.e.,  $I_g$ -RTN transient measurement technique [14], which is used to profile the generation of traps as a function of time. First, the constant voltage was carried out and then held for performing  $I_g$ -RTN measurement [9] in order to detect the traps where ramped voltages were applied gradually. It was repeated until the dielectric went to breakdown. After gathering traps at a specific time, one can determine the physical location of the gen-

erated traps in the dielectric. It was continued until the dielectric reached breakdown.

First, as shown in Fig. 5(b), we applied a constant voltage stress on the MOSFET under  $V_{GS}$ = 2.4 V at room temperature, i.e. for  $V_{GS}$  voltage a little higher than the normal operating voltage  $V_{DD}$  (e.g., for a 28 nm CMOS technology,  $V_{DD}$ = 1.8 V). At 10 seconds, we could detect trap #1, close to the SiO<sub>2</sub> interface. After the next 10 seconds, the stress generated a 2nd trap, #1.2. After another 30 seconds, several traps, #2.1 and #2.2 were generated. We repeated the same procedure until the gate dielectric reached a breakdown. The total accumulated time is 660 seconds. The first few traps were generated near the interface of HfO<sub>2</sub> and SiO<sub>2</sub> and then circle around at this interface. Eventually, as time progresses further, it reaches a breakdown [9].

Next, the PBTI stress test is performed at  $V_{GS} = 2.45$  V and 125 °C, on the MOSFET of the same size. Fig. 5(c) demonstrates the experimental result of the constant voltage BTI-induced breakdown path. It shows a different path from the previous one (Fig. 5(b)), in which the trap was generated at the interface of SiO<sub>2</sub> and Si substrate, and then, most of the generated trap is a single trap. In a shorter time, it reached a breakdown. The latter is a hard breakdown (Fig. 5(c)) whereas the former one (Fig. 5(b)) is a soft breakdown. The former traps with longer time form a spindle shape filament (path). The latter exhibits a snake-walking behavior, named "snake path".

#### 5. The Discovery of a Third Breakdown: Dielectric-fuse Breakdown

Based on the above soft-breakdown and hard-breakdown that people usually understood, the transistor will go into soft-breakdown first and then be developed into a hard-breakdown for the gate dielectric to fail. This results in a short path between the gate and the source/ drain. However, in the measurement of Fig. 6(a), we applied a higher voltage and shorter duration of pulse on the MOSFET gate, i.e., a higher electric field across

Figure 4. (a) The normalized gate current induced by traps a, b, c, (b) the normalized gate current induced by traps e to h, (c) a leakage path drawn along traps.

Figure 5. (a) The experiment to extract the generated traps. (b) The evolution of traps versus stress time in n-channel MOSFET under the room temperature voltage stress. (c) The evolution of traps versus time under high-temperature PBTI stress. (d) The transient characteristics of two different types of leakage current. The black curve is a soft breakdown, while the red curve is a hard breakdown.

Figure 6. (a) The measured TDDB for three different breakdowns. (b) The evolution of traps versus stress time in n-channel MOSFET under higher constant voltage stress at V<sub>gd</sub>= 4 V (in the range of fuse breakdown). The leakage path did not create traps in reaching the metal gate (can be compared with Fig. 5(b)).

the high-k/interfacial gate dielectric, the gate dielectric became open and the gate current will be pulled down to a very low level (clockwise); on the other hand, it will be raised to a higher level, labeled as anti-fuse (counterclockwise), i.e., short. The latter, anti-fuse is the evidence of the hard-breakdown, consistent with Fig. 5(c) and (d), leading to an increase in the gate current after a breakdown. On the contrary, with an increase in applied voltages, the gate current dropped to a very low level. This is because during the process of trap generation, oxygen ions were annealed out and more oxygen vacancies were left at the interfacial layer. This led to a broken filament between the gate and drain, i.e., no current flowing through the gate, located inside the interfacial layer. As a consequence, after the burn-out of this interfacial layer, the SiO<sub>2</sub> layer exhibits a porous structure. Hence, we gave it a new name called third breakdown- dielectric fuse breakdown, dFuse [13].

After several TDDB tests, we can see the difference between three different breakdowns, as given in Fig. 6(a).

All three types of breakdown show different slopes in this time-to-breakdown plot. Obviously, the dFuse breakdown takes a shorter time in comparison to the hard-breakdown. To further understand the path development during the dielectric fuse breakdown, Fig. 6(b) shows the results after the dielectric fuse breakdown. Traps are generated at the interface of the high-k/interfacial layer (IL), in which we see the traps were generated and circled around in the IL layer and will not reach the gate for breakdown, which is different from Fig. 5(b). As a result, these IL traps create porosity in SiO<sub>2</sub> and eventually a gap to block the current path going through the gate dielectric. Thus, we see a sudden decrease in the gate current, as shown in Fig. 7(a) (blue-colored curves).

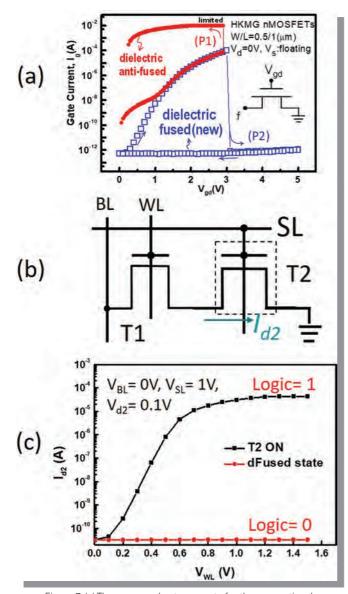

In short, the dielectric fuse, dFuse, breakdown that we observed can be achieved by applying across the gate-to-drain a *higher voltage but shorter pulse, or the same voltage as hard-breakdown but longer time,* to achieve breakdown.

By taking advantage of the observed dFuse breakdown, it may find application to the One-Time-Programming memory (OTP) [14], The architecture of an OTP as a unit cell, shown in Fig. 7(b), consists of a control transistor (T1) and a second transistor(T2) serving as storage. The write operation can be made by applying a pulse with 4.2V high voltage and 1 µsec duration to the T2, it causes damage to the gate dielectric and the gate has no control over the T2 channel with zero drain current. It provides a logic 0, in Fig. 7(c). If instead there is no damage on the T2 gate, the drain current will be read as a high-level current which represents logic 1. Since the gate dielectric is ruptured with a condition of dFuse, it creates a permanent failure of T2 from which T2 remains at logic 0 and could not be recovered. So, this kind of memory is named one-time programming. An example of the MACRO design can be found in [15].

In summary, the difference between hard/soft breakdown and dFuse is shown in the comparison of Fig. 8, in which the dielectric dFuse breakdown creates porosity of the interfacial layer ( $SiO_2$ ) and the burnout region is along the horizontal direction. The OTP provides us with several applications, in the IoT era, such as key encryption, device identity, code storage in mobile phones, power management in mobile phones, LCD drivers, and code storage in Micro Controller Units (MCU), to name a few.

#### 5. Summary and Conclusions

Since the inception of the first version DC  $I_g$ -RTN measurement technique that was developed in 2008 [10]–[11], it brought us more opportunities to understand the reliability of breakdowns, from soft-breakdown to hard-breakdown. Later, it led to the discovery of a third breakdown, named dielectric fuse breakdown, relying on a significant improvement of  $I_g$ -RTN transient in 2015 [13].

| INDE IN                                | Metal<br>HK<br>Si<br>Southerstates<br>Southerstates<br>Southerstates<br>Based of the second secon | 5 D                 | S D        |  |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------|--|--|

| Dielectric<br>Breakdown Fuse Breakdown |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Anti-fuse Breakdown |            |  |  |

| Mechanism                              | (porousness of SiO <sub>2</sub> )                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Hard                | Soft       |  |  |

| Field to<br>breakdown                  | >38(MV/cm)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 38~27(MV/cm)        | <27(MV/cm) |  |  |

| Time to<br>breakdown                   | <1ms                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Few 10s~1ms         | >few 10s   |  |  |

Figure 8. The comparison between dFuse breakdown and anti-fuse (hard- and soft-breakdown).

As a consequence, we will be able to distinguish three different types of breakdown. In addition, both the first DC version and version 2.0 I<sub>g</sub>-RTN measurement techniques allow us to understand the reliability physics underlying the ever-increasing leakage in HKMG CMOS as the scaling of transistors continues. In addition to the understanding of physics, the dFuse that was unveiled here will soon find broader applications in the hardware security design, such as the OTP [15], Physical Unclonable Function (PUF) [16] and for use in mobile phones and MCU, such as power management, cryptography, key generation, encryption, etc. More details of the experimental implementations can be found in [17].

#### Biography

**Steve Chung** received the Ph.D. degree in Electrical Engineering from the University of Illinois at Urbana-Champaign, Champaign, IL, USA. His Ph.D. advisor was the world famous CMOS co-inventor, Prof. C.T. Sah.

Currently, he is NYCU and UMC Chair Professor at the National Yang-

Ming Chiao Tung University (NYCU). He has been the Dean of International Affairs Office and Executive Director of school level research center, (2007–2008). He was a visiting professor with Stanford University, University of California-Merced, between 2001–2009 successively. He has been the consultant of two world largest IC foundries, TSMC and UMC. His recent research areas include: Fin-FET, flash memory, resistance MemoryTechnologies, from storage to Al application. He has performed more than 35 times of in-person presentations in IEDM/VLSI and holds more than 40 patents. He is an IEEE Life Fellow, IEEE Distinguished Lecturer, Senior Editor of Applied Physics-A (Springer), EDS Taipei chapter chair, and with past involvements as IEEE EDS Board of Governor for more than 12 years, EDS Regions/Chapters Chair, and Editor of J-EDS, EDL(2002–2008). Among numerous awards, he has been a recipient of 3-times Outstanding Research Award(NSC), *Pan Wen Yuan award* (2013), Lifetime achievement award as National Inventors (2019), etc.

#### References

[1] R. Chau, S. Datta, M. Doczy, J. Kavalieros, M. Metz, "Gate dielectric scaling for high-performance CMOS: from SiO<sup>2</sup> to high-K," in *Int'l Workshop on Gate Insulator*, doi: 10.1109/ IWGI.2003.159198, Dec. 2003.

[2] K. Mistry, C. Allen, C. Auth, B. Beattie, et al., "A 45nm Logic Technology with High-k+Metal Gate Transistors, Strained Silicon, 9 Cu Interconnect Layers, 193nm Dry Patterning, and 100% Pb-free Packaging," in *IEDMTech. Dig.*, pp. 247-250, Dec. 2007.

[3] T. Smith, https://www.theregister.com/2007/01/27/intel\_45nm \_metal\_gates/, (2007).

[4] A. Elhami Khorasani, M. Griswold, T. L. Alford, "A Fast I-V Screening Measurement for TDDB Assessment of Ultra-Thick Inter-Metal Dielectrics". IEEE Elec. Dev. Lett., Vol. 35, 117–119, 2014.

[5]T Ando,T Shimura, H Watanabe,T Hirano, S Yoshida, et al., "Mechanism of carrier mobility degradation induced by crystallization of HfO<sup>2</sup> gate dielectrics," Applied Physics Express 2 (7), 1402, 2009.

[6] E. Rosenbaum and L. F. Register, "Mechanism of stressinduced leakage current in MOS capacitors," IEEE Trans. Elect. Devices vol. 44, pp. 317-323, 1997.

[7] J. H. Chen, T. B. Huang, X. Wu, D. Landheer, T. F. Lei, and T. S. Chao, "Performance Improvement of CoTiO3 High-k Dielectrics with Nitrogen Incorporation," J. ECS, vol. 154, pp. G18-G23, 2007. [8] B. Kaczer, T. Grasser, Ph. J. Roussel, J. Franco, R. Degraeve,

L.-A. Rabnarsson, E. Simon, G. Groeseneken, and H. Reisinger,

"Origin of NBTI variability in deeply scaled pFETs," in *2010 IEEE Int. Reliability Physics Symp. (IRPS)*, pp. 26-32, (2010).

[9] E. R. Hsieh, P.Y. Lu, S. S. Chung, K.Y. Chang, C. H. Liu, J. C. Ke, C. W. Yang, and C. T. Tsai, "The experimental demonstration of the BTI-induced breakdown path in 28nm high-k metal gate technology CMOS devices," in *Symp. VLSI Tech.*, pp. 132-133, 2014.

[10] C. M. Chang, S. S. Chung, Y. S. Hsieh, L. W. Cheng, C. T. Tsai, et al, "The observation of trapping and detrapping effects in high-k gate dielectric MOSFETs by a new gate current Random Telegraph Noise (IG-RTN) approach, " in *IEDMTech. Dig.* pp. 787-790, 2008.

[11] S. S. Chung and C. M. Chang, "The investigation of capture/emission mechanism in high-*k* gate dielectric soft breakdown by gate current random telegraph noise approach," Applied Physics Lett., 93, 21, p. 3502, 2009.

[12] E. R. Hsieh, Y. L. Tsai, S. S. Chung, C. H. Tsai, R. M. Huang, and C. T. Tsai, "The understanding of multi-level RTN in trigate MOSFETs through the 2D profiling of traps and its impact on SRAM performance: A new failure mechanism found," in *IEDM Tech. Dig.*, pp. 454-457, 2012. [13] E. R. Hsieh, Z. H. Huang, S. S. Chung, R. M. Huang, C. T. Tsai, and T. R. Yew, "The demonstration of low-cost and logic process fully-compatible OTP memory on advanced HKMG CMOS with a newly found dielectric fuse breakdown," in *IEDM Tech. Dig.*, pp. 52-55, 2015.

[14] S. S. Chung, E. R. Hsieh, and Z. H. Huang, One-Time-Programmable Memory Cell and Its Array Circuits, US Provisional document, No. 62/198,666, July 29, 2015.

[15] E. R. Hsieh, C. W. Chang, C. C. Chuang, H. W. Chen, and S. S. Chung, "The Demonstration of Gate Dielectric-fuse 4kb OTP Memory Feasible for Embedded Applications in High-k Metalgate CMOS Generations and Beyond," in *Symp. VLSI Technol., Tech. Dig.*, pp. 52-53, 2019.

[16] W. C. Wang, C. C. Chuang, C. W. Chang, E. R. Hsieh, H.W. Chen, and S. S. Chung, "A Novel Complementary Architecture of One-time-programmable Memory and Its Applications as Physical Unclonable Function (PUF) and One-time Password," in *IEDM Tech. Dig.*, San Francisco CA, Dec. 12-16, 2020.

[17] S. S. Chung, "The discovery of a third breakdown: phenomenon, characterization and applications," Applied Physics-A, https://doi.org/10.1007/s00339-023-06383-w, Jan. 17, 2023.

## UPCOMING TECHNICAL MEETINGS

## IEEE SYMPOSIUM ON VLSI TECHNOLOGY AND CIRCUITS RETURNS TO KYOTO, JAPAN

The 2023 IEEE Symposium on VLSI Technology and Circuits will be held on 11–16 June at the Rihga Royal Hotel, Kyoto, Japan, as an in-person format with on-demand content to deliver on the exciting theme of "Rebooting Technology and Circuits for a Sustainable Future." The 43rd Symposium is jointly sponsored by the IEEE Electron Devices Society (EDS) and IEEE Solid-State Circuits Society (SSCS) as well as the Japan Society of Applied Physics (JSAP).

VLSI Symposium is the premier global venue that promotes synergies between technologists and designers on today's applications and future breakthroughs. From process integration and advanced device architectures to circuit designs and systems, the Symposium covers innovations in a wide range of domains such as artificial intelligence, connected objects, autonomous vehicles, and biomedical applications. To facilitate these interactions, this year's Symposium will offer joint-interest sessions on special areas of Technology and Circuits such as AR/ VR/MR/Metaverse and its integration, aerospace applications, BEOL interconnects and BPD/BSPDN, more novel memory devices to continue scaling, new computing, 3D package technologies and system integration.

Four plenary talks by distinguished industry leaders will open the Symposium:

- Surya Bhattacharya (Director, A\*STAR IME)

- Partha Ranganathan (Vice President, Google)

- Siva Sivaram (President, Western Digital)

Hiroyuki Mizuno (Distinguished Researcher, Hitachi) The two evening panel discussions will focus on the sustainability of VLSI. What is scalable and sustainable in the next 25 years? How can we reboot industry-academia joint research for a sustainable VLSI future? The Symposium will offer two full-day short courses prior to the technical sessions to prepare participants on Advanced CMOSTechnologies for 1 nm & Beyond as well as on Future Directions in High-Speed Wireline and Optical IO.The Symposium will conclude with a full-day Forum focused on Compute Paradigms for Secured Microelectronics and Combinatorial Optimization. The Symposium program also includes a lively demo session and is complemented by six workshops on research and application topics.

We cordially invite you to attend the 43rd IEEE Symposium on VLSI Technology and Circuits. For more information, please visit www.vlsisymposium.org. See you in Kyoto!

> Symposium Chairs: Katsura Miyashita, Toshiba Electronic Devices & Storage Co. Yusuke Oike, Sony Semiconductor Solutions

Symposium Co-Chairs: Gosia Jurczak, Lam Research Borivoje Nikolić, University of California, Berkeley

> Program Chairs: TakaakiTsunomura, Tokyo Electron Limited Mototsugu Hamada, The University of Tokyo

> > Program Co-Chairs: Vijay Narayanan, IBM Ron Kapusta, Analog Devices, Inc.

## **2023 IEEE INTERNATIONAL MEMORY WORKSHOP**

The 15th International Memory Workshop (IMW) is currently planned as an on-site event on 21–24 May 2023 in Monterey, California. The conference brings the memory community together in a workshop environment to discuss the memory process and design technologies, applications, market needs, and strategies. It is spon-

Panel discussion IMW 2022

sored by the IEEE Electron Devices Society and meets annually in May. The IMW is a premier international forum for both new and seasoned technologists having diverse technical backgrounds to share and

learn about the latest developments in memory technology with the global community. The scope of workshop content ranges from new memory concepts in early research to the technology drivers currently in volume production as well as emerging technologies in development. The workshop will start on Sunday, 21 May with a Tutorial Session, followed by Technical Sessions from Monday, 22 May until Wednesday, 24 May. The evening panel discussions will address hot topics in the memory field and active participation and discussions will be encouraged.

For more information, registration and the actual program check the conference website: https://www.ewh. ieee.org/soc/eds/imw/index.htm

> Dirk Wouters 2023 IMW Publicity Chair

## 2023 IEEE BICMOS AND COMPOUND SEMICONDUCTOR INTEGRATED CIRCUITS AND TECHNOLOGY SYMPOSIUM