JULY 2021 VOL. 28, NO. 3 ISSN: 1074 1879

**EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI**

#### TABLE OF CONTENTS

| TECHNICAL BRIEFS                                                                                                                                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SOCIETY NEWS                                                                                                                                                                                          |

| EDS AWARDS AND CALLS FOR NOMINATIONS                                                                                                                                                                  |

| Susan Lord—Cutting Ties, Forging Paths, and Speaking Up     Nadine Collaert—My Wonderful Journey in Science and Engineering     IEEE Electron Devices Society's International Women's Day (IWD) Event |

| EDS YOUNG PROFESSIONALS                                                                                                                                                                               |

| BOS HUMANITARIAN PROJECTS                                                                                                                                                                             |

| CHAPTER NEWS                                                                                                                                                                                          |

| REGIONAL NEWS                                                                                                                                                                                         |

| EDS MEETING CALENDAR                                                                                                                                                                                  |

| EDG MIGGION VIGION AND FIELD OF INTEREST                                                                                                                                                              |

STATEMENTS...

### TECHNICAL BRIEFS

#### BEYOND CMOS (BC)

MATTHEW MARINELLA<sup>1</sup>, SHAMIK DAS<sup>2</sup>, SAPAN AGARWAL<sup>1</sup>, MICHAEL P. FRANK<sup>1</sup>, HIRO AKINAGA<sup>3</sup>, AN CHEN<sup>4</sup>

<sup>1</sup>Sandia National Laboratories\*, <sup>2</sup>MITRE\*\*, <sup>3</sup>National Institute of Advanced Industrial Science and Technology (AIST), <sup>4</sup>IBM Research \*Sandia National Laboratories is a multi-mission laboratory managed and operated by National Technology & Engineering Solutions of Sandia, LLC, a wholly owned subsidiary of Honeywell International Inc., for the U.S. Department of Energy's National Nuclear Security Administration under contract DE-NAOO03525. Approved for public release SAND2021-6396 O. \*\*Approved by The MITRE Corporation for Public Release; Distribution Unlimited. Public Release Case Number 20-02213-5.

#### I. Introduction

CMOS scaling has driven a broad spectrum of applications through increased performance and complexity. As dimensional scaling of CMOS eventually approaches fundamental limits, new information processing devices and architectures have been explored extensively in both academia and industry. The Beyond CMOS (BC) chapter in the International Roadmap for Devices and Systems (IRDS) surveys, catalogs, and assesses viable emerging devices and novel architectures for their long-range potential, and identifies the scientific and technological challenges gating their acceptance by the semiconductor industry. In the previous International Technology Roadmap for Semiconductors (ITRS), the Emerging Research Devices (ERD) chapter covered a similar scope. The BC chapter in IRDS has inherited certain content, structure, and methodology from the ERD chapter in ITRS. During the transition from ITRS to IRDS, the importance of co-optimization of emerging devices and architectures has been increasingly recognized in the broad research community. Therefore, beyond the traditional focus on emerging memory and logic devices, the BC chapter has placed significant emphasis on emerging device-architecture interactions.

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at daniel.tomaszewski@imif.lukasiewicz.gov.pl

# SOCIETY

#### President

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

#### Treasurer

Bin Zhao Freescale Semiconductor Email: bin.zhao@ieee.org

#### Errian. birr.zriao@iccc.oi

**Secretary** M.K. Radhakrishnan

NanoRel

Email: radhakrishnan@ieee.org

#### Jr. Past President

Fernando Guarin GlobalFoundries

Email: fernando.guarin@ieee.org

#### Sr. Past President

Samar Saha Prospicient Devices Email: samar@ieee.org

#### Vice President of Education

Navakanta Bhat Indian Institute of Science Email: navakant@gmail.com

#### Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

## Vice President of Membership and Services

Patrick Fay University of Notre Dame Email: pfay@nd.edu

## Vice President of Publications and Products

Joachim Burghartz Institute for Microelectronics Stuttgart Email: burghartz@ims-chips.de

#### Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

#### Vice President of Strategic Directions

Paul Berger

The Ohio State University Email: pberger@ieee.org

# Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2021                                                                                                                                      | TERM                           | 2022                                                                                                                            | TERM                     | 2023                                                                                                                                              | TERM                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Paul Berger<br>Navakanta Bhat<br>Merlyne De Souza<br>Kazumari Ishimaru<br>William (Bill) Nehrei<br>Murty Polavarapu<br>Camilo Velez Cuerv | a (1)<br>u (1)<br>r (1)<br>(2) | Constantin Bulucea<br>Daniel Camacho<br>John Dallesasse<br>Mario Lanza<br>Geok Ing Ng<br>Claudio Paoloni<br>Hitoshi Wakabayashi | (1)<br>(1)<br>(1)<br>(1) | Roger Booth<br>Xiojun Guo<br>Edmundo A. Gutierrez-D.<br>Francesca lacopi<br>Benjamin Iniguez<br>P. Susthitha Menon<br>Manoj Saxena<br>Sumant Sood | (2)<br>(1)<br>(2)<br>(1)<br>(2)<br>(1)<br>(2)<br>(2) |

# NEWSLETTER EDITORIAL STAFF

#### Editor-In-Chief

Daniel Tomaszewski

Institute of Microelectronics and Photonics

Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### Associate Editor-in-Chief

Manoj Saxena Deen Dayal Upadhyaya College

University of Delhi Email: msaxena@ieee.org

#### REGIONS 1-6, 7 & 9 Eastern, Northeastern &

Southeastern USA (Regions 1, 2 & 3)

Rinus Lee

TEL Technology Center, America Email: rinuslee@ieee.org

# Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University Email: mmadachi@sfu.ca

# Southwestern & Western USA (Regions 5 & 6)

Muhammad Mustafa Hussain University of California—Berkeley Email: MuhammadMustafa. Hussain@kaust.edu.sa

#### Latin America North (Region 9)

Joel Molina Reyes INAOE

Email: jmolina@inaoep.mx

#### Latin America South (Region 9)

Paula Ghedini Der Agopian UNESP, Sao Paulo State University Email: paula.agopian@unesp.br

# REGION 8 Eastern Europe

Kateryna Arkhypova IRE NASU

Email: arkhykate@ieee.org

#### Scandinavia & Central Europe

Marcin Janicki

Lodz University of Technology Email: janicki@dmcs.pl

#### United Kingdom, Middle East & Africa

Stewart Smith

Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

#### Western Europe

Mike Schwarz Mittelhessen University of Applied Sciences Email: mike.schwarz1980@ googlemail.com

#### **REGION 10**

# Australia, New Zealand & South East Asia

Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University

Email: thhou@mail.nctu.edu.tw

#### South Asia

Soumya Pandit University of Calcutta

Email: soumya\_pandit@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission.

#### Newsletter Deadlines

ISSUE

October

January

April

July

April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2021 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

#### BEYOND CMOS (BC)

(continued from page 1)

Although the semiconductor industry faces difficult challenges in CMOS dimensional scaling, there are promising alternative directions for sustained improvement in chip performance and functionality. Integrating new high-speed, high-density, and low-power memory technologies onto the CMOS platform may break the "memory wall", improve system performance, and enable new computing paradigms (e.g., in-memory compute). Novel switches based on new materials, alternative mechanisms, and non-charge state variables (e.g., steep-slope transistors, phase-transition devices, nonvolatile switches) may achieve significantly better energy efficiency than CMOS transistors based on thermionic emission over the channel energy barrier. New information processing technologies substantially beyond the capabilities of CMOS may originate from an innovative combination of new devices, interconnect, and architecture for extending CMOS, which may eventually lead to new platform technologies. Ultimately scaled CMOS as a platform technology may also extend into new domain of functionalities and applications (e.g., security, sensing, communication), a general direction known as "more than Moore". For all these promising directions beyond CMOS and dimensional scaling, new materials and integration techniques play essential roles to enable their implementations.

The BC chapter covers the following major areas: 1) emerging memory and storage devices, 2) emerging logic and alternative information processing devices, 3) emerging device-architecture interactions (including new computing paradigms), and 4) emerging materials integration. This article will briefly review these areas of research and present key observations and recommendations.

#### II. Emerging Memory and Storage Devices

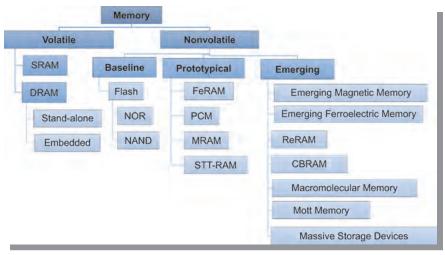

Memory is an essential element of computing, and the characteristics of the memory device technologies play a significant role in the architecture of an information processing system. A taxonomy of current memory devices is given in Fig. 1. Static and dynamic random access memory (SRAM and DRAM) remain the workhorse computing memory technologies, due to their high speed and endurance. Both are volatile and require backup storage when powered down. Nonvolatile memory includes flash, the most prominent and technologically mature baseline technology. The term "flash" refers to an array architecture for charge based memory cells such as floating gate and charge trapping memory, both of which serve as the main data storage mechanism for most modern information processing systems. SRAM, DRAM, and Flash memory have followed Moore's Law scaling for several decades, which was tracked by the ITRS until 2015 and is currently tracked by IRDS. Prototypical devices have matured to the point where the technology is in small-scale commercial production,

and often the technology is making progress on factors such as scaling and density. In this case, prototypical devices that are making progress have historically been tracked by ITRS and expected future progress is predicted. These technologies include ferroelectric memory (Fe-RAM), phase change memory (PCM), field-switched magnetic memory (MRAM), and spin transfer torque magnetic memory (STT-MRAM). Several of these technologies, such as STT-MRAM started in the emerging category and have progressed to the prototypical phase and are continuing to progress commercially.

The primary purpose of the Emerging Memory Devices section is to track technical progress for those devices in the rightmost "emerging" column. This section provides a technical overview of each device, and is accompanied by tables that track key properties of these devices as reported in the literature, such as endurance, retention, switching characteristics, and minimum dimensions. These emerging memory devices are the subject of significant research, with potential to continue storage density scaling beyond physical limits of flash, improve computing efficiency by enabling storage class memory,

Figure 1. Emerging memory devices taxonomy.

and enable new computing paradigms such as in-memory compute.

One of the most active emerging memory research topics is magnetic memories. STT-MRAM has made significant progress in the past decade, and recently we have seen the emergence of several commercial products and integration in commercial foundries. This is due to excellent scalability, CMOS-compatible voltages, high endurance, and compatibility with back end of line CMOS processes. STT-MRAM has the potential for future use as a cache replacement, [1] although it will be important to reduce switching current, increase speed, and increase energy efficiency. This need for improved magnetic memory properties has prompted research in emerging magnetic devices. One example is the three terminal memory structure which harnesses spin orbit torque (SOT) effect, reducing the current density required to switch the magnetization of a magnetic tunnel junction (MTJ). Another active area of research is in voltage controlled magnetic anisotropy (VCMA), which harnesses magnetoelectric effects to reduce the energy and improve the speed of MTJ switching [2].

Resistive and conductive-bridge random access memory (ReRAM and

CBRAM), have seen also significant commercial interest and research activity in the literature, due to potential for applications such as storage class memory, edge computing, and efficient processing of neural networks. These are two terminal resistive switching device structures, with a memory state defined by the resistance. This resistance is controlled by the connecting and breaking of metallic conductive filaments (CBRAM) or modulation of oxygen vacancy concentrations in a metal oxide (ReRAM). Resistive memories are highly scalable and CMOS-compatible, and hence are being integrated into foundry processes. Research challenges for these devices continue to be improving the understanding, parametric control, and reliability. Emerging polymer memories, which incorporation organic materials, often rely on similar physical mechanisms to ReRAM and CBRAM [3].

Ferroelectric memories, including the ferroelectric field effect transistor (FeFET) have seen a resurgence of interest recently due to the discovery of ferroelectricity in HfO [4] which has provided a path for FeFET scalability and CMOS compatibility. Other new technologies that are fur-

ther from commercialization (and lack concrete benchmarks) have become the subject of significant research. For example, DNA storage (covered under massive storage devices) has the highest volumetric information storage capacity of any known medium, which has motivated research to tackle the practical challenges of using these complex organic molecules for information storage. It is hoped that the IRDS coverage of emerging memories can serve as a reference for the electron device community and engineers in understanding new memory devices and their impact on future computing systems, for funding agencies in understanding the memory research challenges, as well as for students and others in academia who need a better understanding of the memory research landscape.

# III. Emerging Logic and Information Processing Devices

For nearly twenty years, the industry's semiconductor roadmap has featured device options that might surpass silicon CMOS as the driver for logic, computation, and information processing applications. Originally captured as Emerging Research Devices, recent editions of the IRDS present these as Logic Devices Beyond CMOS. Though silicon CMOS has proved exceptionally hardy and productive over the last twenty years, the roadmap continues to track Beyond-CMOS devices for both near-term successors and more disruptive, longer-term candidates.

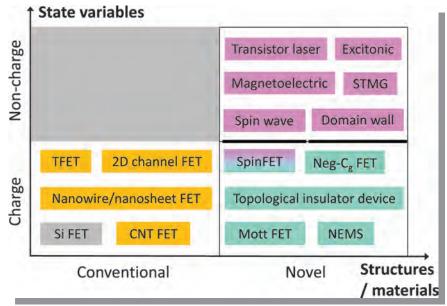

Figure 2 depicts the taxonomy of emerging logic devices as conveyed in the IRDS. Such devices depart from the present state-of-the-art in two primary ways. First, the structure and materials constituting the device will be different to some degree from silicon planar FETs or FinFETs. This departure is shown on the horizontal axis. Second, the physical manifestation of digital information, also known as the state variable, may differ from the electric charge that is used in FETs. This is shown on the vertical

Figure 2. Taxonomy of logic devices beyond CMOS. Reproduced from Figure BC3.1 of the 2021 IRDS Beyond CMOS chapter.

axis. Considering these elements together, a natural three-part grouping emerges that is used to characterize near-term vs. far-term candidates for the evolution of semiconductors.

The nearest of these candidates are the conventionally structured, chargebased devices listed in the lower left of the figure. Such devices include nanowire transistors and carbon nanotube transistors, for example. The intent with these devices is to obtain charge transport characteristics exceeding the semiconductor channels of conventional devices. Thus, a few of these candidates could be considered as potential channel-replacement technologies for near-future state-ofthe-art devices and are also tracked within the "More Moore" component of the IRDS. This includes "stacked nanosheet" devices as well as vertical gate-all-around (VGAA) transistors.

Further evolutions of charge-based devices are considered in the lower right of the figure. Here, one begins to see mechanisms for modulating charge transport that differ from the electrostatic field effect. Some examples include using a type of metal-insulator phase transition (Mott transition) as a switch or using electromechanical potential to store a digital state. Because of the greater departure in materials systems from CMOS as compared with the first category of candidates, it is expected that integration with CMOS will be more complicated and take longer to manifest commercially. Also, it is less clear for any of these devices that there is a route to the kind of universal performance applicability and scalability that has made silicon CMOS economically viable for so long.

A recent addition to the Beyond CMOS roadmap in this second group of the figure is the topological insulator transistor. Research into topological insulators as materials has increased substantially in recent years, primarily for applications in quantum information science. Some of these research results suggest routes to using topological properties

to increase the speed and power efficiency of field-effect devices. It is an ongoing line of inquiry to determine if such advantages can be materialized robustly at room temperature with commercially relevant yields.

Finally, the Beyond CMOS roadmap has always monitored the progress in devices shown at upper right in the figure, which represent a substantial departure both in form and function from conventional semiconductor field-effect transistors. Principally, these devices use a noncharge-based state variable, such as a remnant magnetization, exciton, or optical/photonic state. In some cases, state information can be transported via charges, such as with a spin-filtered electronic current. In others, the change in state variable also requires a novel form or material structure for the interconnect. Thus, development and commercial maturation for these candidates is expected to take significant time, or else such devices might only be used within heterogeneous integration contexts, i.e., alongside state-of-the-art silicon.

As the industry progresses and the nearer-term Beyond CMOS candidates become more central to the IRDS. the focus of logic device evaluation beyond CMOS will evolve. Though the core focus remains on digital information processing, it seems less and less likely that a candidate will emerge that will take over the mantle of the silicon FET as the workhorse of linear, multi-generational progression for the industry. Instead, a variety of devices tailored to a variety of applications and accelerators will need to be explored and matured using ultimate silicon as a foundation for experimentation and commercialization.

#### IV. Emerging Architectures and Device Interaction

Many new emerging devices will require co-design between devices and higher levels of computer design (e.g., circuit, architecture, and application). These emerging devices are not intended simply as "drop-in" replacements for standard CMOS devices. but will require new types of circuit designs, new functional module architectures, and even new software to best utilize the new devices' capabilities [5].

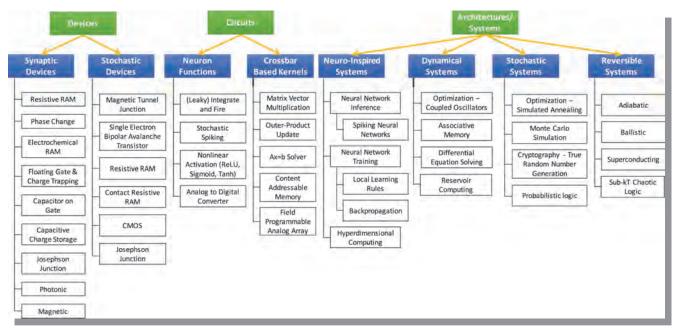

Novel design issues that span the device and architecture levels especially need to be considered when adopting new low-level computing paradigms. Devices may be organized in radically new ways to carry out computation in a very different style from what we may consider the most "conventional" computing paradigm, which has relied on standard combinational and sequential nonreversible Boolean logic. The Beyond CMOS roadmap has begun tracking some of the most common building blocks for emerging systems and applications as shown in Fig 3.

At the device level, there are many types of devices that function as a synaptic device that both hold a stored state and use that state to modulate an analog input. This type of device is critical to overcoming the von Neumann Bottleneck: rather than moving data between memory and a processor, processing is directly integrated with each memory element. The analog processing of a synaptic device can also replace the 1,000's of transistors needed to do a digital operation with a single device. Another important class of devices are stochastic devices that generate a random binary or analog value. For many of the devices the probability distribution is tunable allowing for controllable randomness. Conventional digital logic is deterministic and cannot introduce true randomness, and instead require relatively expensive pseudo random number generators (PRNGs). Replacing a large expensive PRNG with a single device allows one to consider algorithms that are inherently stochastic and would otherwise be computationally expensive.

At the circuit level there are both circuits dedicated to computing a specific "neuron" function very efficiently, and circuits that are based on a crossbar array of synaptic devices

Figure 3. Emerging architectures require co-designing new devices, computational kernels and computational systems.

Some of the possible building blocks are shown.

to compute a given matrix operation. Converting between analog and digital is typically a very expensive operation, and so neuron devices and circuits that can directly operate on an analog input avoid this cost. Common functions include leaky-integrate-andfire neurons, stochastic spiking neurons, rectified linear neurons, and sigmoidal neurons. At the array level, there are computational kernels that can read a matrix in parallel by performing matrix vector multiplication, write a matrix in parallel by updating all values by the outer product of two input vectors, approximately solve the matrix equation Ax = b for a vector x, implement a content addressable memory, and provide a reconfigurable analog computing substrate through a field programmable analog array.

These enabling devices and circuits can then be used to build a wide variety of architectures and systems. Neuro-inspired systems include conventional neural network inference and backpropagation based training. Spiking neural networks promise to reduce communication and analog to digital conversion (ADC) costs. New neural training algorithms based on

local learning rules promise to drastically reduce the data-movement and buffering needed to train a neural network. Hyperdimensional computing is a new high-dimensional learning system that is enabled by large hardwarebased content addressable memories.

Dynamical systems can use the temporal evolution of a recurrently connected system to solve a variety of problems. Coupled oscillators can be used to solve optimization problems. Associative memories can be stored in Hopfield networks. Differential equations can be mapped to analog substrates, and reservoir computing systems can be used to analyze temporal data. Chaotic logic networks can carry out monolithic reversible transformations of the state of a Boolean circuit even down to sub-kT signal levels.

Stochastic devices enable new systems that are built around repeated random sampling. Simulated annealing can be used to solve optimization problems. Stochastic devices enable Monte Carlo simulation. True random number generation is critical for cryptographic applications and tunable random devices enable probabilistic logic.

In addition to developing accelerators for specific computing functions, reversible computing systems aim to lower the energy dissipation of general digital logic, including both general-purpose programmable digital processors, and more specialized digital ASICs. Rigorous thermodynamic arguments have shown that the fundamental Landauer limit on energy efficiency can only be avoided in deterministic computational processes composed from local primitive operations if they have the property of (conditioned or unconditional) logical reversibility [6]. In addition to the potential for reducing minimum energy dissipation below conventional limits, reversible techniques can potentially exceed the conventional limits on larger-scale practical computing efficiency. Concrete examples of reversible computing systems based on both semiconducting and superconducting technology platforms have been demonstrated, and this area seems ripe for further development.

In this section, the Beyond CMOS roadmap has surveyed a variety of concepts and R&D directions for the development of novel beyond-CMOS computing technologies that represent an effort to think "outside the box," in the sense of looking beyond

just developing simple drop-in replacements for traditional logic and memory cells. More broadly, new hardware designs spanning multiple levels from the devices up through circuits and architectures must be considered, and the interactions between the various levels explored. More specifically, we expand the scope of future computing technologies beyond traditional irreversible, deterministic digital logic to include a broad range of alternative, unconventional computational paradigms, such as analog, probabilistic, and (classical) reversible computing paradigms.

# V. Emerging Materials Integration

In the previous ITRS activities that form integrated knowledge and collective intelligence in academia, consortia, and industry researchers, the international technology working group of Emerging Research Materials (ERM) presented potential solutions from a materials science perspective for future logic and memory devices, front end processing, interconnects, assembly and package, lithography, metrology, and life-cycle assessment of Environment, Safety, and Health (ESH)-related issues [7]. Taking over that experience, the IRDS 2020 edition set up "Emerging Materials Integration (EMI)" section in the "Beyond CMOS" chapter. While existing technologies are integrated on a Si-based platform, the majority of beyond-CMOS technologies are based on entirely new materials and cutting-edge material science. The key EMI challenge is to provide timely guidance on emerging materials, process performance, cost, reliability, and sustainable developments that will drive breakthroughs in the future. Figure 4 depicts the role of EMI, which is to promote the advancement of existing technologies.

The current EMI section emphasizes strategic challenges, novel breakthroughs, and potentially disruptive opportunities for emerging material properties, synthetic methods, and

Figure 4. Emerging Material Integration promotes the advancement of existing technologies.

metrology, organized in the following areas: (1) Scaled technology materials needs for More Moore, (2) Novel materials for Beyond CMOS, and (3) Potentially disruptive material opportunities for functional scaling and convergent applications. Regarding materials for advanced More Moore technologies, high mobility transition metal dichalcogenides (TMD) with low defect density and low resistance ohmic contacts are listed as a longterm difficult challenge. Nano-carbon materials, complex metal oxides and spin-related materials are attracting attention as materials for non-CMOS logic and memory devices. Novel interlayer dielectrics, such as Metal Organic Framework (MOF) and Carbon Organic Framework (COF) will improve the interconnect reliability. Materials and processes that enable monolithically 3D integrated complex functionality, such as integration with flexible electronics and biocompatible functional materials, are also included in long-term challenges. As one of the convergent opportunities, EMI section refers to Big data and Digital transformation (DX) issues. Robust and ubiquitous information processing and independent power supplies (such as Energy Harvesting expanding the IoT utilization, one of the major topics in "More than

Moore" chapter) will be a place for emerging materials to play an active role. Emerging materials have been spurring developments of non-von Neumann architectures for novel computing, such as neuromorphic computing, reinforcement learning, topological quantum computing, reversible computing, and probabilistic computing. A typical example is physical reservoir computing. Since computing performance in these systems depends on the unique material properties of the reservoir, the material research to optimize physical phenomena for reservoir computing will directly improve performance metrics such as energy efficiency. It is expected that the output of energy harvesting and the required power for novel computing approaches will be matched in the near future.

To drive emerging material technologies, the EMI section focuses on multiscale simulation. Conventional multiscale physics modeling was described previously in the ERM chapter of ITRS, where the physics to explain mesoscopic level phenomena is required to link electronic properties and device characterization. In the EMI section of the current BC chapter, a potential role for machine learning and informatics has been suggested as an alternative to the simulation in the

mesoscopic level, where inputs of molecular level phenomena provide an output describing continuum level phenomena. Transient electronics is introduced as one example of a disruptive technology. Here, materials, devices, and systems disappear with minimal or non-traceable remains in a controllable period of time. The spontaneous and transient functions in the material property, such as a conductance change with a controllable decay in atomic switches, are also treated with the appearance of transient electronics in the EMI section. This emerging electronics with a 'fading' capability will bring about intelligent applications, such as environmentally friendly electronics for one of the targets of SGDs Goal 12, to substantially reduce waste generation through prevention, reduction, recycling and reuse [8]. Future editions of EMI will provide additional descriptions and continue to adapt its scope to engage with societal environment, such as autonomous systems, smart cities and CPS. Cooperation with international standardization groups, which prepares a common protocol for assessing the properties of emerging materials, will also be considered part of EMI activities.

#### VI. Assessment

With a large variety of mechanisms and characteristics as well as different levels of maturity, beyond-CMOS devices present a unique challenge for assessment of their performance and potential. The BC chapter has referenced the emerging device benchmarking in the Nanoelectronics Research Initiative (NRI) for quantitative assessment [9]. The NRI benchmarking evaluates novel switches in conventional Boolean logic circuits (e.g., an inverter, a 2-input NAND gate) with quantitative metrics (e.g., speed, power dissipation, footprint, span of control, logical effort). Although the assessment of beyond-CMOS devices is an evolving effort and conclusions could be continuously altered by new research progress, some observations are worth noticing. First, the power-speed tradeoff commonly

observed in CMOS continues to be a challenge for beyond-CMOS devices. Many beyond-CMOS devices utilize novel mechanisms and non-charge state variables to achieve low switching power; however, communication with many non-charge tokens is often significantly slower than moving charges. Second, most beyond-CMOS devices have not been shown to be capable of replacing CMOS with better power-speed performance. CMOS will remain the primary basis for IC chips for the coming years. Some promising beyond-CMOS technologies could be utilized to augment CMOS as special purpose accelerators to offload specific computations from the generalpurpose processors. While integrating dissimilar technologies and materials is challenging, advance in heterogeneous integration may make this more feasible over time. Third, as the characteristics of beyond-CMOS devices become better understood and controlled, work on novel architectures that can leverage these unique devices becomes increasingly important. Cooptimization of emerging devices and architectures may have great potential to improve the energy efficiency and performance of computing systems. Last, the high-precision fabrication capabilities critical to CMOS (e.g., patterning, deposition, purity, doping, alignment) will continue to be important in the realization of systems built upon beyond-CMOS devices.

Previously, the ITRS ERD chapter utilized a survey-based critical review to assess the potential of beyond-CMOS devices, as a consensus among researchers participating in the survey. The ERD assessment measured devices on a scale of 1 to 3 on a set of criteria, including scalability, speed, energy-efficiency, gain (or on/off ratio), operational reliability, operational temperature, and CMOS compatibility. A spider chart was used to visualize the assessment. The ERD survey-based assessment has been widely cited in literature, although the scale of the survey sometimes raised questions about the accuracy of some assessment. At the same time, for highly exploratory devices without sufficient data, this assessment based on the survey of experts' perspective indeed provided an alternative measure of their potential.

As beyond-CMOS devices are being developed increasingly for novel computing paradigms beyond Boolean logic and von Neumann architecture, benchmarking cannot be simply performed at the device or logic gate levels. Benchmarking across multiple layers from devices to architectures is a great challenge that has to be addressed by interdisciplinary collaborations. Facing a large variety of design options and applications, benchmarking needs to be focused with well defined criteria and assumptions in order to produce meaningful results. Unlike in mature technologies where benchmarking may be more conclusive, beyond-CMOS benchmarking may provide guidance more than drawing definitive conclusions.

#### VII. Summary

Beyond-CMOS research has gone through a transition from a focus on novel devices with the potential to replace CMOS transistors to a holistic approach driven by device-architecture interaction and cooptimization to augment CMOS. The IRDS Beyond CMOS (BC) chapter not only tracks the progress of emerging logic and memory devices but also summarizes their utilization in unconventional computing architectures and applications. New computing paradigms may exploit unique characteristics of beyond-CMOS devices for more efficient native implementations of key functions. These promising devices often rely on emerging materials and advanced fabrication and integration techniques for demonstration and prototyping. The IRDS Beyond CMOS (BC) chapter covers promising research directions from materials and devices up to designs and architectures, to provide a comprehensive reference for research beyond conventional CMOS technologies, Boolean logic, and von Neumann architectures. As the dimensional scaling reaches its

limits, continued improvement of chip efficiency and performance may be driven by co-optimization, integration, and functional diversification. Beyond-CMOS devices and architectures may provide promising technology options for ongoing improvement.

#### References

[1] G. Hu et al., "Spin-transfer torque MRAM with reliable 2 ns writing for last level cache applications," 2019 IEEE International Electron Devices Meeting (IEDM), pp. 2.6.1-2.6.4 (2019). doi: 10.1109/IEDM19573.2019.8993604 [2] B. Rana, Y. Otani, "Towards magnonic devices based on voltage-controlled magnetic anisotropy," Communications Physics 2, 90, pp. 1-12 (2019). doi: 10.1038/s42005-019-0189-6

[3] Q.-D. Ling, D.-J. Liaw, C. Zhu, D. S.-H. Chan, E.-T. Kang and K.-G. Neoh, "Polymer electronic memories: materials devices and mechanisms", Progr. Polymer Sci., 33, pp. 917-978 (2008). doi:10.1016/j. progpolymsci.2008.08.001

[4] T. S. Böscke, J. Müller, D. Bräuhaus, U. Schröder, and U. Böttger, "Ferroelectricity in hafnium oxide thin films," Applied Physics Letters, 99(10), p. 102903 (2011). doi: 10.1063/1.3634052

[5] T. P. Xiao, C. H. Bennett, B. Feinberg, S. Agarwal, and M. J. Marinella, "Analog architectures for neural network acceleration based on nonvolatile memory," Applied Physics Reviews, 7(3), p. 031301 (2020). doi: 10.1063/1.5143815

[6] M. P. Frank and K. Shukla, "Quantum foundations of classical reversible computing," Preprints (2021), 2021050066. doi: 10.20944/preprints202105.0066.v2

[7] S.W. King, H. Simka, D. Herr, H. Akinaga, and M. Garner, "Research updates: the three M's (materials, metrology, and modeling) together pave the path to future nanoelectronic technologies," APL Materials, 1, p. 040701 (2013). doi: 10.1063/1.4822437 [8] United Nations Development Programme: GOAL 12 TARGETS [Internet] (accessed April 20, 2021) (https:// www.undp.org/content/undp/en/ home/sustainable-developmentgoals/goal-12-responsible-consumption-and-production/targets.html) [9] C. Pan and A. Naeemi, "An expanded benchmarking of beyond-CMOS devices based on boolean and neuromorphic representative circuits," IEEE J. Exploratory Solid-State Computational Devices and Circuits 3, p.101 (2017). doi: 0.1109/

JXCDC.2018.2793536

# AN INTRODUCTION TO SIC POWER DEVICES: STATUS, CHALLENGES, AND OUTLOOK

VICTOR VELIADIS, PH.D., IEEE FELLOW EXECUTIVE DIRECTOR AND CTO, POWERAMERICA Professor in Electrical and Computer Engineering, North Carolina State University E-MAIL: JVVELIAD@NCSU.EDU

In an increasingly electrified technology driven world, power electronics is central to the entire manufacturing economy. Silicon (Si) power devices have dominated power electronics due to their low cost volume production, excellent starting material quality, ease of processing, and proven reliability. Although Si power devices continue to make significant progress, they are approaching their operational limits primarily due to their relatively low bandgap and critical electric field that result in high conduction and switching losses, and poor high temperature performance.

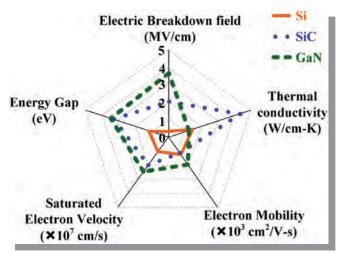

Wide bandgap power semiconductor devices like Silicon Carbide (SiC) and the III-IV nitrides are currently in production for high power/ temperature applications. Silicon car-

bide (SiC) is ideally suited for power switching due to its high critical electric field strength, its large bandgap, its excellent thermal conductivity, and its high saturated drift-velocity. For power devices, the tenfold increase in critical electric field strength of SiC relative to Si allows high voltage blocking layers to be fabricated significantly thinner than those of comparable Si devices. This reduces device on-state resistance and the associated conduction and switching losses, while maintaining the same high voltage blocking capability. Lower switching losses allow for high frequency operation, which decreases the size and weight of a system's passive components. The low specific on-state resistance enables high-current operation at a relatively low forward voltage drop at a given

breakdown voltage. In addition, the wide bandgap of SiC allows operation at high temperatures, where conventional Si devices fail, with low leakage and reduced cooling system requirements. A graphical summary of Si, SiC, and GaN relevant material properties is shown in Fig. 1, [1].

To exploit SiC's compelling material properties in power devices, significant efforts started in the 1980s to develop high quality, low defect SiC substrates and epitaxy. Today, 150 mm SiC wafers are primarily used in the production of SiC devices. 200 mm wafers were demonstrated in 2015 and are expected to become commercially available from several vendors as early as 2022. It should be noted that conventional SiC substrate growth is more complex than that of Si requiring the use of large seeds and

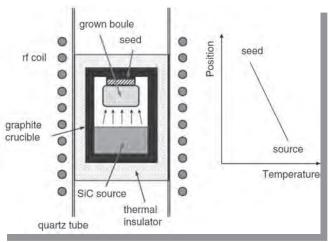

high process temperatures. SiC substrates are mainly grown by the seeded sublimation technique, as schematically shown in Fig. 2.

The raw material, SiC powder, is placed at the bottom of a graphite crucible. A seed wafer is placed at the top of the crucible, which is heated by RF coils to a temperature of ~2500 °C. The seed wafer is kept at lower temperature than the SiC powder and the sublimed SiC species condensate and crystallize on the seed wafer. Reported sublimation growth rates are in the order of 0.5-2 mm/h. Increasing the growth rate can have the undesirable side effect of increased structural defect inclusion in the boule. SiC material's hardness, which is comparable to that of diamond, makes sawing and polishing SiC substrates slow and costly relative to Si.

The epitaxial active SiC device layer is grown by chemical vapor deposition (CVD) in horizontal or planetary reactors at 1500–1650 °C. Pressure typically

ranges from 30 to 90 torr and growth rate can be as high as 46 mm/hr. The epitaxial growth is done on 4-degree off-cut substrates to maintain the polytype stability of the substrate. Breakdown voltage capability is dependent on the doping concentration and thickness of the epitaxial layer. For example, the optimal epitaxial values for 1200 V devices are a drift layer doping of  $1 \times 10^{16}$  cm<sup>-3</sup> and a thickness of 10  $\mu$ m. For 10 kV devices, the optimal values are  $7 \times 10^{14}$  cm<sup>-3</sup> and 95 µm, respectively. Uniformity control of doping and thickness is crucial in ensuring high device yields. "Thinner" SiC epitaxial growth is well established and strives to minimize defect propagation from the sub-

Figure 1. Graphical comparison of Si, SiC, and GaN material properties.

Figure 2. Schematic description of crucible for seeded sublimation growth of SiC substrates.

strate to the epitaxial layer. Growing the thicker epitaxial layers that enable high voltage devices is more complex and a subject of research and development efforts.

#### **SiC Defects**

Historically, killer defects limiting yield have been polytype inclusions and micropipes. These have practically been eliminated in commercial wafers. Micropipe density, which is detrimental to device operation, is typically below 0.1 cm<sup>-2</sup>. Remaining structural defects are threading screw dislocations (300–600 cm<sup>-2</sup>) that can increase reverse voltage leakage, threading edge dislocations (2000–5000 cm<sup>-2</sup>) that are consid-

ered benian, and Basal-Plane-Dislocations (BPDs) (500-3000 cm<sup>-2</sup>), which lead to device degradation under bipolar current flow. Although threading dislocations do result in measurable disturbances of epitaxial layer surface morphology, the practical effects of these disturbances on device performance and reliability are minimal [2]. BPDs are the major remaining "killer" defect impacting bipolar SiC devices as well as unipolar devices that conduct bipolar current during their operational cycle [3]. Basal plane dislocation defects are known to propagate from the wafer substrate through the thickness of the epitaxial layers where devices are fabricated. BPDs can also be generated during the high-temperature ion-implantation fabrication process. When bipolar current flows through a SiC transistor, electron-hole pair recombination at BPDs in the drift layer provides the energy to activate dislocation glides that give rise to

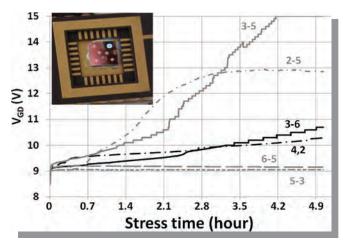

stacking faults and degradation. To investigate the impact of BPDs on the electrical characteristics of \_ion-implanted SiC transistors with 100-µm drift epilayers (10 kV rated), 17 JFETs of those specifications were stressed at a fixed gate-drain dc bi-polar current density of 100 A/cm² for 5 hr. Representative curves are presented in Fig. 3 [4].

At 100 A/cm², the gate–drain *p-n* junction is turned on, as evidenced by the emission of blue/violet electroluminescence at the edges of the JFET (inset photograph of Fig. 3), and bipolar current flows. Of the 17 JFETs stressed, six exhibit no forward gate–drain voltage degradation, nine exhibit intermediate voltage

degradation, and two exhibit severe voltage degradation. Representative forward gate-drain voltages as a function of stress time curves, under the fixed 100-A/cm<sup>2</sup> dc bipolar stress, are shown in Fig. 3 for the three "voltage-degradation" cases. A measurement compliance of  $V_{GD} = 15 \text{ V}$  is reached after 4 hr of bipolar injection for JFET 3-5. The forward/ reverse gate-source, forward/reverse gate-drain, transfer, blocking voltage, and ON-state conduction electrical JFET characteristics are measured before and after the 5 hr bipolarstressing period. Bipolar stress leads to forward gate-drain p-n junction and ON-state conduction degradations. Forward and reverse gate-source, transfer, reverse gate-drain, and blocking voltage JFET characteristics exhibit no degradation with bipolar stress.

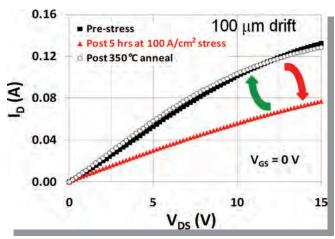

Interestingly, transistor BPD-related electrical characteristic degradations can be fully reversed by annealing at 350 °C, while non-degraded characteristics remain unaffected by this annealing. Representative SiC JFET ON-state conduction, BPD-related degradation and full recovery by annealing are shown in Fig. 4 [4].

#### **SiC Fabrication**

For mass SiC commercialization, high yielding fabrication processes are required. Numerous wellestablished processes from silicon technology have been successfully transferred to SiC. However, SiC material properties necessitate development of specific

Figure 3. Representative SiC JFET forward gate-drain voltages as a function of time for a fixed dc 100-A/cm² gate-drain bipolar stress. The compliance is set at  $V_{GD} = 15 \text{ V. A biased JFET with its gate-drain}$ diode's bipolar current giving rise to blue/violet electroluminescence is shown in the inset.

Figure 4. BPD-related SiC JFET ON-state conduction degradation and full recovery by annealing. The black squares, red triangles, and open circles represent the ON-state conduction electrical characteristics prior to bipolar stress, after 5 hours of 100-A/cm<sup>2</sup> bipolar stress, and after a 350 °C anneal, respectively.

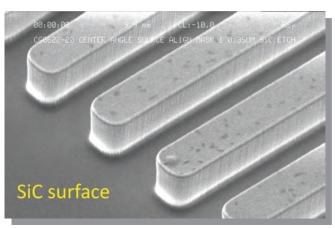

Figure 5. Reactive-ion etched 0.7 µm deep vertical SiC mesas using a Cr/Al mask.

processes, the parameters of which must be optimized and qualified [5]. SiC is inert against chemical solvents and only dry etching is practical. Furthermore, the hardness of SiC results in low photoresist selectivity and a "hard" mask, usually composed of metal or dielectrics, is required for SiC photolithographic patterning and etch. 0.7 µm deep SiC mesas, trenched using a "silicon" reactive-ion etch (RIE) tool and a Cr/Al mask, are shown in Fig. 5.

Cr assists with adhesion of metal layers to the underlying SiC surface. The RIE was fluorine-based for higher mask/SiC selectivity. RIE settings were optimized to eliminate micro-masking and achieve vertical etched sidewall profile formation.

Conventional thermal diffusion is not realistic in doping SiC due to its high melting point and the low diffusion constant of dopants within SiC. Heated ion-implantation is typically performed for doping densities of 1016-1020 cm-3 (the higher doping densities assisting with ohmic contact formation), and room temperature implantation can work well for low implant doses (~1015 cm-3). Nitrogen/ Phosphorus and Aluminum are the preferred Impurities for n-type and p-type SiC doping, respectively. The as-implanted depth profiles are retained after the anneal for AI, P, and N as expected from their low diffusion constants. The lack of diffusion makes it easy to form shallow junctions and difficult to form deep ones. After ion implantation, a 1600-1800 °C anneal is performed for lattice damage recovery, and high dopant electrical activation. A protective cap layer covering the SiC wafer protects its surface from degradation due to Si desorption and migration of surface atoms. Fig. 6 is a scanning electron microscopy image of a "post p+ ion-implantation" annealed wafer in the absence of a protective cap layer. The SiC wafer surface degrades due to Si desorption and migration of surface atoms. The wafer did not yield functional devices.

A wafer from the same fabrication lot, annealed simultaneously with that of Fig. 6 but with a carbon cap layer protecting its surface, exhibits excellent SiC morphology, Fig. 7, and high device yield. The high-energy ion-implantation bombardment signature is visible in the "nano-pits" of the implanted gate surface in Fig. 7.

The high value of the SiC/metal barrier results in rectifying metal contacts and post metal deposition anneal is required for ohmic contact formation. Typically, a 50-100 nm Ni layer is blanket deposited and patterned on the wafer for the simultaneous ohmic contact formation on the n-type and p-type doped regions, Fig. 8. Depending on the specifics of the fabrication process, isolating the source from the gate areas with dielectrics can facilitate high yields in the subsequent high temperature processing.

High temperature annealing of the Ni patterned wafer creates Ni-silicide for low resistivity ohmic contact formation. Rapid

Figure 6. Scanning electron microscopy image of a "post p+ ionimplantation" annealed wafer in the absence of a protective cap layer. The SiC wafer surface has degraded due to Si desorption and migration of surface atoms.

Figure 7. Scanning electron microscopy image of a "post p+ ion-implantation" annealed SiC wafer in the presence of a carbon protective cap layer. Excellent surface morphology and high device yield are attained.

Figure 8. Scanning electron microscopy image of a patterned Ni layer on a SiC wafer surface. Dielectric isolates the metalized p+ implanted gate areas (pitted surface) from the n-doped source stripes.

thermal annealing (RTA) at 950 °C, using standard silicon fabrication equipment, was used to create Ni silicide with no metal strings, Fig. 9. The dielectric isolates the source from the gate areas eliminating shorting during the high temperature silicide process.

Unlike Si wafers, SiC wafers are transparent. This complicates the use of "silicon" tools for CD-SEM and metrology measurements, as the focal plane is determined with the use of an optical microscope, SiCspecific wavelength metrology/inspection tools are now available from multiple vendors.

Another issue is the relative lack of flatness of SiC wafers, compared to those of Si, that can complicate photolithography. In addition, the high-temperature SiC processing can further degrade wafer flatness, occasionally rendering wafers unusable. This is particularly problematic with the thick epitaxy wafers used in +3.3 kV device fabrication. Efforts are underway to produce flatter starting SiC wafers, and to minimize flatness degradation during fabrication.

Lastly, the poor SiC/SiO<sub>3</sub> interface quality reduces inversion layer mobility, thus passivation techniques, including annealing in nitrides, are utilized to improve the SiC/SiO<sub>2</sub> interface quality. Furthermore, the high concentration of interface oxide traps leads to undesirable threshold voltage instability. A positive shift in threshold voltage increases conduction losses, while a negative threshold voltage shift can lead to unintentional device turn-on.

SiC process integration technology has made significant advancements and optimizations are continuing. Today, SiC transistors are commercially available in the 650-1700 V range from multiple vendors.

#### Large Area SiC **Transistors**

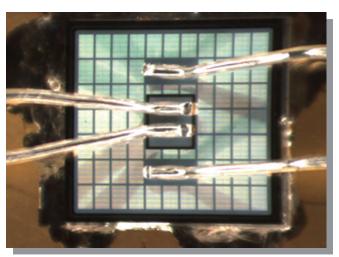

To effectively compete with Si, large-area reliable and rugged SiC devices must be produced at competitive cost. Early proof-of-concept work paved the way for investments that contributed to SiC commercialization. In 2008, a 1680 V SiC JFET with an active area of 0.143 cm<sup>2</sup> (0.19 cm<sup>2</sup> total area) and an on-state current capability of 50 A was the largest transistor reported at the time, [6]. JFETs were soldered into "testing" packages and wire bonded using 10 mil (254  $\mu$ m) diameter AI wires for electric characterization Fig. 10.

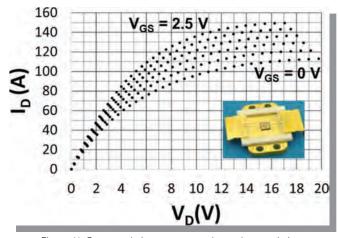

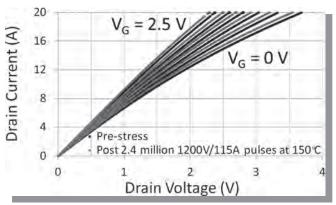

Room-temperature pulsed ON-state drain-current measurements were performed on packaged JFETs. The ON-state draincurrent vs. voltage characteristics are shown in Fig. 11 at a gate bias range of 0 to 2.5V in steps of 0.5 V. To maintain voltage-control capability (high  $I_D/I_G$  gain), the gate must be biased below its 2.7 V built-in potential value. If the gate bias increases in excess of 2.7 V, significant gate current injection occurs into the channel of the JFET, and its current gain I<sub>D</sub>/I<sub>G</sub> degrades. At a gate-to-source bias of 2.5 V, the JFET outputs 53.6 A at a forward drain voltage

Figure 9. Scanning electron microscopy image of the Ni patterned SiC wafer of Fig. 8, after a 950 °C rapid-thermal-annealing event. Ni silicide is formed with no shorting of the p-gate to the n-source regions.

Fig. 10. Optical image of a 1680 V SiC JFET with an active area of 0.143 cm² (0.19 cm² total area) packaged for electrical characterization.

Figure 11. On-state drain current vs. voltage characteristics of a single 1680 V, 0.143 cm<sup>2</sup> packaged SiC JFET, at a gate bias range of 0 to 2.5V in steps of 0.5 V.

drop of 2.08 V. The specific ON-state resistance is 5.5 mΩ · cm2, and the transistor current gain is  $I_D/I_G =$ 26,800.

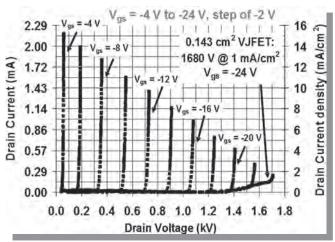

The blocking-voltage characteristics of the 0.143 cm<sup>2</sup> active area JFET at gate biases of -4 to -24V, in steps of -2 V are shown in Fig. 12. At a gate-to-source bias of -24 V and a low drain-current density of 1 mA/cm<sup>2</sup> the JFET blocks 1680 V.

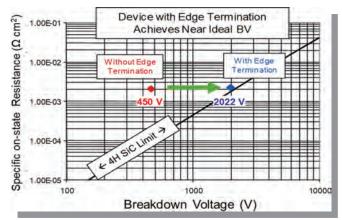

Specialized edge termination structures like multiple junction termination extensions and floating guard rings are fabricated to maximize the high-voltage performance [7]. The impact of edge termination in maximizing blocking voltage is graphically illustrated in Fig. 13. The blocking voltages of identical design and area SiC JFETs, fabricated next to each other on the same die of the same wafer, were measured. The JFETs had approximately equal resistance. One JFET was fabricated with a high performance floating guard ring edge termination while no edge termination was fabricated in the other. The former achieved a blocking voltage of 2022 V while the latter only blocked 450 V, Fig. 13. In short, a well-designed edge termination structure maximizes breakdown voltage with no associated increase in device resistance.

#### SiC Reliability and Ruggedness

Reliability and ruggedness demonstrations build confidence in SiC system insertion. An important contribution to SiC device reliability is reducing threshold-voltage

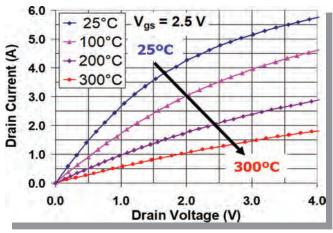

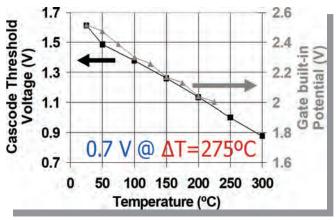

instability. In SiC MOSFETs, which are the dominant transistors in SiCbased power electronics applications, threshold-voltage instability is primarily due to the oxide traps at the SiC/gate-oxide interface. A positive shift in the SiC transistor's threshold voltage has the deleterious effect of increasing conduction losses, while a negative shift is undesirable as it can spontaneously turn the device on. To showcase the potential of SiC threshold-voltage stability, a JFET based all-SiC normally-off switch was implemented by combining a 1200 V normally-on (depletion mode) JFET with a low-voltage normallyoff (enhancement mode) JFET in the cascode configuration [8]. To evaluate threshold voltage shift with temperature, the  $I_{\rm DS}$ - $V_{\rm DS}$  characteristics of the all-SiC cascode switch were measured at junction temperatures of 25 °C, 100 °C, 200 °C and 300 °C and are shown in Fig. 14 [9]. The cascode's specific ON-state resistance was extracted from the data of Fig. 14 at  $V_{\rm DS}$  = 0.5 V.The increase in ON-state resistance with temperature agrees well with the theoretical reduction of the 4H-SiC electron mobility.

Based on the JFET cascode's thermal measurements, the cascode threshold voltage was extracted and is plotted as a function of temperature on the left axis of the graph of Fig. 15.

The threshold voltage decreases from 1.6 V to 0.9 V as the temperature

increases from 25 °C to 300 °C; the cascode switch remains normallyoff at 300 °C. The cascode's gatejunction built-in potential variation with temperature was also extracted and plotted on the right axis of the graph of Fig. 15. As the temperature increases from 25 °C to 225 °C, the cascode's threshold voltage decreases by 0.54 V while its gate-junction built-in potential decreases by 0.52 V. This excellent agreement confirms that the decrease in cascode threshold voltage with temperature stems from the reduction of its gatejunction built-in potential as expected from theory. Thus, SiC JFETs, which have no gate oxides but rather use pn junctions to control the current flow

Figure 12. Blocking-voltage characteristics of the 0.143 cm<sup>2</sup> active area SiC JFET at gate biases of -4 to -24 V, in steps of -2 V.

The JFET blocks 1680 V.

Figure 14. Temperature dependence of the SiC cascode's ON-state drain current at  $V_{\rm GS}$  = 2.5 V.

Figure 13. Blocking voltages of two SiC JFETs fabricated on the same die of the same wafer. Edge termination increases blocking voltage from 450 V to 2022 V with no associated increase in device resistance.

Figure 15. Temperature dependences of the SiC cascode's threshold-voltage (left axis) and gate-junction built-in potential (right axis). At a temperature swing of 275 °C, the threshold voltage only shifts by 0.7 V.

through their gates, have remarkably stable threshold voltages. As the quality of the SiC MOSFET gate oxide is being aggressively improved, similar threshold voltage stability is expected in the near future.

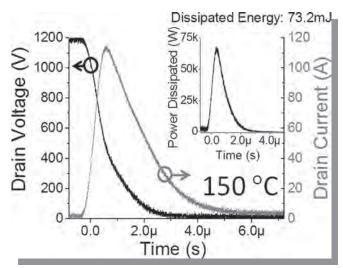

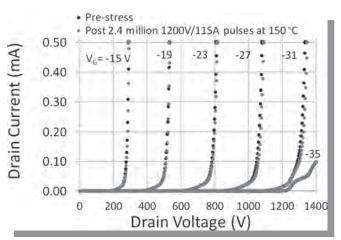

To demonstrate the ruggedness of SiC transistors, a SiC JFET was subjected to over 2.4 million 1200-V/115-A hard-switching events at what is 13 times its 150 °C rated current, Fig. 16 [10].

The JFET drain voltage is plotted in black (left axis) in Fig. 16; the current through the JFET is plotted in gray (right axis). By multiplying the JFET voltage by the current, the power dissipated by the JFET is calculated and plotted in the inset of Fig. 16. The energy dissipated by the JFET during each 1200-V/115-A switching transient is 73.2 mJ, and the peak dissipated power is 68.2 kW.

Figs. 17 and 18 show the ON-state current conduction and blocking voltage curves of the JFET before and after the 2.4 million 1200-V/ 115-A hard-switching events at 150 °C, respectively.

The black circles correspond to measurements taken prior to hard switching stressing. The gray circles represent measurements taken after the over 2.4 million hard switching events at 150 °C. As the JFET had not been subjected to burn-in stressing prior to the initiation of hard switch stressing, the slight improvement in the ON-state conduction JFET characteristics in Fig. 17 is attributed to burn-in effects stemming from the repetitive hard switching. The electrical characteristics do not degrade with stressing.

Figure 16. The 1200-V/115-A hard switching waveforms of the SiC JFET testing at 150 °C. The energy dissipated by the JFET during each hard switching event is 73.2 mJ (inset), and the peak dissipated power is 68.2 kW.

Figure 17. ON-state SiC JFET current conduction curves before (black circles) and after (gray circles) the over 2.4 million hard switching events at 150 °C. The slight improvement in JFET current conduction is attributed to burn-in of the JFET.

Figure 18. Blocking voltage SiC JFET curves before (black circles) and after (gray circles) more than 2.4 million hard-switching events at 150 °C and at 13 times the JFET's rated current. The blocking voltage characteristics are unchanged.

Therefore, the SiC transistor is rugged and operates reliably after the over 2.4 million hard switch stressing events at 13 times its 150 °C rated current.

SiC Schottky Barrier Diodes, planar and trench MOSFETs, and JFETs are commercially available as discrete components the voltage range of 650 V to 1700 V from several US. European and Asian companies. Suppliers also provide modules with multiple transistors and high currents. 3.3 kV MOSFETs will become commercially available from large manufacturers as early as 2021. Historically, the 1200 V SiC MOSFET released by Cree in 2011 was the first commercially available SiC transistor [11]. Today, the SiC MOSFET is the dominant SiC switch used in power electronics and has steadily gained market share. However, high device cost, reliability/ruggedness concerns, and the need for a workforce trained in SiC system insertion are barriers to mass adoption. In several applications, like PV systems, insertion of SiC reduces overall system cost compared to Si, even though SiC devices cost 2-3 more than their Si counterparts. This is due to the passive component and cooling system simplifications enabled by SiC high frequency operation and properties. Nevertheless, reducing SiC device cost is highly desirable. The SiC wafer represents 50-70% of the overall SiC device cost, a consequence of the unique substrate fabrication specifics outlined in the discussion of Fig. 2. A SiC device cost reduction of over

20% is expected with the transition from 150 mm to 200 mm substrates. Further cost reductions can occur with SiC device manufacturing in fabs alongside Si. SiC devices fabricated in large Si volume fabs exploit economies of scale that lower cost. Through re-purposing older fully depreciated 150 mm and 200 mm Si foundries, SiC power devices can be manufactured with the relatively small investments necessary to support unique SiC processing steps like high temperature implantation and anneal, and ohmic contact formation. Minimizing fabrication cost by exploiting the mature Si volume production assumes the fab is loaded close to capacity with standard Si and SiC processes running on the same line. In addition, aggregating the demand for SiC substrates and epilayers in volume fabs contributes to lower material costs. Lower fabrication costs in a fully depreciated Si+SiC "capacity" loaded fab, coupled with decreased material costs leads to significant price reductions for SiC devices. This approach offers a new opportunity for outdated Si foundries, which have not kept up with the channel length reductions of the last two decades, to continue manufacturing legacy Si parts while ramping up SiC fabrication that requires relatively modest 0.3 micron design rules [12].

Progress in the areas of materials and cleanroom fabrication can result in device yield and reliability improvements. More planar wafers, reduction of BPDs and process-generated defects, and higher quality gate oxides that reduce threshold voltage instability are all being addressed. Valuable data is being accumulated over years of field operation and is analyzed to drive device optimization. Independent facilities that perform reliability analyses of SiC devices have been established and contribute to "SiC user confidence" [13]. SiC devices can be made more rugged by leveraging design trade-offs. This, combined with intelligent gate drives, can provide safe-operating-areas that rival those of Si. Finally, a workforce well trained in SiC power electronics is key in creating the large device demand that will spur mass manufacturing with its costlowering benefits. Entities like PowerAmerica carry out University/industry applied collaborative projects, offer industry-driven WBG short courses and tutorials at conferences, and match students with industrial internship opportunities [14]. These activities train the existing workforce and prepare the next generation of SiC technologists, facilitating accelerated deployment of SiC power electronics.

#### References

[1] E. Jones, Fei Wang, D. Costinett, "Review of Commercial GaN Power Devices and GaN-Based Converter Design Challenges," IEEE Journal of Emerging and Selected Topics in Power Electronics, Vol. 4, No. 3, 2016, p. 707. [2] E. Van Brunt, A. Burk, D. J. Lichtenwalner, R. Leonard, S. Sabri, D. A. Gajewski, A. Mackenzie, B. Hull, S. Allen, and J. W. Palmour. "Performance and Reliability Impacts of Extended Epitaxial Defects on 4H-SiC Power Devices," Materials Science Forum, vol. 924, Trans Tech Publications, Ltd., June 2018, pp. 137-142. [3] A. Agarwal, H. Fatima, S. Haney, and S.-H. Ryu, "A new degradation mechanism in high-voltage SiC powerMOS-FETs," IEEE Electron Device Lett., vol. 28, no. 7, pp. 587-589, Jul. 2007.

[4] V. Veliadis, H. Hearne, E. J. Stewart, M. Snook, W. Chang, J. D. Caldwell, H. C. Ha, N. El-Hinnawy, P. Borodulin, R. S. Howell, D. Urciuoli, and C. Scozzie, "Degradation and full recovery in high-voltage implanted-gate SiC JFETs subjected to bipolar-current stress," IEEE Electron Dev. Lett., Vol. 33, No. 7, pp. 952–954, 2012. [5] V. Veliadis, "Silicon Carbide Junction Field Effect Transistors (SiC – JFETs)" in "Wiley Encyclopedia of Electrical and Electronics Engineering", 2014, pp. 1–37.

[6] V. Veliadis, T. McNutt, M. Snook, H. Hearne, P. Potyraj, and C. Scozzie, "A 1680V(at1mA/cm²),54A(at780W/cm²)

normally-ON 4H-SiC JFET with 0.143 cm<sup>2</sup> active area," IEEE Electron Dev. Lett., Vol. 29, No. 10, pp. 1132–1134, 2008

[7] V. Veliadis, M. Snook, T. McNutt, H. Hearne, P. Potyraj, A. Lelis, and C. Scozzie, "A 2055-V (at 0.7 mA/cm²), 24-A (at 706 W/cm²) normally-ON 4H-SiC JFET with 0.068-cm² active area and blocking voltage capability of 94% of the SiC material limit," IEEE Electron Dev. Lett., Vol. 29, No. 12, pp. 1325–1327, 2008.

[8] V. Veliadis, T. McNutt, M. McCoy, H. Hearne, P. Potyraj, and C. Scozzie, "Large area silicon carbide VJFETs for 1200 V cascode switch operation," International Journal of Power Management Electronics Vol. 2008, (2008), ID. 523721.

[9] V. Veliadis, H. Hearne, T. McNutt, M. Snook, P. Potyraj, and C. Scozzie, "VJFET based all-SiC Normally-Off Cascode Switch for High Temperature Power Handling Applications," Materials Science Forum, Vols. 615-617, pp. 711–714, 2009.

[10] V. Veliadis, B. Steiner, K. Lawson, S. B. Bayne, D. Urciuoli, H. C. Ha, N. El-Hinnawy, S. Gupta, P. Borodulin, R. S. Howell, and C. Scozzie, "Reliable Operation of SiC JFET Subjected to Over 2.4 Million 1200-V/115-A Hard Switch Stressing Events at 150 °C," IEEE Electron Dev. Lett., Vol. 34, No. 3, pp. 384–386, 2013.

[11] https://www.cree.com/news-media/news/article/cree-launches-industry-s-first-commercial-silicon-carbide-power-mosfet-destined-to-replace-silicon-devices-in-high-voltage-1200-v-power-electronics

[12] V. Veliadis, "Empowering power electronics with PowerAmerica," Compound Semiconductor Magazine Vol. 25, Nov/Dec. 2019 p. 36.

[13] PowerAmerica portfolio of projects, http://poweramericainstitute.org/

[14] V. Veliadis, "The Impact of Education in Accelerating Commercialization of Wide-Bandgap Power Electronics," IEEE Power Electronics Magazine, June 2019, p. 62.

## A REVIEW OF THE 22ND INTERNATIONAL VACUUM ELECTRONICS CONFERENCE (IVEC)

NATANAEL AYLLON, ROBERTO DIONISIO, FELIX MENTGEN EUROPEAN SPACE AGENCY E-MAIL: FELIX. MENTGEN@ESA.INT

The 22nd edition of the International Vacuum Electronics Conference (www.ivec2021.org) was held in a virtual platform from the 27 to 30 April this year with the technical cosponsorship of the IEEE EDS society. IVEC was created in the year 2000 by merging the US Power Tubes conferences and the European Space Agency TWTA Workshops.

Originally it was foreseen to hold this year's edition of the conference as a face-to-face event in the WTC conference center in Rotterdam, The Netherlands. Quite soon though it became clear that this was not going to be possible due to the restrictions in international travel and the event was converted into a fully virtual conference using the "Let's Get Digital" online platform.

By using the virtual platform, the organising committee was able to organise a conference which overcame the obstacles resulting from the worldwide travel restrictions and offered a highly interesting conference to all the participants.

To make the event a success, a novel conference concept was needed which combined the advantages of both in-person and virtual events. In this concept, there were three important aspects. First the conference should continue to focus on the established elements of IVEC like the plenary talks, the paper presentation sessions and the awards. Second, the

conference should enable as much interaction between the participants as possible since this is the aspect which is inhibited the most in virtual conferences. Third, the conference should also have some novelties like the introduction of a new topic family, nano vacuum electronics.

With the new concept ready, the organisation could begin.

The first mentioned aspect was the most straightforward one, with the help of the technical programme committee, exactly 200 papers were accepted and a total of 20 oral paper presentation sessions could be put together. The topics of the sessions ranged from Traveling Wave Tubes over Thermionic Emission to Free Electron lasers and gave a good overview over the current research trends in the vacuum electronics community.

In addition to this, 4 plenary speakers gave more extensive talks about their current research and development projects. Yaxin Zhang from UESTC talked about Terahertz Vacuum Electron Devices and Applications in High-Rate Communication and Imaging Systems, Ernst Bosch from Thales lectured about Electric propulsion—Game Changer for Satellites and New Possibilities for Applications, Dimitris Pavlidis from the University of Florida gave an interesting talk about Vacuum Nanoelectronics Based on Si and III-Nitride Semiconductors and Erk Jensen from

CERN gave an overview over The Role of Vacuum Electronics in Future Particle Accelerators.

For everyone willing to extend their knowledge about vacuum electronics there were also a number of mini courses covering topics of general RF and vacuum electronics theory, manufacture and applications. Given that this year's IVEC was organised mainly by members of the European Space Agency, the selection of courses put part of the focus on the space applications of vacuum electronics.

The second aspect of the conference concept was the intention to create as much interaction between all the participants as possible.

With innovative ideas it was possible to get people from across the world to interact using all the means that the virtual conference platform offered. The elements of the live programme hereby closely followed a classical in-person scheduling. This meant that there were live opening and closing ceremonies, live plenary talks, live award ceremonies and one live keynote speech in each oral paper presentation session which were led by a live chairperson. On top of all of this there were live Q&A sessions that came along with each of the aforementioned parts. The recording of all the live content gave the participants an additional opportunity to follow or re-watch all the content at

Geographical regions introduced to facilitate attending IVEC 2021 by participants from different time zones

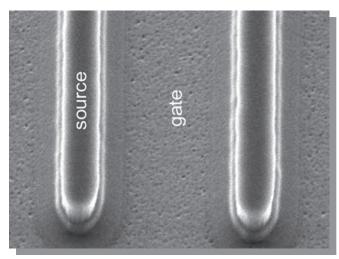

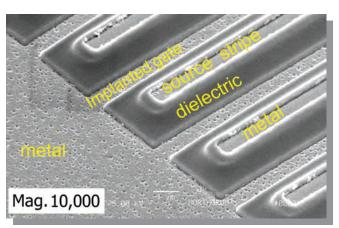

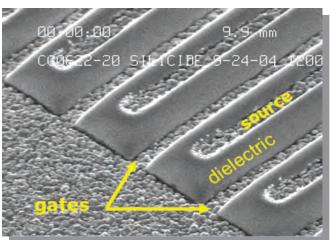

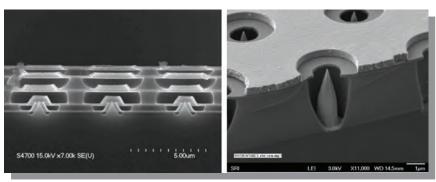

Examples of SEM images of devices presented at the vacuum nanoelectronics sessions

any time for a number of weeks after the end of the conference.

With participants coming from all over the world, it would have not been possible to set up a schedule that allowed for everyone to take part in all the live content. Instead it was decided to define two main geographical regions, one region being EU-Asia and the other region being the Americas. A distributed conference schedule was then set up with each live element taking place at a convenient time for either the EU-Asia region or the Americas region. This enabled people within each region to participate in part of

the live program at times that were convenient for them, thus greatly increasing the interaction. Of course all participants could always join any session, even the ones scheduled at times more convenient to other regions. With this programme arrangement, the conference saw many interesting and fruitful discussions during the Q&A sessions of the plenaries and oral paper presentation sessions. As the live interactions between people are what keeps a scientific community alive, we believe that with this year's concept, IVEC could get as close as possible to an in-person event.

The third aspect of the conference concept was the introduction of a new topical group, nano vacuum electronics. Researchers from this up and coming field study special nanofabricated structures made mostly from semiconducting materials. Due to their size at nano-scale they are much smaller than the average free path length of electrons in air at ambient pressure. Therefore these devices behave as if they were placed in a vacuum, even though they are not. As a result, they exhibit properties of both classical vacuum electronics and solid state electronics. These structures can for example be integrated with a high density and at the same time be very tolerant to environmental effects like radiation, making them interesting for many different applications.

To put enough attention to this new topic and properly introduce it to the IVEC community, there was a mini-course focused on nano vacuum electronics for space applications by Jin-Woo Han from USRA NASA AMES research center. The plenary talk of Dimitris Pavlidis from

University of Florida focused also on this topic. With this and with enough submissions from the scientific community, one entire oral paper presentation session could be devoted to nano vacuum electronics.

Initially there was some uncertainty as to whether there would be a high interest in the conference even with the new digital platform since the previous year's IVEC had only taken place six months before. The reason for this was that the first wave of COVID-19 hit around the time that IVEC 2020 had been scheduled and the organisers were forced to move the event to a later date in order to be able to react to the changing situation.

But with over 260 participants from 11 countries, this year's event was well-attended and showed the community's persistent interest in this conference even in its second year of going virtual.

Over the four days of the conference, there was a lot of active participation in all Q&A sessions, overall demonstrating that the conference concept showed the desired outcomes.

Thanks to the selection committees, the three awards traditionally awarded at IVEC went to researchers in recognition of their excellent scientific work.

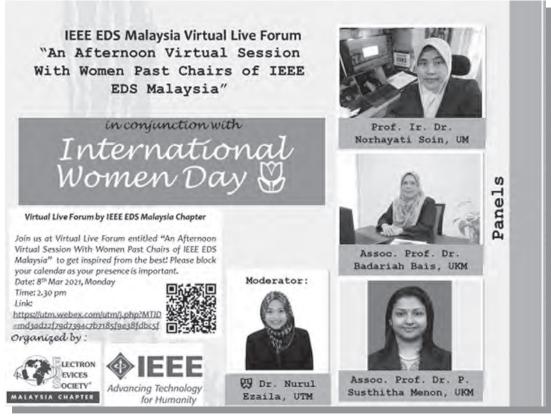

Gun-Sik Park