JULY 2022 VOL. 29, NO. 3 ISSN: 1074 1879

**EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI**

### TABLE OF CONTENTS

| 75TH ANNIVERSARY OF THE TRANSISTOR   |

|--------------------------------------|

| TECHNICAL BRIEFS                     |

| UPCOMING TECHNICAL MEETINGS          |

| SOCIETY NEWS                         |

| EDS AWARDS AND CALLS FOR NOMINATIONS |

| EDS WOMEN IN ENGINEERING             |

| EDS YOUNG PROFESSIONALS              |

| EDS HUMANITARIAN PROJECTS            |

| CHAPTER NEWS                         |

| REGIONAL NEWS44                      |

| EDS MEETING CALENDAR                 |

| EDS STRATEGIC PLANNING UPDATE        |

# **IEEE**

# 75TH ANNIVERSARY OF THE TRANSISTOR

# HISTORY AND EMERGING DESIGNS OF POWER TRANSISTORS

B. Jayant Baliga North Carolina State University

Electricity was playing a major role in the lives of people by the middle of the 20th century. Electric lighting, pioneered by Edison, had improved productivity, quality of life, and safety by illumination of our streets,

factories, and residences. Refrigeration, enabled by efficient motors, had transformed the storage of perishable foods in homes while preserving them during delivery from farms to the market. The replacement of mechanical actuators for these application with electronic switches became a possibility after the invention of the bipolar transistor (Shockley, Bardeen, and Brattain, Bell Labs, 1947). For applications operating at high power levels, the ideal electronic switches must exhibit the following characteristics: (a) high voltage blocking capability; (b) low on-state voltage drop to reduce conduction losses; (c) fast switching capability for the voltage and current to minimize switching losses; (d) ability to tolerate simultaneous imposition of high voltage and current during the switching transient for ruggedness; (e) control of current using a small voltage with low drive currents to allow integration of the drive electronics; and (f) current saturation under drive voltage control to avoid the need for snubber elements. In addition, an ideal power transistor should be able operate symmetrically in the first and third quadrants. The quest to create a power transistor that satisfies these requirements has driven innovations in the technology during the last 60 years.

This article highlights important power transistor innovations that have occurred since the 1960s allowing displacement of analog power control (phase control) with digital power control (pulse width modulation). These innovations initially required changes in device architecture and physics for silicon based transistors. Subsequently, even greater performance enhancements were achieved by

### **ELECTRON DEVICES** SOCIETY

President

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

**President-Elect**

Bin Zhao Freescale Semiconductor Email: bin.zhao@ieee.org

Treasurer Roger Booth Qualcomm

Email: boothrog@yahoo.com

**Secretary** M.K. Radhakrishnan NanoRel Email: radhakrishnan@ieee.org

Sr. Past President

Fernando Guarin GlobalFoundries Email: fernando.guarin@ieee.org

Vice President of Education

Navakanta Bhat

Indian Institute of Science Email: navakant@gmail.com

Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

Vice President of Membership and Services

Merlyne de Souza University of Sheffield Email: m.desouza@sheffield.ac.uk

Vice President of Publications and Products

Arokia Nathan University of Cambridge Email: an299@cam.ac.uk

Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

Vice President of Strategic Directions

Doug P. Verret IEEE Fellow

Email: dougverret@gmail.com

Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) **Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2022               | TERM   | 2023               | TERM | 2024                 | Term |

|--------------------|--------|--------------------|------|----------------------|------|

| Constantin Buluce  | a (2)  | Roger Booth        | (2)  | Mario Aleman         | (1)  |

| Daniel Mauricio    |        | Xiaojun Guo        | (1)  | Paul Berger          | (2)  |

| Camacho Montejo    | (2)    | Edmundo A.         |      | Yogesh Singh Chauhan | (1)  |

| John Dallesasse    | (2)    | Gutierrez-D.       | (2)  | Patrick Fay          | (1)  |

| Mario Lanza        | (2)    | Francesca lacopi   | (1)  | Kazunari Ishimaru    | (2)  |

| Geok Ing Ng        | (2)    | Benjamin Iniguez   | (2)  | Bill Nehrer          | (2)  |

| Claudio Paoloni    | (2)    | P. Susthitha Menon | (1)  | Merlyne de Souza     | (2)  |

| Hitoshi Wakabayash | ni (2) | Manoj Saxena       | (2)  | ,                    |      |

| ,                  |        | Sumant Sood        | (2)  |                      |      |

### **NEWSLETTER EDITORIAL STAFF**

#### Editor-In-Chief

Daniel Tomaszewski

Institute of Microelectronics and Photonics Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### Associate Editor-in-Chief

Manoj Saxena Deen Dayal Upadhyaya College

University of Delhi Email: msaxena@ieee.org

REGIONS 1-6, 7 & 9 Eastern, Northeastern & Southeastern USA (Regions 1, 2 & 3)

Rinus Lee TEL Technology Center, America Email: rinuslee@ieee.org

Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University Email: mmadachi@sfu.ca

Southwestern & Western USA (Regions 5 & 6)

Lawrence Larson Texas State University Email: Larry.Larson@ieee.org

Latin America North (Region 9)

Joel Molina Reyes INAOE

Email: jmolina@inaoep.mx

Latin America South (Region 9) Paula Ghedini Der Agopian

UNESP, Sao Paulo State University Email: paula.agopian@unesp.br

**REGION 8** Scandinavia & Central Europe

Marcin Janicki Lodz University of Technology Email: janicki@dmcs.pl

### United Kingdom, Middle East & Africa

Stewart Smith Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

### Western Europe

Mike Schwarz Mittelhessen University of **Applied Sciences** Email: mike.schwarz1980@ googlemail.com

### REGION 10

#### Australia, New Zealand & South East Asia

Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University

Email: thhou@mail.nctu.edu.tw

#### South Asia

Soumya Pandit University of Calcutta Email: soumya\_pandit@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission.

### Newsletter Deadlines

**I**SSUE **DUE DATE** October July 1st October 1st January January 1st April Jüly April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright @ 2022 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

### HISTORY AND EMERGING DESIGNS OF POWER TRANSISTORS

(continued from page 1)

replacing silicon with wide band gap semiconductor materials.

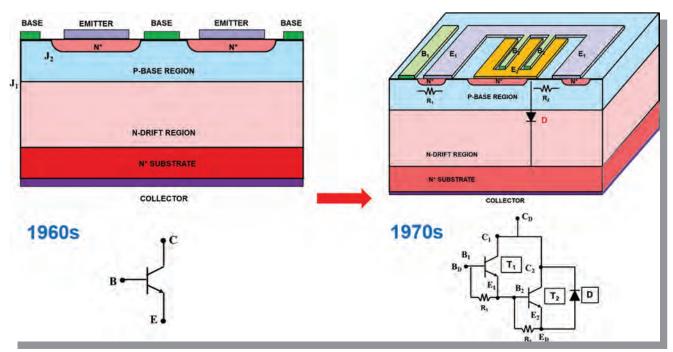

The power bipolar transistor architecture (Fig. 1 left) was a departure from the signal transistor due to the need for supporting the high voltages and controlling the high currents required in power applications. The power transistor requires a vertical structure with one of the high current terminals (collector) located at the bottom of the chip, with the other high current terminal (emitter) formed at the top. The base terminal must be interdigitated with the emitter because on-state current flow concentrates at the emitter edges due to the emitter crowding effect. A thick drift region with low doping concentration is required to support the high voltages, resulting in a large on-state resistance despite some conductivity modulation. Most significantly, a large base width is necessary to avoid reachthrough limited breakdown, resulting in a low current gain (typically < 10 in the on-state). A large reverse base drive current is needed during turn-off to shorten the storage time, resulting in a current gain of only 2. Bulky and complex base drive circuits were consequently needed, which created reliability issues. The safe operating area of the power bipolar transistor was also poor, making addition of snubber components necessary.

The Darlington power bipolar transistor (Fig. 1 right) was developed to ameliorate the problem with low onstate current gain. It utilizes a base drive transistor T<sub>1</sub> to provide drive current to the output transistor T2, as shown by its equivalent circuit in Fig. 1. This approach allowed increasing the current gain in the on-state but the turn-off gain was still poor. More significantly, the Darlington power transistor has a diode-like on-state characteristics because of current flow of transistor T<sub>1</sub> through the base-emitter junction of transistor T2. This makes its on-state voltage drop much larger than the single bipolar transistor.

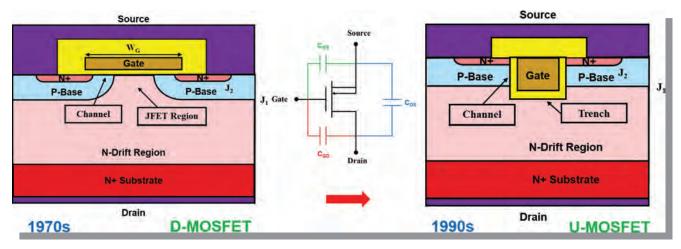

The availability of the CMOS technology for integrated circuits enabled making power Metal-Oxide-Semiconductor Field Effect Transistors (MOSFETs) in the 1970s. The doublediffused or D-MOSFET (Fig. 2 left) was first commercialized by several companies (International Rectifier, Siliconix). It's channel length is determined by the difference in diffusion depths of the P-base and N+ source regions, allowing short channel length (1 to 1.5 µm) to be achieved with 5 µm lithography process tolerances at that time. This device also has a vertical structure that contains a thick drift region with low doping concentration to support high voltages. It adds substantial on-state resistance for devices with high blocking voltages. On-state current flow occurs when a positive gate drive voltage is applied to the gate to induce an inversion layer at the surface of the P-base region to create a channel. The resistances of the channel and JFET regions contribute substantially to the total on-resistance for devices with low blocking voltages (< 100 V). This device exhibited most of the desired characteristics for the

Figure 1. Evolution of Power Bipolar Transistors.

Figure 2. Evolution of Power Metal-Oxide-Semiconductor Field Effect Transistors.

ideal electronic switch when the blocking voltage was less than 100 V.

The quest to realize lower on-resistance lead to the introduction of the power U-MOSFET (Fig. 2 right) by the industry in the 1990s (Siliconix). The JFET region resistance was eliminated using this structure allowing increasing the channel density as well. The U-MOSFETs reduced the on-resistance by a factor 3x for devices with  $30\,V$  ratings. However, the input capacitance for the devices ( $C_{GS}$  in the equivalent circuit in Fig. 2) increased substantially slowing down the switching speed. However, the overall performance im-

provement made this structural design dominant in the 1990s.

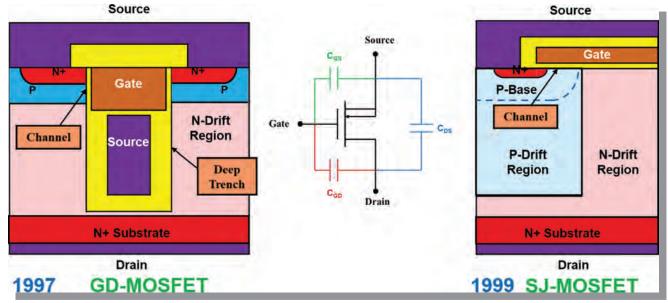

A major breakthrough in enhancing the performance of silicon power MOSFETs occurred with the introduction of the two-dimensional charge-coupling concept in the 1990s. The first approach (Baliga, NCSU, U.S. Patent 5,637,898, 1997) was proposed with a source electrode inside a deep trench to produce the desired 2D charge-coupling. The GD-MOSFET (Fig. 3 left) with a linearly graded doping profile in the drift region was shown to greatly improve the electric field distribution in the drift region, al-

lowing increasing its doping concentration far above (> 10x) that possible with the previous designs shown in Fig. 2. This approach reduced the drift region resistance well below what was previously considered the limit for ideal on-resistance for silicon material. The device structure, now commonly called the split-gate MOSFET (a misnomer because it contains only one gate electrode), has become the most popular product manufactured by leading power device companies (Alpha and Omega, Infineon) with blocking voltages up to 150 V. These devices are widely used for building

Figure 3. Evolution of Power Metal-Oxide-Semiconductor Field Effect Transistors.

power supplies to serve microprocessors and graphics chips in desktop and laptop computers.

The second approach (Lorenz, Infineon, ISPSD 1999) utilized a vertical junction produced by the addition of a deep P-type drift region operating in parallel with the N-type drift region to achieve the 2D charge-coupling. This device design (Fig. 3 right), commonly referred to as the super-junction (SJ) MOSFET, has become popular for making products with blocking voltages of 600 - 900 V. These devices are used in motor drive applications when switching losses are dominant. Products are available from many companies. (Infineon, ST Microelectronics).

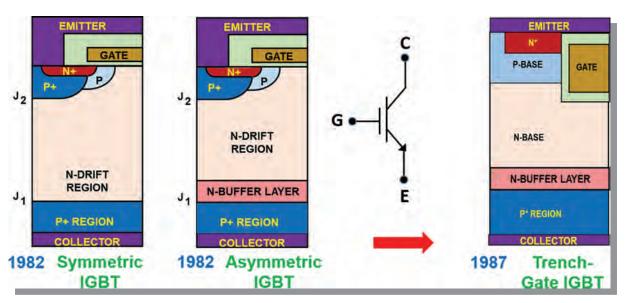

The Insulated Gate Bipolar Transistor (IGBT) was invented, developed and commercialized in the early 1980s to replace the bipolar junction transistor due to its many short-comings (Baliga, General Electric, U.S. Patent 4,969,028, Filed 1980, Issued 1990). The device structure (Fig. 4 left) can be designed to be capable of blocking voltage in the first and third quadrant (Symmetric IGBT) at junctions J<sub>1</sub> and J<sub>2</sub> or only in the first quadrant (Asymmetric IGBT). The IGBT operates by creating an MOS-channel using a positive gate bias, which delivers the base drive current to the internal wide-base P-N-P bipolar transistor. Collector cur-

rent flow is generated using both electrons via the channel and holes via the P-N-P transistor within the same drift region, called MOS-bipolar current transport. The device can be turned-off by reducing the gate voltage to zero to shut off the electron supply. The holes in the drift region are removed by recombination, creating a current tail that produces switching losses.

The proposed IGBT design was a radical departure because of employing a wide-base P-N-P transistor rather than the narrow-base N-P-N transistors used for power transistors at that time. Skeptics believed that this would severely limit the current flow making the device inferior to power bipolar transistors. My analysis, based upon high level injection physics within the N-base region (N-drift region), predicted P-i-N rectifier like on-state characteristics with low on-state voltage drop even at high current densities. This analysis was fortunately proven to be correct when actual devices were fabricated and tested.

A major hurdle for the IGBT was potential latch-up of the internal 4-layer thyristor, which could result in destructive failure. This issue was overcome using the deep P+ region (Fig. 4 left) added to the basic doublediffused MOSFET process (Baliga and

Adler, General Electric, U.S. Patent 4,443,931, 1984). The IGBT was then believed to be limited to low operating frequencies, thus constraining its applications, because methods to control the minority carrier lifetime at that time led to damaging the MOS gate structure. Fortunately, I discovered a process that allowed using high energy electron irradiation to reduce the lifetime in the drift region followed by a low temperature annealing process that removed the damage in the gate oxide. This was crucial to creating IGBTs that could operate over a large range of switching speeds (Baliga, IEEE EDL, 1983), opening up a wide spectrum of applications within GE at first and then beyond.

Based on my pitch in November 1980 projecting wide-spread impact of the IGBT within the Motor Drives, Lighting, Appliances, and Medical divisions at the General Electric Company, the Chairman, Jack Welch, approved full support for my development and commercialization of the IGBT. Based on this support, I was able to engineer and build the IGBT directly in the power MOSFET manufacturing line in less than 10 months. This had to be accomplished with no flaws during chip design and process definition, to ensure first pass success, due to the intense corporate scrutiny.

Figure 4. Evolution of Insulated Gate Bipolar Transistors (IGBTs).

This was a critical step in making the IGBT available in large quantities for use at GE to build the first adjustable speed motor drives for heat pumps, and novel lamps that were precursors of the compact fluorescent lamps that became commercially viable in the 1990s. Jack Welch embargoed any publication of information regarding the IGBT due its value to GE applications. This embargo was eventually broken by announcement of an IGBT product D94F4 by the Semiconductor Products Division in June 1983. It's applications were promoted by GE (Baliga and Smith, IEEE APEC, 1983), which resulted in a "Product of the Year" Award. After the release of my publications by GE on the attributes of the IGBT from 1983 to 1985, products were developed and introduced by many companies (Toshiba, Mitsubishi Electric, Fuji Electric) in Japan starting in 1985.

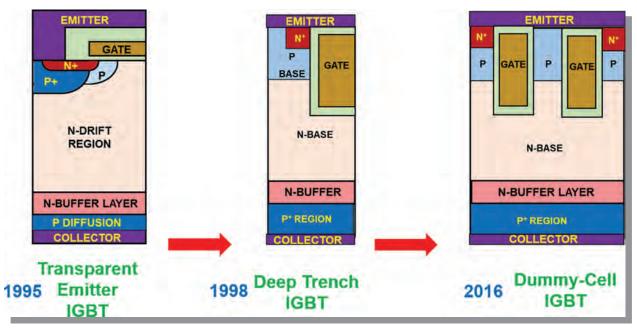

IGBT innovations were also made in Europe (ABB, Siemens) in the 1990s with the transparent emitter design (Fig. 5 left). The P+ emitter region was replaced with a thin P-diffusion on the bottom of the wafer with low doping concentration to reduce the injection efficiency. This was found to reduce switching losses for very high voltage

(> 4 kV) devices required to replace gate-turn-off (GTO) thyristors used for electric locomotive drives. This technology was rapidly optimized in Europe and Japan for wide spread use in urban and long distance public transportation.

An improvement to the trade-off between the on-state voltage drop and switching speed for the IGBT was achieved by employment of the trench-gate structure (Chang and Baliga IEEE IEDM, 1987). The trenchgate design (Fig. 4 right) increases channel density, providing more drive current to the internal bipolar transistor, to reduce on-state voltage drop. Another IGBT design innovation that was shown to improve the performance of high voltage IGBT devices was the deep trench structure (Toshiba, IEEE ISPSD, 1998) with a narrow P-base region (Fig. 5). This approach enhanced the conductivity modulation of the drift region resulting in lower on-state voltage drop.

Over the last 4 decades, the IGBT has become very popular for a large variety of applications (Baliga, The IGBT Device, Elsevier, 2015). It is used in all sectors (transportation, lighting, consumer, industrial, medical, etc.) of the economy to enhance the quality

of life for billions of people around the world. The creation of the electronic ignition system using IGBTs for gasoline powered cars and trucks has reduced gasoline consumption by 1.8 trillion gallons from 1990-2020. The development of adjustable speed motor drives using IGBTs has reduced electricity consumption by 73,000 Tera-Watt-Hours from 1990-2020. The deployment of 20 billion compact fluorescent lamps using IGBT electronic ballasts has reduced electricity consumption by 59,900 Tera-Watt-Hours from 1990-2020. These applications of the IGBT have saved consumers \$ 33.6 Trillion while reducing carbon-dioxide emissions by 181 Trillion pounds from 1990-2020 to mitigate global warming.

All solar and wind power generation relies upon using the IGBT to convert the energy into a stable 50 or 60 Hz AC power that can be delivered to the grid. In addition, the IGBT is used for the inverters for driving the motors in electric cars manufactured by all automobile companies. It will therefore play an essential role in the elimination of fossil fuels in the electricity generation and transportation sectors to combat climate change.

Figure 5. Evolution of Insulated Gate Bipolar Transistors (IGBTs).

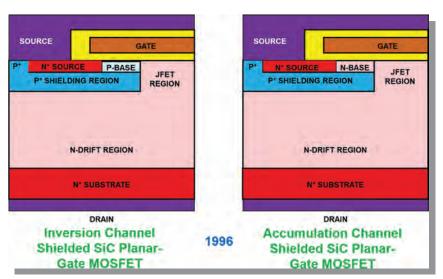

The history of evolution of power devices includes a quantum leap in performance that was enabled by wide band gap semiconductor materials. The impact of replacing silicon with wide band gap semiconductors was first recognized by the derivation of an equation relating the drift region resistance in a vertical unipolar power device to the basic material properties, now commonly called Baliga's Figure-of-Merit or BFOM (Baliga, GE, JAP, 1983; IEEE EDL, 1989). This equation predicted 13.7-fold reduction in resistance by using gallium arsenide and more than 100-fold reduction in resistance by using silicon carbide (SiC). The theory was validated in the 1990s, after the availability of 6H-SiC wafers, by fabricating 400 V Schottky rectifiers (Bhatnagar, McLarty and Baliga, IEEE EDL, 1992) and subsequently the first high performance SiC power MOSFETs. (Shenoy and Baliga, IEEE EDL, 1997). This required altering the power MOSFET structure to (a) shield the P-base region to prevent reach-through breakdown; (b) shield the gate oxide from high electric fields; and (c) employing accumulation channels to increase the channel mobility. The 4H-SiC planar-gate MOS-FET structures that are now commercially available employ the shielded structures (Baliga, NCSU, U.S. Patent 5,543,637, 1996) with accumulation or inversion channels (Fig. 6).

The D-MOSFET process used for silicon power MOSFETs cannot be used for SiC devices due to insignificant diffusion of dopants in this material even at very high temperatures that lead to sublimation. The channel is therefore formed by staggered ion-implantation of the P and N-type dopants used to form the P-base and N<sup>+</sup> source regions (Bhatnagar and Baliga, U.S. Patent 5,322,802, 1994; Shenoy, Cooper and Melloch, IEEE EDL, 1997). This requires high resolution photolithography to create the sub-micron channel lengths needed to achieve a low on-state resistance in the power MOSFETs. Commercial SiC planar-gate power MOSFETs are

Figure 6. Evolution of Planar-Gate Silicon Carbide Power MOSFETs.

manufactured using this technology.

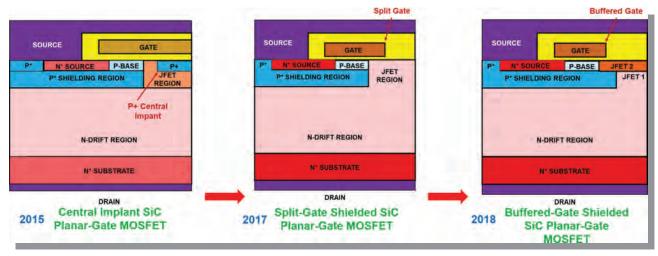

The reduction in switching power losses in motor drives by replacement of silicon IGBTs with SiC power MOSFETs was projected (Baliga, NCSU, Proceedings IEEE, 1994) and subsequently experimentally demonstrated (Fabre, et al., ALSTHOM, IEEE TPE, 2015). However, the cost of SiC power MOSFETs is at present more than 3-times that for the equivalent rated silicon IGBT, impeding its commercial viability. The strategy undertaken by the industry to overcome the higher cost of this technology is to operate the power electronics at a much higher frequency to reduce the cost of passive elements, such as inductors and filters, to offset the semiconductor cost. The operation of SiC power MOSFETs at higher frequencies requires design innovations to reduce drain current and voltage transient times during switching. Faster drain voltage transient times during switching can be achieved in SiC power MOSFETs by reducing the gate-drain charge.

One innovative design (Fig. 7 left) to achieve this employs a centralimplanted P+ region inside the JFET region (Zhang, et al., CREE, IEEE ISPSD, 2015). Additional process steps are required to add the P+ region and it must be connected to the source electrode orthogonal to the

cross-section. The second innovative approach (Fig. 7 middle) is the splitgate device design (Han, Baliga, and Sung, NCSU, IEEE EDL, 2017) where the width of the gate electrode is shortened over the JFET region. This design reduces the gate-drain charge by a factor of 2.4-times without any additional process steps. The third innovative design approach (Fig. 7 right) is the buffered-gate design (Han, Baliga, and Sung, NCSU, IEEE EDL, 2018) where the edge of the P+ shielding region is extended beyond the edge of the split-gate electrode. This design reduces the gate-drain charge by a factor of 6-times but requires an additional process step to include a second JFET region.

In typical voltage source inverters using the H-bridge topology with silicon IGBTs, it is necessary to connect an anti-parallel diode for operation of the adjustable speed drive for motors. In principle, the anti-parallel diode is not required for the SiC power MOSFET due to current flow via the P-N body diode. However, this approach has been found to result in high switching power losses due to the bipolar diode reverse recovery phenomenon at elevated temperatures. In addition, a phenomenon called bipolar degradation of the SiC power MOSFET was discovered where defects are generated in the

Figure 7. Evolution of Planar-Gate Silicon Carbide Power MOSFETs.

drift region due to the P-N diode bipolar current flow. A discrete junction barrier controlled Schottky (JBS) diode (Baliga, GE, IEEE EDL, 1984; Held, Kaminski, and Niemann, ABB, Material Science Forum, 1998) can be connected across the SiC power MOSFET to prevent current flow via the body diode. This adds another packaged component with significant SiC chip area and cost. An innovative design (Fig. 8) integrates the JBS diode into the SiC power MOSFET cell structure (Sung and Baliga, NCSU, IEEE EDL, 2016). This structure was created by engineering the source contact process to simultaneously

P\* N' SOURCE P-BASE

P\* SHIELDING REGION

N-DRIFT REGION

N' SUBSTRATE

DRAIN

SIC Planar-Gate

JBSFET

Figure 8. Evolution of Silicon Carbide Power MOSFETs.

make a Schottky barrier contact to the drift region at the JBS diode and ohmic contacts to the N<sup>+</sup> source and P<sup>+</sup> shielding regions.

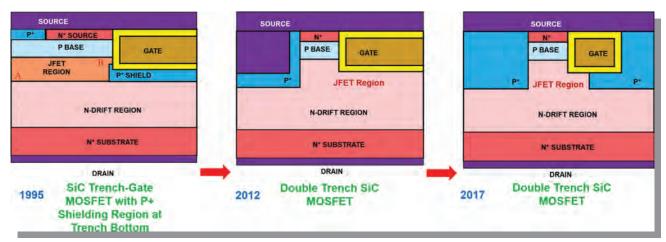

As in the case of silicon power MOSFETs, trench-gate technology can be employed for SiC power MOS-FETs to reduce the on-state resistance due to elimination of the JFET region and increase in channel density. The major challenge for this approach is a very high electric field in the gate oxide at the bottom of the trench that can lead to unreliable operation and even catastrophic failure. The first innovative design (Fig. 9 left) to solve this problem utilizes a P+ shielding region at the bottom of the trench which is connected to the source electrode orthogonal to the cross-section (Baliga, NCSU, U.S. Patent 5,396,085, 1995; Li, Cooper and Capano, Purdue University, IEEE EDL, 2002). The second approach (Fig. 9 middle) makes use of two trench regions (Harada, et al, Rohm, IEEE ISPSD, 2012), one to form the gate structure and a second deeper one for shielding the gate oxide. The third approach (Fig. 9) right) makes use of a shallow trench to form the gate structure and two deeper trenches to shield the gate oxide (Peters, et al, Infineon, PCIM 2017). In all three designs, a JFET region is created when shielding the gate oxide, which must be adequately doped to reduce the on-state resistance

without degrading the breakdown voltage. Good on-state resistance, breakdown voltage and gate oxide shielding was observed with the first approach, while the lowest gate oxide electric field was observed for the third approach with a higher on-state resistance (Agarwal, Han and Baliga, NCSU, IEEE WiPDA, 2018).

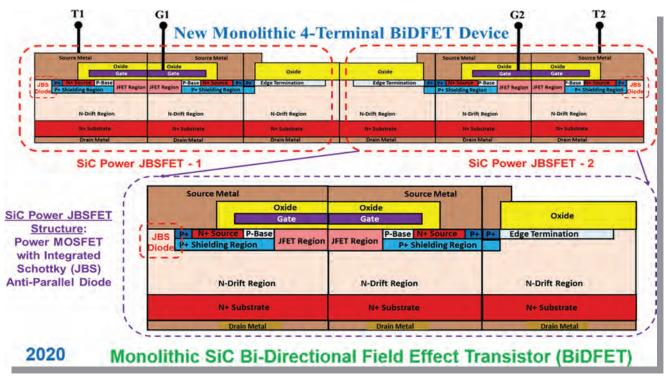

As mentioned in the beginning of this article, the 'holy grail' for the power semiconductor community during the last 60 years has been to create a power switch with symmetric behavior in the first and third quadrants, gate voltage controlled output characteristics with current saturation, low on-state voltage drop, and fast switching capability. Power electronics engineers have used multiple discrete devices to assemble such a switch for use in matrix converters (Baliga and Han, NCSU, GOMACTech, 2018). A compact, monolithic 4-terminal bi-directional power switch, named the BiDFET, has been recently achieved (Baliga, NCSU, U.S. Patent 10,804,393, 2020; Han, et al., NCSU, IEEE ISPSD, 2020) by integration of two JBSFETs (Fig. 10). These devices will enable a new generation of power electronics that is more compact and efficient.

Excellent power devices can also be created using another wide bad gap semiconductor, gallium nitride (GaN). The ability to grow device

Figure 9. Evolution of Trench-Gate Silicon Carbide Power MOSFETs.

Figure 10. Monolithic SiC Bi-Directional Field Effect Transistor (BiDFET).

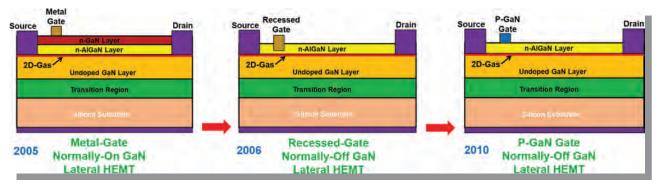

quality epitaxial layers of GaN on low cost, large diameter, silicon substrates is a unique attribute of this approach. However, this requires fabrication of lateral high voltage power devices with inter-digitation of the drain, gate, and source electrodes, which can make the chip design challenging due to current crowding and parasitic metal resistances. The formation of a twodimensional electron gas (commonly referred to as a 2D-gas) at the interface

between GaN and aluminum gallium nitride (AlGaN) creates a layer with low sheet resistance to reduce onstate resistance. The first devices (Fig. 11 left) used a metal-gate (Schottky barrier) contact that produced normally-on behavior in the high-electronmobility-transistor (HEMT) device. Since this is unacceptable for use in power circuits, this design was combined with a low-voltage silicon MOS-FET to form the Baliga-Pair or Cascode topology (Baliga, NCSU, U.S. Patent 5,396,085, 1995; Transphorm and IRF products). Subsequently, normallyoff GaN HEMT devices (Fig. 11 middle and right) were created using the recessed gate design (Saito, et al., IEEE TED, 2006) and P-GaN gate region (Holt, et al., IEEE IPES, 2010). The lateral configuration of these devices allows making multiple power transistors on the same chip to build compact power integrated circuits for applications

Figure 11. Gallium Nitride Lateral HEMT Power Devices.

such as laptop and cellphone chargers. The devices may be suitable for motor drives for electric vehicles but face a strong completion from the previously discussed SiC power MOSFET in this application space.

Despite 40 years of progress, innovations in power semiconductor devices continue to enhance their performance. They have become essential technology for providing consumers with enhanced comfort, mobility, and quality of life. The transition from fossil fuels to renewable energy for our electricity needs and electric vehicles for our transportation can only be accomplished by utilizing power semiconductor devices.

### Acronyms

**APEC:** Applied power Electronics Conference

**EDL:** Electron Device Letters

**IEDM:** International Electron Devic-

es Meeting

IPES: International Conference on Integrated Power Electronic Systems **ISPSD:** International Symposium on Power Semiconductor Devices and ICs

**JAP:** Journal of Applied Physics

PCIM: Power Conversion and Intelligent Motion Conference

TED: Transactions on Electron Devices

**TPE:**Transactions on Power Electronics

WiPDA: Wide bandgap semiconductor Power Device and Applications Workshop

### **Biography**

Prof. Baliga is an internationally recognized expert on power semiconductor devices. He is a Member of the National Academy of Engineer-

ing and a Life Fellow of the IEEE. He spent 15 years at the General Electric Research and Development Center, Schenectady, NY, leading their power device effort and was bestowed the highest scientific rank of Coolidge Fellow. He joined NC State in 1988 as a Full Professor and was promoted to the rank of 'Distinguished University Professor' in 1997. Among his many NCSU honors, he was the recepient of the 1998 O. Max Gardner Award given by the North Carolina University Board of Governors to the one person within the 16 constituent universities who has made 'the greatest contribution to the welfare of the human race'; and the 2011 Alexander Quarles Holladay Medal of Excellence, the highest honor at NCSU from the Board of Trustees. Prof. Baliga has authored/edited 22 books and over 700 scientific articles. He has

been granted 122 U.S. Patents. The IEEE has recognized him numerous times-most recently with the highest award, the IEEE Medal of Honor. Scientific American magazine included him among the 'Eight Heroes of the Semiconductor Revolution' when commemorating the 50th anniversary of the invention of the transistor. Prof. Baliga invented, developed and commercialized the Insulated Gate Bipolar Trannsistor (IGBT) at GE. He was inducted into the National Inventors Hall of Fame as the sole inventor of the IGBT. The IGBT is extensively used in the consumer, industrial, lighting, transportation, medical, renewable energy, and other sectors of the economy. It has enabled enormous reduction of gasoline and electrical energy use, resulting in huge cost savings to consumers, and reduction of world-wide carbon dioxide emissions. A detailed description on the applications and social impact of the IGBT is available in one of his books. He received the National Medal of Technology and Innovation, the highest form of recognition given to an engineer by the United States Government, from President Obama in October 2011, at the White House; and the North Carolina Award for Science from Governor Purdue in October 2012, and the Global Energy Prize in 2015.

### Transistors at 75—Past, Present, and Future

CHENMING HU TSMC DISTINGUISHED PROF. EMERITUS. UNIV. OF CALIFORNIA BERKELEY IEEE LIFE FELLOW, MEDAL OF HONOR RECIPIENT

Early Transistors: Three Bell Labs researchers born on three continents invented the transistor 75 years ago-John Bardeen in America (Madison USA), William Shockley in Europe (Liverpool England), and Walter Brattain in Asia (Xiamen China). Another engineer, John Pierce, suggested the name "transistor" because it connects the new device to the already familiar terms: transconductance, resistor, etc.

Transistor became a household word when SONY introduced a shirt-pocket-size transistor radio using Texas Instruments transistors and a standard 9V battery in 1957 and went on to sell 6 million units of that model. IBM introduced the first mass-produced transistor computer in 1958.

From Ge to Si to Heterogeneous Integration: The early transistors were made with germanium. Around 1960, silicon became the preferred semiconductor because its larger bandgap greatly reduces the transistor leakage current especially when the transistors are hot.

While Si wafers are now entrenched as the substrate material, Ge has returned in the form of SixGe1-x alloy thin films added on the Si substrates during IC production. SiGe is playing increasingly critical roles in advanced MOSFETs for enhancing electron and hole mobilities and other benefits. Optical, magnetic, and ferroelectric materials have also been integrated into Si technology. Wide band-gap semiconductors GaN on Si or SiC substrates are used for making high-voltage transistors.

How the Transistor Density Grew and Grew: Jack Kilby of TI received the 2000 Nobel Prize in Physics "for his part in the invention of the integrated circuits". Robert Noyce of Fairchild Semiconductor is considered the other major contributor and his

President Barack Obama shakes hands with Dr. Chenming Hu

patent content bears a great resemblance to modern IC technology, but he had died before 2000.

Today, we take for granted that over 100 million silicon wafers are used each year to produce about 10<sup>20</sup> transistors with the smallest features the size of tens of atoms. But the growth of circuit density could have halted for any one of several reasons long ago but for the ingenuity and hard work of many people and several industries. The semiconductor equipment industry kept improving lithography and other production tools. The process engineers in the leading IC fabs delivered high-yield nano-fabrication technologies for making tiny intricate structures. The

high costs of technology development and fabs were once considered potential showstoppers - until industry consolidation and the foundry model created huge IC manufacturing companies. The EDA industry's design automation tools reduced the barrier to designing large complex ICs, and accurate standard transistor models bridged the physical fabs and the digital EDA tools. Ensuring the long-term reliability of billions of transistors turned out possible through better materials, manufacturing, understanding of failure mechanisms, and failure rate modeling. But past success does not guarantee future success. The hill gets steeper.

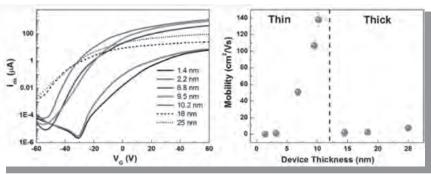

Power Consumption, MOSFET, CMOS, Thin-Body CMOS, 3D Transistor: If we want to cramp a hundred times more transistors into a chip of a certain size, we need to reduce the power consumption per transistor by about a hundred times. Otherwise, heat removal would be a nightmare, not to mention the impact of such energy use on mother earth. A major change that reduced power consumption was the transition from bipolar transistors to MOSFET and then CMOS. CMOS technology reduced the standby current of circuits to nothing but the transistor leakage current.

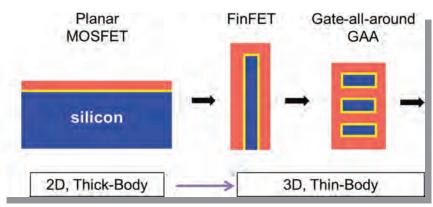

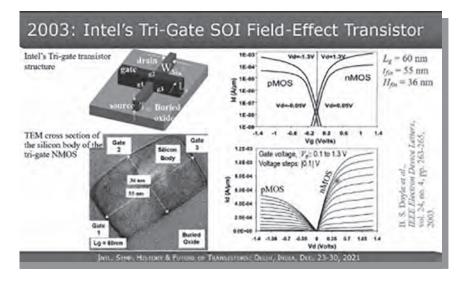

Evolution of transistor structure

The basic MOSFET structure remained unchanged from 1960 for 50 years until reducing MOSFET size further without degrading leakage, speed or switching energy became impossible. In 2011 Intel adopted the first 3D transistor, FinFET for production. FinFET and the thinbody MOSFET concept arise from the insight that the leakage current basically cannot flow within several nanometers (nm) of the Si surface because the surface potential is well controlled by the gate voltage. In the figure showing the MOSFET evolution, FinFET has a vertical Si fin (in blue), about 10nm thin, as the transistor body. The body is covered by gate oxide (in yellow) and gate metal (in orange) and leaves no Si outside the range of strong gate control. It reduces the leakage current by orders of magnitude. Furthermore, the FinFET size can be reduced every few years as long as the fin thickness is also reduced. Another thinbody MOSFET demonstrated in the same DARPA research project as Fin-FET is the ultra-thin-body SOI (UTB-SOI or FDSOI). Being a 3D transistor, FinFET has a smaller footprint than the planar MOSFET. It has the same advantage as building tall buildings

instead of single-story buildings in a crowded city.

The fin of FinFET has become thinner and taller with each new technology node. At the 2nm node, it is too hard to make the required thin and tall fin by lithography and etching. The industry is adopting a new 3D thin-body MOSFET structure called NanoSheet or GAA (gate-all-around), where the thin body is made by epitaxial growth and etch-release. The figure above illustrates the evolution from FinFET to GAAFET.

## Examples of What May Happen Next

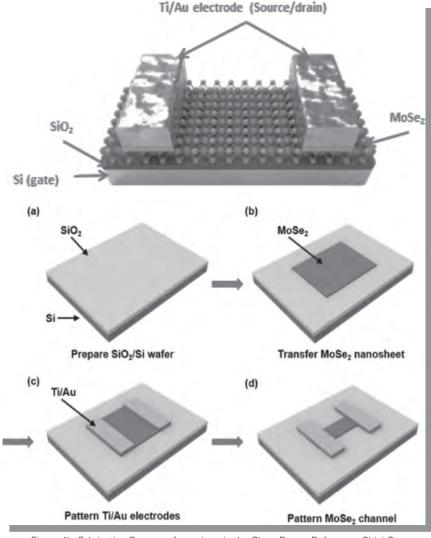

3D transistors and 3D packaging are here to stay. 3D NAND technology is an excellent example of a costeffective monolithic 3D memory IC. Monolithic 3D logic IC may start with stacking PFET on top of NFET to reduce CMOS-gates' footprints. Future monolithic 3D IC paths may employ transferred single-crystal semiconductor films, self-assembled 2D semiconductors, or amorphous or polycrystalline semiconductor films as the transistor material. 0.6nm MoS2 monolayer has been used to demonstrate 1 nm gate-length thinbody MOSFET. Power supply voltage

and power consumption may be reduced by many folds with Negative-Capacitance Transistor (NCFET). It requires inserting a thin layer of ferroelectric such as HfZrO in the MOSFET gate stack. Another advantage of adding the thin ferroelectric is its memory property that may be exploited for computing in memory or fast non-volatile memory.

## Does the World Need More and Better Transistors?

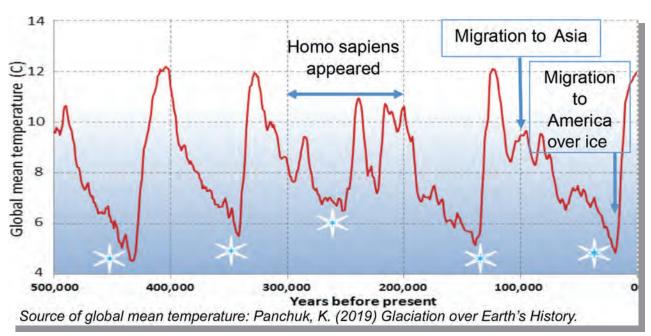

The enormity of the task of dealing with global warming (see the graph below) is beginning to be realized. What about the task of dealing with the next Ice Age, which is predicted to start in 1500 years based on Earth's orbit? Humans may need order-of-magnitude greater capabilities to deal with future existential challenges.

But how can we possibly get 10x or more problem-solving power? Electronics are the key. While all technological advances bring forth new capabilities, electronics are unique for three reasons.

Its impact is infectious. Highspeed communication and computing, automation, internet, Al, robotics, and

Variation of global mean temperature

- yet-unknown future technologies enabled by better transistors have lifted and will lift up all technologies, industries, and sciences. And they in turn lift each other.

- 2) ICs use relatively small amounts of materials. And the less materials they use (by being made smaller), the faster and more capable they become.

- 3) Theoretically, the energy required for information manipulation can still be reduced by more than a thousand times. Although we have no idea how to get there now, reducing the energy by 10 or 100 times would not violate physical laws. The energy efficiencies of other technologies (transportation, lighting, ...) are mostly already around 50% of their theoretical limits.

### Lesson From the Past and Task for the Future

The history of transistors is a journey log of climbing one hill after another. Until we get high enough on one hill, we can not even see the terrain and map a route to reach the next hill. Importantly, with each hill climbed, we accumulate and discover new skills that help us move forward. Deposit and etch materials one atomic layer at a time? Sure. Economically on millions of wafers every week at high yield with billions of transistors on each chip? Sure. Magnetic, ferroelectric, and optical materials too? Sure. Switch the magnetic polarization with an electric field, not current? Sure. Do anything that does not violate physical

laws? Probably. Continuing the hard climbs while diligently scouting for new provisions and possible routes is the best way to create future electronics, which may be very different in devices, materials, and operating mechanisms. The new provisions and route will come from university and industry researchers with deep knowledge in physics, chemistry, biology, and algorithms—and the help of expanding problem-solving capabilities, time, and luck.

### **Biography**

Dr. Hu received his B.S. degree from National Taiwan University, which honored him with its Distinguished Alumni Award,

and M.S. and Ph.D. degrees from UC Berkeley. Dr. Chenming Hu is called the Father of 3D Transistors for developing the FinFET in 1999. Intel hailed FinFET as the most radical shift in semiconductor technology in over 50 years. Modern computers, smart phones, and the internet all ran on 3D transistor processors. He received the US National Technology and Innovation Medal from President Obama in 2016. He leads the ongoing development of BSIM, a suite of industry-standard computer models of transistors. University of California provides it royalty free for the global IC industry to design integrated circuits worth well over a trillion US dollars since 1995. IEEE, world's largest technical professional organization, gave him its highest award,

Medal of Honor, in 2020 for helping to "keep Moore's Law going over many decades" after lauding him as "Microelectronics Visionary" for "achievements critical to producing smaller yet more reliable and higher-performance integrated circuits" in 2009. The 2013 Kaufman Award cited his "tremendous career of creativity and innovation that fueled the past four decades of the semiconductor industry". Dr. Hu is TSMC Distinguished Chair Professor Emeritus of the University of California, Berkeley. From 2001 to 2004 he was the Chief Technology Officer of TSMC, now the world's largest semiconductor company. He was the board chairman of the nonprofit Friends of Children with Special Needs and the East Bay Chinese School. He has authored six books and 1000 research papers and received over 100 US patents and honorary doctoral degrees from the University of Hong Kong and NYCU in Taiwan. He is honored with memberships in the US National Academy of Engineering, Chinese Academy of Sciences, US Academy of Inventors, The World Academy of Sciences and Academia Sinica. His other professional honors include Asian American Engineer of the Year; Silicon Valley Engineering Hall of Fame; IEEE Jack Morton Award, Solid State Circuits Award, Nishizawa Medal, and the EDS Education Award for "distinguished contributions to education and inspiration of students, practicing engineers and future educators." He also received UC Berkeley's highest honor for teaching—the Berkeley Distinguished Teaching Award.

### TECHNICAL BRIEFS

### OUTSIDE SYSTEM CONNECTIVITY ROADMAP

C. MICHAEL GARNER

GARNER NANOTECHNOLOGY SOLUTIONS, CHAIR OUTSIDE SYSTEMS CONNECTIVITY

### 1. Introduction

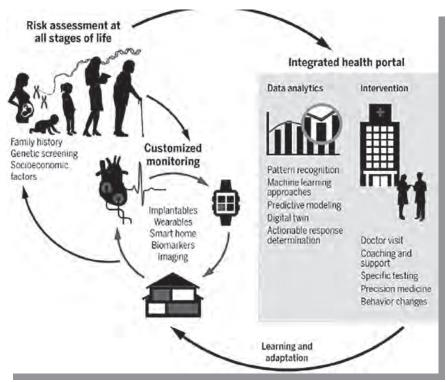

The purpose of the Outside System Connectivity (OSC) roadmap is to identify communication requirements for systems in different applications, identify gaps in capabilities, identify critical component and device development needs and monitor developments of capabilities to fill these future gaps.

The Internet of Everything (IoE) is continuing to expand in applications that demand higher volumes of higher performance communication. The IoE was initially defined as a wide range of Internet of Things (IoT) devices communicating with cloud computing that store data and which was analyzed with applications and actions communicated. As IoE was used for a broader range of applications, some applications had unacceptably slow performance due to the latency of communicating with the cloud. To overcome this latency limitation, some applications added local storage and processing close to the IoT devices and network, which is referred to as fog computing.

Most applications will employ RF/ microwave wireless communication to connect to the internet which will then connect through high-performance backhaul or fiber optical interconnects to a cloud data center. In the future, millimeter waves (mmWaves), massive multiple-input multiple-output (MIMO) or other 5G media will be implemented for high-speed connection to terminal devices, while lowpower wide-area network (LoWAN) communications, such as LoRaWAN, SIGFOX, LTE Cat 0 and NB-loT, will be utilized to connect and provide enormous data to the cloud and/or fog

computing system from IoT-edge sensor devices. Within the data center, communication to servers is through fiber optical interconnects with signals being routed through multiple routers. Upon arrival at a router, the optical signals are converted to electrical, routed and then converted back to optical signals, which adds to energy consumption and latency. The requested data is then routed out of the data center and returned to the requesting IoT devices through a path similar to the request path.

Applications that require fast communication and decision making, such as autonomous vehicles and traffic control, are adopting edge computing. In this model fast communications are made between the edge and vehicles and traffic flow controls and filtered data is communicated between edge computing and the supporting cloud computing capabilities. Fast communication with low latency is required between the IoT devices and the fog, while fast communication will be required also between elements of the Edge. Computing in the Edge can be performed in a micro data center, which is connected to the network and the internet.

With the rapid growth of high data rate internet applications and IoT, communication rates in data centers need to grow to support high-speed access and provide high-speed low latency communication between servers and memory or other servers. With increased use of high-resolution video, virtual reality, and augmented reality applications, ever higher data rate communication with lower latency is required in data cen-

ters. Communication between racks and switches is carried by optical interconnects; however, the capacity of switches is increasing faster than the capacity of fiber interconnects. Also, the power consumed by the switches in data centers is approximately 30% of the power consumed in the data center. To reduce switching power and overcome the fiber capacity gap, companies are working to integrate silicon photonics into the switch. There are also efforts to extend fiber into the server, into packages and thus reduce power. There are significant technical challenges with developing and implementing single mode fiber with low loss for these applications. These challenges will be highlighted in this article.

Applications that will first drive the development of high-volume component and device development are communication in data centers and mobile handheld devices. Over time new applications, such as quantum computing, may arise that require the development of new component and device capabilities and these are monitored in the roadmap.

## 2. Application/System Requirements & Challenges

While a broad range of applications are assessed in the OSC roadmap, data centers and mobile smartphones are driving development of higher performance circuits and devices and are described in this article.

### Data Center Communication

For data centers, the drivers for communication are the data rate per server unit, which is currently 400 Gbps, as shown in Table 1, and

Table 1: Wavelength Division Multiplexing Module Performance Requirements

|                                         | 2019 | 2021 | 2023    | 2025 | 2027    | 2029    | 2031 | 2033 | 2035 | 2037    |

|-----------------------------------------|------|------|---------|------|---------|---------|------|------|------|---------|

| System structure                        |      |      |         |      |         |         |      |      |      |         |

| Data Rate/ Lane[1] (Gbit/s)             | 100  | 100  | 100/200 | 200  | 200/400 | 200/400 | 400  | 400  | 400  | 400/800 |

| Data Rate/fiber (Gbit/s)                | 400  | 400  | 800     | 800  | 1600    | 1600    | 3200 | 3200 | 3200 | 3200    |

| Distance (km)                           | < 10 | < 80 | < 80    | < 80 | < 80    | < 80    | < 80 | < 80 | < 80 | < 80    |

| #Wavelengths [2]                        | 4    | 4    | 4       | 4    | 8       | 8       | 8    | 8    | 8    | 8       |

| Number of Bits per symbol (HOM) [3]     | 2    | 2    | 2       | 2    | 2       | 2       | 4    | 4    | 4    | 4       |

| Additional link penalty due to HOM (dB) | 3    | 3    | 3       | 3    | 3       | 3       | 9    | 9    | 9    | 9       |

- [1] a lane is for a single data stream with only amplitude modulation in a fiber (per wavelength)

- [2] assuming HOM on fully integrated Si Photonics: QPSK/DPQPSK demonstrated with Si-photonics, 16-PSK, 32-PSK not demonstrated

- [3] assuming integrated laser on Si after 2019, 40 mW on WDM laser at high temperature not demonstrated yet

HOM: Higher Order Modulation (i.e. PAM4, QPSK, etc.)

PAM: Phase Amplitude Modulation QPSK: Quadrature Phase-Shift Keying WDM: Wavelength-Division Multiplexing

| Manufacturable solutions exist, and are being optimized |  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|--|

| Manufacturable solutions are known                      |  |  |  |  |  |

| Manufacturable solutions are NOT known                  |  |  |  |  |  |

power consumption. Data centers typically upgrade servers approximately every three years and would like to have the data rates increase when they upgrade the servers; however, this would require upgrading the optical interconnect cables with every server upgrade. Power consumed in communication and switching is becoming significant, 30% of data center power in 2013, and signal integrity is being compromised at higher date rate due to RF loss in the metal trace between the switch chip to the faceplate, so Data Centers are requesting that optical I/O be integrated into the switch package by the 51.2 Tbps switch. The Consortium for On-Board Optics (COBO) or Co-packaged Optics (CPO) is driving to have the photonic transmitter and receiver on the board and connecting this to single-mode fiber in the data center. This would enable upgrading the data center communication data rate when the servers are upgraded. At the same time, the routers in data centers are adding

communication capacity and ports that consume considerable power, so the industry is seeking ways to reduce router thermal density and improve energy efficiency.

### Mobile Handheld

As smart phones incorporate more functionality, they will need to communicate at higher data rates, as shown in table 2, with the internet, but also detect signals from GPS satellites, cell towers, health monitors, watches, and other RF sources. Thus, they will need to have compact antennas that can receive and transmit to multiple ranges of frequencies with multiple protocols. The RF and AMS (Analog/Mixed-Signal) components will need to support all of the communication with high energy efficiency for multiple applications simultaneously.

A significant challenge for mobile smartphones is to support the data rates required for new multimedia applications such as virtual reality. While future smartphones need to

communicate at higher data rates, they will need to operate with low power consumption. Furthermore, future smartphones will need to have improved security of personal information when communicating with the internet or other devices. An additional challenge is to integrate additional antennas into thin smartphones without causing interference in other communications or integrated circuits.

### 3. Critical Components

### Data Centers

To achieve higher data rates, more wavelengths than 4 in current CWDM4 format and higher order modulation, will be needed in addition to higher data rates per lane. To support pulse amplitude modulation, DAC/ADCs are needed.

### Mobile Phones

In the longer term, high frequency mmWave may be used in high population density areas to support high

Table 2: Mobile Device Wireless Cellular Performance Requirements

| Year                                                  | 2021        | 2022     | 2023        | 2024        | 2025        | 2026        | 2027     | 2028     | 2029        |

|-------------------------------------------------------|-------------|----------|-------------|-------------|-------------|-------------|----------|----------|-------------|

| Cellular Data Rate Gbps (Max.) <sup>6</sup>           | 5           | 5        | 7           | 7           | 7           | 10          | 10       | 10       | 20          |

| Max. Cell Range <sup>7</sup> (km)<br>[unobstructed]   | 35/0.2-1    | 35/0.2-1 | 35/0.2-1    | 35/0.2-1    | 35/0.2-1    | 35/0.2-1    | 35/0.2-1 | 35/0.2-1 | 35/0.2-1    |

| 3G Frequency                                          | <4 GHz      | <4 GHz   | <4 GHz      | <4 GHz      | <4 GHz      | <4 GHz      | <4 GHz   | <4 GHz   | <4 GHz      |

| 4G Frequency                                          | <4 GHz      | <4 GHz   | <4 GHz      | <4 GHz      | <4 GHz      | <4 GHz      | <4 GHz   | <4 GHz   | <4 GHz      |

| 5G Maximum Data Rate (Gbps)                           | 5           | 5        | 7           | 7           | 7           | 10          | 10       | 10       | 20          |

| 6G Maximum Data Rate (Gbps)                           |             |          |             |             |             |             |          |          |             |

| Wireless Power Budget (mW)                            | 200–<br>300 | 200–300  | 200–<br>300 | 200–<br>300 | 200–<br>300 | 200–<br>300 | 200–300  | 200–300  | 200–<br>300 |

| Year                                                  | 2030        | 2031     | 2032        | 2033        | 2034        | 2035        | 2036     | 2037     |             |

| Cellular Data Rate Gbps (Max.) <sup>6</sup>           | 20          | 20       | 50          | 50          | 50          | 70          | 70       | 70       |             |

| Max. Cell Range <sup>7</sup> (km) [unob-<br>structed] | 35/0.2-1    | 35/0.2-1 | 35/0.2-1    | 35/0.2-1    | 35/0.2-1    |             |          |          |             |

| 3G Frequency                                          | <4 GHz      | <4 GHz   | <4 GHz      | <4 GHz      | <4 GHz      |             |          |          |             |

| 4G Frequency                                          | <4 GHz      | <4 GHz   | <4 GHz      | <4 GHz      | <4 GHz      |             |          |          |             |

| 5G Maximum Data Rate (Gbps)                           | 20          | 20       | 20          | 20          | 20          | 20          | 20       | 20       |             |

| 6G Maximum Data Rate (Gbps)                           |             |          | 50          | 50          | 50          | 70          | 70       | 70       |             |

| Wireless Power Budget (mW)                            | 200–<br>300 | 200–300  | 200–<br>300 | 200–<br>300 | 200–<br>300 | 200–<br>300 | 200–300  | 200–300  |             |

<sup>&</sup>lt;sup>6</sup> Assumes that Massive MIMO will be implemented in 2019 and full 5G performance in 2025.

<sup>&</sup>lt;sup>7</sup> Assumes 4G LTE through 2017, Massive MIMO <6 GHz through 2023 and both Massive MIMO <6 GHz and mm Wave beyond 2025.

| Manufacturable solutions exist, and are being optimized |  |  |  |  |  |

|---------------------------------------------------------|--|--|--|--|--|

| Manufacturable solutions are known                      |  |  |  |  |  |

| Manufacturable solutions are NOT known                  |  |  |  |  |  |

data rate applications with a large number of users. A significant challenge is that 28 GHz to 78 GHz signals do not penetrate buildings, so buildings would need to have repeaters in the building or employ massive MIMO or ultra-high data rate Wi-Fi.

If 5G is implemented with mmWave and MIMO, cell phones would need to have multiple antennas to receive and transmit information and each antenna would need to have power amplifier (PA) and an ADC and DAC [1], which would consume considerable power operating with high precision at high frequencies. A critical challenge is to increase the energy efficiency of the PA at mmWave frequencies while maintaining linearity, since the efficiency of the PA decreases with operating frequency. Thus, higher performance

of incumbent process technologies or even new materials may be required to improve energy efficiency. In the transmit mode, the antenna array would operate as an active phased array to focus transmission toward the base station. To overcome the high operating power of the high precision DAC/ADCs, use of hybrid analog/digital preprocessing [2, 3] or lower precision DAC/ADCs (1bit) [1, 2, 4] has been proposed. To compensate for potential blockages [5], multiple antennas would need to be integrated into the cell phone to be connected with multiple base stations.[6]

For >10 Gb/s communication rates, proposals have been made for a single bit zero crossing modulation protocol; however, energy efficiency of all required components need to be investigated.

### 4. Integrated Circuits

To increase data rates of communication with lower power and lower power, DACs and ADCs need to operate with higher sampling rates and lower power consumption. Also, serializer-deserializer (SERDES) circuits need to operate at higher frequencies with higher efficiency. To achieve higher data rates with improved energy efficiency in these circuits, devices need to operate with lower power at higher frequencies. This may require introduction of new device, gate, contact, or interconnect materials while decreasing circuit cost.

Recently, a 5 nm integrated circuit technology was announced that demonstrated a transmitter test circuit that operated at 130 Gb/s data rates with PAM4 modulation and 0.97 pJ/bit energy consumption [7].

### 5. Device Requirements, Chal**lenges & Potential Solutions**

#### **CMOS Devices**

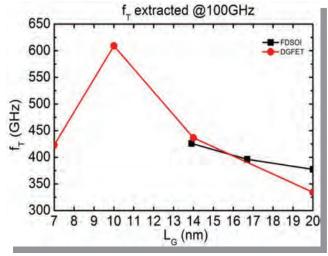

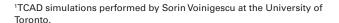

The 2022 roadmap technology plots reflect the RF and analog performance metrics needed to support the technology roadmap developed by the IRDS More Moore IFT in 2017. The RF-AMS performance metrics for CMOS devices have been restricted to peak f<sub>T</sub> (Figure 1) and peak g<sub>m</sub> (Figure 2) and have been calibrated on recent averaged measured data in the 28 nm, 22 nm, and 16 nm nodes. The 2020 roadmap gives the above performance FoMs for n-channel FDSOI and double-gate FinFET highperformance devices obtained from technology computer aided design (TCAD)-based device modeling methods(a) [8]. These include hydrodynamic transport with thin silicon mobility physics, as well as the estimated resistive and capacitive device parasitics up to the first metal layer, which defines the terminals of a transistor cell in high-frequency analog circuit design. They indicate the degradation in f<sub>T</sub> and g<sub>m</sub> at gate lengths below 10 nm as a result of mobility degradation caused by surface scattering at the gate oxide interface, and due to the ever-thinner silicon body. As can be observed, the double gate of the FinFET results in higher transconductance but also higher capacitive parasitics compared to the single-gate FDSOI MOSFETs. Note that the displayed  $f_T$  (Figure 1) does not include the capacitive parasitics resulting from connecting the transistor cell to the passive devices in the upper metal layers of the back-end. The introduction of new materials, and transistor and gate structures may change the  $f_T$  trend of sub 10 nm CMOS devices. Reduction of gate and contact resistance has been demonstrated to improve  $f_{Max}$  [9, 10], but not impact  $f_T$ .

Many of the materials-oriented and structural changes being invoked in the digital roadmap degrade or alter RF and analog device behavior. Complex tradeoffs in optimization for RF, HF, and AMS performance occur as different mechanisms emerge as limiting factors. Examples include series resistances at gate, source and drain, as well as parasitics from interconnecting the transistors to other devices in a circuit that greatly affect the device impedances and the "loaded" figures of merit as measured at the upper metal levels. Fundamental

changes of device structures, e.g., multiple-gates and silicon-on-insulator (SOI), to sustain continued digital performance and density improvements greatly alter RF and AMS characteristics. Such differences, along with the steady reduction in supply voltages, pose significant circuit design challenges and may drive the need to make dramatic changes to existing design structures.

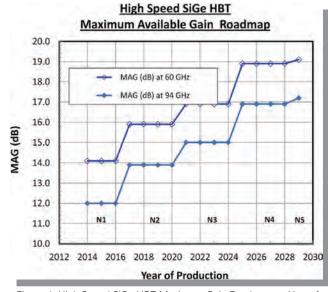

### Group IV Bipolar

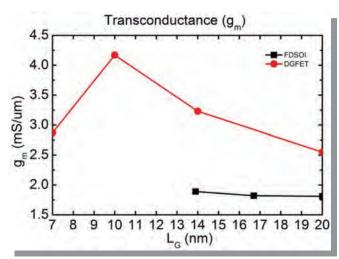

The roadmap for SiGe heterojunction bipolar transistors (HBTs) and associated benchmark circuits at mm-wave frequencies has been based since 2013 on a seamless set of TCAD device simulation tools in order to obtain consistent compact model parameters for the complete transistor structure used in the respective circuit simulations. All known transport, structural parasitics up to metal 1 (i.e. transistor cell terminals) and temperature effects have been included in the results [11] and calibrated based on experimental data. Furthermore, the TCAD tools and those parameters that cannot be obtained by TCAD have been calibrated on existing prototyping process technologies. Performance

Figure 1. CMOS Roadmap for Peak fT vs. Physical Gate Length for FD-SOI and Double-gate (FinFET) MOSFETs Based on Technology CAD.1

Figure 2. CMOS Roadmap for Transconductance per Unit Gate Width, q<sub>m</sub>, vs. Physical Gate Length for FDSOI and Double-gate (FinFET) MOSFETs Based on Technology CAD.

plateaus have been assumed to last four years and are linked to applications and the foregoing system drivers. It has been assumed that at least two foundries offering the technology of the respective node for product prototyping are presented. The benchmark circuits for LNA, PA, VCO, and current-mode-logicbased (CML) ring-oscillator (RO) have been manually optimized for each technology node and a variety of commercially relevant frequencies. The most recent result for a prototyping process [12] corresponds closely to the performance predicted for node N3 (Figures 3, 4).

Even though it is a challenge for the HS-NPN to increase the unity current gain cut-off frequency  $f_T$  by more aggressive vertical profiles, it is less of a challenge to achieve  $f_{MAX}$  $> f_T$ . What is unclear today is, how large the ratio  $f_{MAX}/f_T$  needs to be for future circuit applications. That is, the challenge is to determine what this ratio should be by using the "plateau technologies" for the next roadmap and appropriate benchmark circuits. Since lateral scaling requirements for HBTs are significantly relaxed compared with those for MOSFETs, vertical profile fabrication under the

constraints of overall process integration appears to be the bigger challenge. The reduction of imperfections and the increase of current carrying capability of the emitter and collector contact metallization are further challenges that need to be met by process engineers on the way to achieving the physical limits of this and any other technology [12].

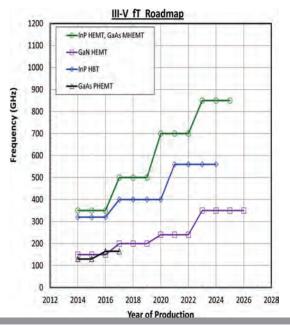

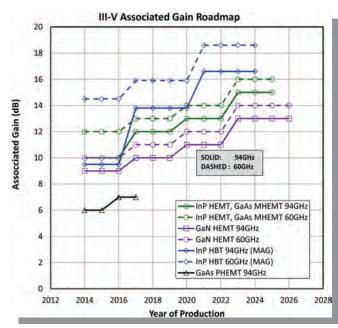

### III-V FET and Bipolar

The FoMs depend on technology and include:  $f_T$ ,  $f_{MAX}$ ,  $g_m$ , and  $V_{BD}$ ; power, gain, and efficiency at 10, 24, 60, 94, 140, and 220 GHz; NF<sub>MIN</sub> and G<sub>A</sub> at 10, 24, 60, and 94 GHz; LNA NF and  $G_A$  at 140 and 220 GHz. Ft and associated gain are as shown in Figures 5-6. As mentioned previously, RF and AMS front-end components are a growing part of the semiconductor industry. However, this has divided the III-V technology landscape into two groups, one dominated by the large volume consumer market and the other dominated by low volume specialty markets. Within the III-V technology landscape, the large volume consumer driven market is best represented by GaAs HBT power amplifiers for cellular communications.

The unique challenges for III-V devices are yield (manufacturability), substrate size, thermal management, integration density, dielectric loading, and reliability under high fields. Challenges common with Si-based circuits include improving efficiency and linearity/dynamic range, particularly for power amplifiers. A major challenge is increasing the functionality of power amplifiers in terms of operating frequency and modulation schemes while simultaneously meeting increasingly stringent linearity and efficiency requirements at the same or lower cost.

## Photonic Integrated Circuits and Devices

Near-term challenges are to 1) increase the data rate per wavelength and total throughput per fiber, density of optical transceivers while reducing their power and cost, and 2) develop a router/switch package integrated photonic interconnects for data centers. Long-term challenges include 1) processing information in the optical domain, and 2) developing methods for communication between systems with different wavelengths, polarizations, and modulations.

Figure 3. High Speed SiGe HBT fT and fMAX Roadmap vs. Year of Production.

Figure 4. High Speed SiGe HBT Maximum Gain Roadmap vs. Year of Production.

### Photonic Integrated Circuits(PIC)

Recently, photonic integrated circuits on silicon, using either hybrid or heterogeneous integration methods, have been introduced into the market by multiple transceiver manufacturers. Currently, some of these products have separate transmitter and receiver chips.

Some of these transmitter circuits have the lasers integrated with the modulators, while some of these have the laser packaged separately from the modulators. In most cases, the modulators and waveguides are fabricated on single-crystal silicon on insulator wafers. Most suppliers are employing Mach Zehnder modulators, while more compact ring modulators are being evaluated in research and moving to product phase in a few years. Since ring modulator operating wavelength is sensitive to temperature, they have been integrated with tuning elements to control the optimal wavelength, which increases power consumption and cross-talk, which must be managed. Many of these transmitter circuits employ multiple wavelengths that either are transmitted over individual fibers or multiplexed into a single fiber. Mach Zehnder modulators and the (de)multiplexers currently use silicon waveguides and the weak electro-optic effect from free carriers means the foot-print of the PIC is relatively large. Future energy-savings from these circuits, will depend upon improvements to laser wall-plug efficiency and reduction in size and power consumption of electro-optic modulators, thereby having a cascading effect of reduced power consumption and cost for the photonic chip, and supporting integrated circuits.

### Low Power High Output Lasers

To reduce the power consumed in communication, there is a need to increase the efficiency of lasers in converting electrical energy to photons. VCSELs and edge-emitting lasers are used for different applications and may be competing in some applications as silicon photonics strives to reduce cost while increasing data rates.

Although VCSELs are more energy efficient than edge emitting lasers, the power to modulate at higher data rates will increase, which can cause reliability issues. So more efficient top emitting lasers are needed in the future. To support high volume manufacturing,

III-V quantum dot VCSELs epitaxially grown and fabricated on (001) silicon [13] with p-doping [14] have been demonstrated with high stability over a wide temperature range.

An emerging technique to increase photonic light source energy dissipation is to introduce nanostructures that increase energy density. This has been used to demonstrate electrically pumped lasers with lasing thresholds of 287 nA at 150 K [15] that is 1000x less than earlier electrically pumped nanocavity lasers.

Some short-distance communication links may also be powered by high-efficiency LEDs (no threshold). However, higher throughput relies on efficient packaging of several thousand spatially multiplexed optical channels.

### High-Density Low Power Modulators

For optical interconnects to meet future requirements, all supporting devices must operate with higher performance, lower energy consumption, higher optical efficiency, and have a lower cost. Essential for long-distance communication, Electro-Optic Modulators (EOM) can modulate the amplitude, phase, frequency, or polarization

Figure 5. III-V Roadmap for fT

Figure 6. III-V Roadmap for Associated Gain

of the light; however, these devices must become more compact, and operate with lower power consumption. Compact modulator options in the future will likely use the following physical effects: electro-absorption modulation, bulk semiconductor Franz-Keldysh effect (III-V, Ge), plasmonics, Stark Effect, or Wannier-Stark localization.

## High Speed, High-Density Photodetectors

A significant challenge for optical detectors is to increase operating frequency to support higher data rates. A limiting factor is the RC time constant of the photodetector. The most logical solution is to reduce the detector size which reduces junction capacitance, but this may not be able to absorb most of the light, i.e., poor responsivity. Ongoing efforts are focused on reducing the junction and contact resistance for the smaller photodetectors, and achieve a good speed-responsivity tradeoff. The most recent research breakthrough has yielded a bandwidth in excess of 250 GHz [16]. If the detector intercepts less light from the waveguide, the amplifier will need to have higher gain that will potentially reduce the signal-tonoise ratio. The best solution to this is to develop techniques to effectively couple light from the waveguide into the detector. Possible solutions include using plasmonic structures above the photodetectors to focus light into the detector. Another option is to include passive periodic or aperiodic nanophotonic structures to focus light onto the photodetector. The temperature dependence of the potential solutions needs to be understood, to design the optimal solution.

# Optically Based Switching and Routing

Currently, optical signals are redirected by electrical routers where the light must be converted to electrical signals that are routed to different fi-

ber channels. This significant latency can be added to the transmission of optical signals that go through multiple routers. New technologies are needed to enable optically based switching and routing that do not require the optical-electrical-optical conversion. Hybrid electrical/optical (E/O) routing capabilities have been demonstrated using both MEMS [17–20] and E/O switches including Mach-Zehnder interferometers [21] and ring resonators [22].

If all-optical networks are to be viable, optically based logic will be needed to identify signal stream routing conflicts and determine the correct routing alternative. A number of optical logic devices and functions have been proposed that require local nonlinearity of optical properties [23]. It is proposed that branched waveguides with local nonlinear optical materials could function as AND on OR functions [24].

### 6. Summary

Future system communication requirements are driving development of new communication architectures, circuits, and devices. The OSC welcomes input on circuit and device requirements and potential solutions.

### 7. Acknowledgments

The author acknowledges the valuable contributions of the IEEE IRDS members and former ITRS members to the IEEE IRDS Outside System Connectivity Roadmap. Furthermore, valuable improvements were made to this paper by Carlos Augusto, Di Liang, and Sudharsanan Srinivasan.

#### References

[1] W.-b. Abbas, F. Gomez-Cuba, and M. Zorzi. "Millimeter wave receiver efficiency: A comprehensive comparison of beamforming schemes with low resolution ADCs." arXiv preprint arXiv:1607.03725 (2016). https://arxiv.org/abs/160703725

[2] A. Alkhateeb, et al. "MIMO precoding and combining solutions for millime-

ter-wave systems." *IEEE Communications Magazine* 52.12 (2014): 122–131.

[3] C. Risi, D. Persson, and E. G. Larsson. "Massive MIMO with 1-bit ADC." arXiv preprint arXiv:1404.7736 (2014). https://arxiv.org/abs/1404.7736

[4] S. Kutty and D. Sen. "Beamforming for millimeter wave communications: An inclusive survey." *IEEE Communications Surveys & Tutorials* 18.2 (2016): 949–973.

[5] Y. Huo, X. Dong and W. Xu, "5G Cellular User Equipment: From Theory to Practical Hardware Design," in *IEEE Access*, vol. 5, pp. 13992–14010, 2017. DOI: 10.1109/JPROC.2012.2207649

[6] J.G. Andrews, et al. "Modeling and analyzing millimeter wave cellular systems." *IEEE Transactions on Communications* 65.1 (2017): 403–430.

[7] G. Yeap et al., TSMC, "5nm CMOS Production Technology Platform Featuring Full-Fledged EUV and High-Mobility Channel FinFETs with Densest 0.021µm² SRAM Cells for Mobile SoC and High-Performance Computing Applications," IEDM 2019 Paper #36.7

[8] S.P. Voinigescu, S. Shopov, J. Bateman, H. Farooq, J. Hoffman, and K. Vasilakopoulos. "Silicon millimeterwave. Terahertz, and high-speed fiber-optic device and benchmark circuit scaling through the 2030 ITRS horizon." Proceedings of the IEEE 105, pp. 1087-1104, 2017. DOI: 10.1109/JPROC.2017.2672721

[9] K. Hijioka, J. Kawahara, M. Narihiro, I. Kume, A. Tanabe, H. Nagase, H. Yamamoto, N. Inoue, T. Takeuchi, T. Onodera, S. Saito, N. Furutake, and Y. Hayashi." Rf performance upgrading of low-power 40nm-node CMOS devices by extremely low-resistance partially-thickened local (PTL)-interconnects." Proceedings of the 2009 IEEE international electron devices meeting (IEDM) pp 887-889.

[10] C. Auth, et al. "A 10nm High Performance and Low-Power CMOS Technology Featuring 3rd Generation FinFET Transistors, Self-Aligned Quad Patterning, Contact over Active Gate and Cobalt Local Interconnects." Proceedings of the 2017 IEEE International Electron Devices Meeting (IEDM), 29.1.

[11] M. Schröter, T. Rosenbaum, P. Chevalier, B. Heinemann, S. Voinigescu,

E. Preisler, J. Boeck, A. Mukherjee, "SiGe HBT technology: Future trends and TCAD based roadmap", Proc. of the IEEE, Vol. 105, No. 6, pp. 1068-1086, 2017. DOI: 10.1109/JPROC.2015.2500024

[12] B. Heinemann et al., "SiGe HBT with fT/fMAX of 505 GHz/720 GHz", IEDM Tech. Digest, 2016.

[13] N. Ledentsov, L. Chorchos, O. Makarov, J.-R. Kropp, V. A. Shchukin, V. P. Kalosha, J. P. Turkiewicz, N. Cherkashin, and N. N. Ledentsov "Quantum-dot oxideconfined 850-nm VCSELs with extreme temperature stability operating at 25 Gbit/s up to 180°C", Proc. SPIE 11300, Vertical-Cavity Surface-Emitting Lasers XXIV, 113000H (24 February 2020); https://doi. org/10.1117/12.2543244

[14] H. Huang, J. Duan, B. Dong, J. Norman, D. Jung, J. E. Bowers, and F. Grillot. "Epitaxial quantum dot lasers on silicon with high thermal stability and strong resistance to optical feedback." Applied Physics Letters Photonics 5, 016103 (2020); https://doi.org/10.1063/1.5120029

[15] B. Ellis, M. Mayer, G. Shambat, T. Sarmiento, E. Haller, J. S. Harris, and J. Vuckovic. "Ultralow-threshold electrically pumped quantum-dot photonic-crystal nanocavity laser". Nature Photonics 5, pp. 297-300 (2011). DOI: 10.1038/nphoton.2011.51.

[16] Lischke, S., Peczek, A., Morgan, J.S. et al. Ultra-fast germanium photodiode with 3-dB bandwidth of 265 GHz. Nat. Photon. 15, 925-931 (2021).

[17] G. Wang, et al. "Your Data Center is a Router: The case for Reconfigurable Optical Circuit Switched Paths." Proc. ACM Hotnets VIII (New York City, NY, USA) (2009).