OCTOBER 2019 VOL. 26, NO. 4 ISSN: 1074 1879

EDITOR-IN-CHIEF: CARMEN M. LILLEY

#### TABLE OF CONTENTS

| TECHNICAL BRIEFS                             |

|----------------------------------------------|

| UPCOMING TECHNICAL MEETINGS                  |

| SOCIETY NEWS                                 |

| VOUNG PROFESSIONALS                          |

| CHAPTER NEWS                                 |

| REGIONAL NEWS                                |

| EDS MEETINGS CALENDAR                        |

| EDS MISSION. VISION AND FIELD OF INTEREST 52 |

# TECHNICAL BRIEFS

# MARVELS OF MICROELECTRONIC TECHNOLOGY: THE 1T-1C DYNAMIC RANDOM ACCESS MEMORY, FROM A GROUNDBREAKING IDEA TO A BUSINESS BENCHMARK

BY SIMON DELEONIBUS, PAST CHIEF SCIENTIST, CEA, LETT

In this issue, we report on one of the flagship Marvels of Microelectronic Technology, which has marked the history of microelectronics in the past 50 years: the 1 Transistor –1 Capacitor Dynamic Random Access Memory (1T1C DRAM). DRAMs have driven and accompanied Moore's Law through Metal Oxide Semiconductor Field Effect Transistor (MOSFET) integrated circuit scaling. They have been and still are a benchmark for the microelectronics industry: they continue to share their leadership with advanced microprocessors, SOCs and nonvolatile memories. DRAM fostered technological progress that was necessary to introduce new materials and revise process integration. In this article, R.H. Dennard, H. Sunami, M. Koyanagi and K. Itoh (Figure 1) accepted to remind us the pioneering times when 1T1C DRAM came out of its cradle.

#### **DRAM Invention and First Developments**

The groundbreaking ideas proposed by Robert Dennard, IEEE Fellow, IBM Fellow, to push microelectronics progress thanks to the 1T1C DRAM and MOSFET integrated circuit scaling have already been widely commented and many times awarded. The circumstances giving birth to the idea of MOSFET scaling were reported in the IEEE EDS Newsletter July 2019 issue. In this issue (October 2019), we will report the advent of 1T1C DRAM. Robert Dennard kindly accepted to remind us a few important facts. Some of them were also reported at

(continued on page 3)

#### SAVE THE DATE!

EDS Governance Meeting Series 7–8 December 2019 San Francisco, California, USA

#### **ELECTRON DEVICES** SOCIETY

#### President

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

#### **President-Elect**

Meyya Meyyappan NASA Ames Research Center E-mail: m.meyyappan@nasa.gov

#### Treasurer

Subramanian S. Iver **UCLA**

E-mail: iver@ieee.org

#### Secretary

Jacobus Swart FEEC/UNICAMP

E-mail: jacobus@fee.unicamp.br

#### Jr. Past President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### Sr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Vice President of Membership and Services

Ru Huang Peking University

E-mail: ruhuang@pku.edu.cn

#### Vice President of Publications and Products

Tsu-Jae King Liu University of California at Berkeley E-mail: king@eecs.berkeley.edu

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

#### Vice President of Technical **Committees & Meetings**

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith **IEEE Operations Center** E-mail: tlsmith@ieee.org

#### **Operations Director**

James Skowrenski **IEEE Operations Center** E-mail: j.skowrenski@ieee.org

#### **Content Management**

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IFFF prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) **Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2019                                                                                                                   | TERM                                          | <u>2020</u>                                                                                                                                     | TERM                                                 | <u>2021</u>                                                                                                                              | TERM                                          |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Joachim N.<br>Burghartz<br>Ru Huang<br>Shuji Ikeda<br>Meyya Meyyappan<br>Arokia Nathan<br>Jacobus W. Swart<br>Bin Zhao | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) | Roger Booth<br>Mukta Farooq<br>Edmundo A.<br>Gutierrez-D.<br>Benjamin Iniguez<br>Carmen M. Lilley<br>Durga Misra<br>Manoj Saxena<br>Sumant Sood | (1)<br>(2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(1) | Paul Berger<br>Navakanta Bhat<br>Maria De Souza<br>Kazunari Ishimaru<br>William (Bill) Nehrer<br>Murty Polavarapu<br>Camilo Velez Cuervo | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) |

#### NEWSLETTER **EDITORIAL STAFF**

#### **Editor-In-Chief**

Carmen M. Lillev University of Illinois at Chicago E-mail: clilley@uic.edu

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Rinus Lee GlobalFoundries E-mail: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

#### Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Edmundo A. Guiterrez-D. INAOE

E-mail: edmundo@inaoep.mx

#### **REGION 8** Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Marcin Janicki Lodz University of Technology E-mail: janicki@dmcs.pl

#### UK. Middle East & Africa

Jonathan Terry

The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Mike Schwarz Robert Bosch GmbH E-mail: mike.schwarz1980@ googlemail.com

#### **REGION 10**

#### Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia

E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.ip

#### **East Asia**

Mina Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

#### **N**EWSLETTER **D**EADLINES

**DUE DATE** ISSUE October July 1st January October 1st April January 1st April 1st July

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright @ 2019 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

# MARVELS OF MICROELECTRONIC TECHNOLOGY: THE 1T-1C DYNAMIC RANDOM ACCESS MEMORY, FROM A GROUNDBREAKING IDEA TO A BUSINESS BENCHMARK

(continued from page 1)

his 2013 Kyoto Prize Award ceremony as well as in journals/magazines papers [1], [2].

In the time period of Dennard's invention (mid-1960s), IBM mainframe computers were equipped with a maximum of 1 MB magnetic-core memory capacity. The access time was in the range of 1-2 microseconds, and power dissipation was about 40 kW. Those features are orders of magnitude larger than the ones we are used to on our today's handheld mobile phones! In 1971, the first semiconductor memory equipped IBM mainframe computers were based on 128 bit/chip bipolar design [2]. The six transistor (6T) memory cell (2 cross coupled flip flops and 2 bitlines access transistors) was the standard benchmark reference [3]. To compensate the lack of performance of 6T MOSFET arrays, Pleshko and Terman proposed to interface them with bipolar support circuits in order to drive large interconnect loads with low impedance devices [4]. n-MOSFET design started to be convincing by its potential lower cost and scalability, coming together with a speed increase and reduced power consumption, which narrowed the gap with bipolar Figures [5]."

Dennard was struck by an unexpected fact, where he states: "One day in late 1966 an important event in my life occurred. During the day I attended a large IBM Research conference where various projects were presented. ... I was very impressed by a description of a proposed thinfilm magnetic memory, which was projecting hundreds of thousands of bits in a 25 cm wide memory board... they had a very simple memory cell, just a small square of magnetic material at the intersection of two etched copper lines. I was inspired to find something that

Figure 1 From left to right: (Standing) Hideo Sunami and Mitsumasa Koyanagi (Sitting) Kiyoo Itoh and Robert Dennard at the 2006 IEEE Award Ceremony. Itoh, Sunami, and Koyanagi were honored with the 2006 IEEE Jun-Ichi Nishizawa Medal. (Front cover of IEEE SSC Newsletter, Winter 2008, vol. 13, n°.1)

simple for the technology we were developing." [1], [2]

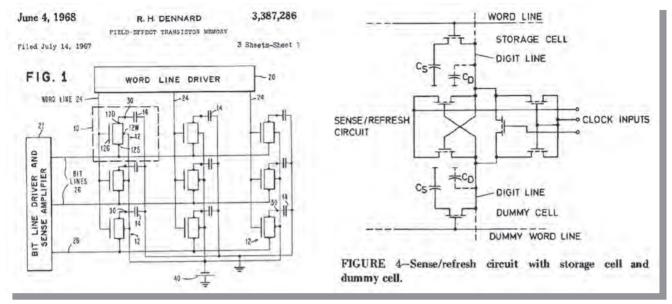

Such a simple idea has been so powerful in the long term and is still a source of inspiration nowadays to those who build cross bar arrays or are ever looking for the Universal Memory. "I found that an MOS transistor in series with each capacitor could be used as a switch to connect the capacitor to a data line briefly to charge or discharge it to write a data bit, represented by a positive voltage level, +V, or a zero voltage level on the bit line. The transistor is turned on and off by a control signal on a word line which allows selecting a given capacitor from many others for receiving the data on that bit line." [1], [2] The basic idea of 1T1C DRAM was born that same day in late 1966. Dennard restlessly kept on working for several weeks on various configurations. He finally realized that the stored charge could be written and read through the same nonlinear device which is the access transistor, that would create a small signal on the bit line: "The cell had been reduced to a single transistor and a capacitor at the intersection of two access lines [1], [6]. I was satisfied that this was as close to my goal as possible, and offered a great reduction in complexity compared to the six-transistor memory cell." (Figure 2 Left)

Nevertheless, MOSFET technology needed to prove its capability because the mainly used p-channels transistor speed was lower than for the bipolar competitor. Moreover, MOSFETs' characteristics, based on interface inversion, were still not well controlled. In that context, Intel realized the first silicon gate 3 p-channel transistor DRAM in 1970 [7]. The first proposal of 2 kbits "One device RAM chip" design, based on MOSFET technology, was published in 1971 [8]. 4 kbit chips became commercially available in the mid 1970s.

Besides the technology, further development consisted in layout

Figure 2 (Left) Detail from R.H. Dennard's 1st Patent of 1T1C DRAM [6]; (Right) Open Bitline 1T1C DRAM array architecture by K.U. Stein et al. presented at 1972 IEEE ISSCC [11]. The sense-and-refresh circuit is shared by 2 bitlines both connected to a large number of DRAM storage and dummy memory cells (first pair only represented) through two latch nodes

optimization to pack up as much as possible the bit cell, possibly including self-aligned contacts and two poly layers, to realize both a transistor gate and a capacitance plate [9]. At the chip level, innovations were guided by the necessity to match bitlines and wordlines pitches, including the row and column decoders layout, with the bit cell arrays without sacrificing the performance and noise Figures [9]. The small signals delivered by the bitcell and the necessity to restore them requested innovations in the design of the sense amplifiers [2]. Dennard reminds how critical it was to make DRAM products design manufacturable from the first idea of latch based sense amplifier in 1970 [10] and the implementation of the Open Bitline architecture using a cross-coupled differential sense amplifier based on a combination of each bitcell with a dummy cell. first presented at the 1972 ISSCC [11] (Figure 2 Right), refined in its "double cross coupled" version in IBM's 64 kBit DRAM in 1977 [12]. However, the solution to noise problems, potentially introduced by imbalances in the arrays, was brought by the Folded Bitline architecture invented by Itoh [13] in 1974 (see more hereunder "Folded Bitline and revised Open Bitline architectures" section). At this early stage of development, the necessity to introduce redundancy in order to maximize production yield appeared and was reported by IBM and Bell Laboratories [14], [15].

In the early days, Dennard's approach received also criticism, including internally at IBM, despite the fact that the architecture was considered as the simplest for a memory cell. As an example, we report a comment on 1T1C DRAM drawbacks "The cell has a number of drawbacks... the readout is destructive, the stored charge distributes between the cell and bit line capacitances and the writing speed is limited by the information storage capacitor which must be made large enough to yield a reasonable sense charge" [5]. However, Dennard explains that such a specific situation can be managed: "A distinctive characteristic of this memory cell is that a small leakage current from this n-doped region to the p-type silicon substrate discharges the capacitor in a fraction of a second. This gives rise to the name "dynamic" since the data is only stored temporarily. To preserve the data it must be refreshed by reading it out and writing it back into each cell at certain intervals. Fortunately, the speed of this memory scheme allows more than a hundred million read or write operations per second and only a small percentage of these are needed for refreshing the data. Thus, this scheme became known as dynamic RAM, and commonly called DRAM." [1]

Once the 1T1C concept was proven, competition started raging to scale down the memory devices driven by performance and density increase. At Hitachi, another main frame computer company, two concepts came out almost concomitantly, driven by two talented imaginative engineers, IEEE Fellows and Professors Hideo Sunami and Mitsumasa Koyanagi, as original solutions to respond to the scaling challenge. One was using capacitors embedded into trenches etched in the substrate and the second one stacked a capacitor on top of the addressing (write/refresh, sense/erase,) devices. These approaches were among the first attempts to exploit the 3rd-Dimension to improve microelectronics circuit density and were going to become benchmark circuits

for technology scaling, but their inventors probably were not conscious of it, at the time.

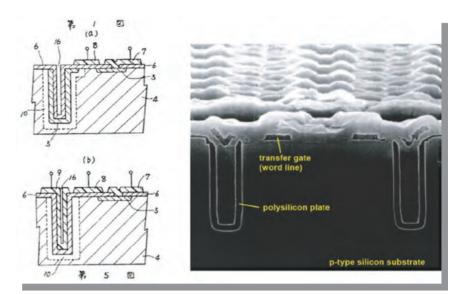

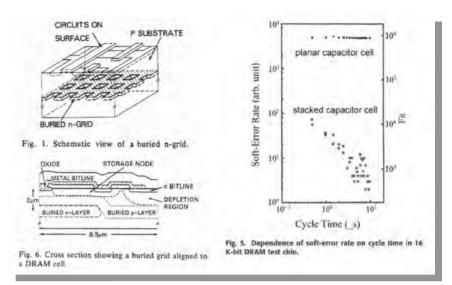

#### **Trench Capacitor DRAM**

Hideo Sunami proposed the trench capacitor approach. He was inspired by a combination of Dennard's 1T1C approach, his background on electronic components engineering and his youth passion for radio engineering. He entered Tohoku University in 1963 and joined Hitachi Central Research Laboratory (CRL) in 1969 after his graduation from Prof. Junichi Nishizawa's laboratory in 1969.

Hideo Sunami was very much involved in CCD research at Hitachi and that naturally led him to be interested in the DRAM because CCD were very demanding in terms of silicon engineering and more precisely gettering, doping and materials purity control. He proposed to make the capacitor of the 1T1C DRAM by etching a trench capacitor into silicon. Sunami thought that by adjusting the trench depth the capacitance value could be increased without increasing the capacitor footprint [16] (Figure 3 Left). Sunami told us: "At an early stage of my junior-high school age I fell in love with two hobbies. One was collecting butterflies and the other was hand making of short-wave radio receivers and transmitters. Then I have made myself to be very familiar to electronic components such as vacuum tubes, transistors, resistors, capacitors, etc. by the time I entered Tohoku University in 1963."

Hitachi CRL offered him a leave opportunity at Stanford University. His imagination was struck by marvels achieved in a completely different area while he attended a conference: "In the conference I was awfully shocked by some presentation where truly vertical trench of aspect ratio of almost 5 was formed on (110)-oriented silicon surface. In those days, truly vertical trench could not be formed on silicon surface but spherical crater-like hollow was formed even by using plasma etching." He knew from

Figure 3 (Left) Trench Capacitor DRAM patent H. Sunami and S. Nishimatsu, Japanese patent application, Tokugansho 50-53883, 1975 [16]; (Right) SEM cross section of first 1-Mbit Trench Capacitor cell DRAM, presented at 1982 IEDM by Sunami et al. [18]

his experience on CCD that surface characterization was a major tool to master the integrity and reliability of silicon devices.

Sunami continues: "On the other hand, I was hearing that one-device and one-capacitor DRAM cell had been recently invented. Despite the on-going research on surface characterization at Stanford, I got an inspiration of a first trench capacitor cell concept based on a combination of that DRAM cell and a cylindrical trimmer condenser used in radiofrequency transmitter. I requested my department boss at CRL to send me abroad a patent application form. His answer was negative. He told me: "You should concentrate on on-going research." Therefore, the first trench-capacitor cell patent was applied in 1975, several months after I left Stanford. Since the patent was not classified to be excellent, it was not applied to US!"

In the late 1970s and 1980s, Hitachi became one of the major actors on the DRAM business by first introducing Trench capacitor DRAM. Hitachi's 1-Mb DRAM was first presented at 1984, ISSCC [17] featuring a Corrugated Cell Structure that was first reported at 1982 IEDM [18] (Figure 3 Right) and received the IEEE Paul Rappaport Award in 1984 [19].

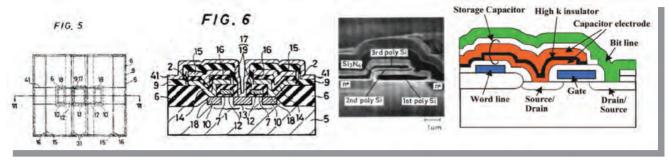

#### Stacked Capacitor DRAM Cell

Another challenging approach to the scaling of DRAMs was the 1T1C cell using a so called "Stacked Capacitor." While the storage capacitance decreases by following their linear scaling, the number of stored charges decreases. The stored charge can thus incur severe variations. Mitsumasa Koyanagi points out: "The number of signal charges stored in the storage capacitor has to be maintained at almost a constant, or can be only slightly reduced, as the memory cell size is scaled down. However, MOS capacitor value—and hence the amount of signal charges—is significantly reduced as the memory cell size is reduced, even if the capacitor oxide thickness is scaled-down. Therefore, I forecasted in 1975 that the 1-T cell with a two-dimensional (2D) structure using a planar MOS capacitor eventually would encounter a scaling-down limitation because it was not possible to reduce the MOS capacitor area according to the scaling theory." [20] The second reason to find an alternative was to reduce the influence of minority carriers generated in the

Figure 4 (Left ) Capacitor over Bitline Basic principle of stacked capacitor cell DRAM [22]; (Middle) 3 µm NMOS Stacked capacitor DRAM presented by M. Koyanagi et al. at IEDM 1978 [21]; (Right) Schematic cross-section of Capacitor Over Bitline [20]

silicon substrate on the storage node charges, degrading thus retention time and soft error immunity.

Using a vertical capacitor (exploitation of the 3rd-dimension) would give more flexibility to fix the capacitance value. If the vertical capacitor is located far from the silicon substrate, then the degradation of retention and soft errors immunity by the minority carriers is dramatically reduced.

"An inversion layer capacitance and a depletion layer capacitance are connected with the gate oxide capacitance in series in the MOS capacitor. The charges in the inversion layer and the depletion layer are easily affected by the minority carriers, which are thermally or optically generated or generated by the irradiation of energetic particles in a silicon substrate."

Koyanagi had a good knowledge of MOS interface physics. "In my Ph.D. research during 1971-1974 [3], I had commented on the silicon surface and the inversion layer in MOS structures. To evaluate the electrical properties of the interface states and the inversion layer, I myself built an impedance analyzer with the frequency range of 0.01 Hz to 100 MHz. I examined various kinds of capacitors, including high-k (high dielectric constant) capacitors as a reference capacitor of this impedance analyzer. Eventually, I made a vacuum capacitor for a reference capacitor in which fin-type capacitor electrodes were encapsulated in a vacuum container."

Koyanagi also used a  $Ta_2O_5$  film as a capacitor insulator for the first time [21].  $Ta_2O_5$  has a dielectric constant

five or six times larger than that of  $SiO_2$ . Therefore, the storage capacitance can greatly be increased, although the leakage current is larger than for  $SiO_2$  or  $Si_3N_4$  (for the same thickness) because of a lower bandgap value.

Koyanagi proposed the Capacitor Over Bitline (COB) concept which laid out the capacitor structure on top of the access transistor [21], [22], [23] (Figure 4). Many ways have been explored to increase the capacitance value per unit area by playing with the actual capacitance area spread in 3D either by wrapping multiple electrodes (Fin type capacitors, 1st publication by Fujitsu in 1988 [24]), increasing the plate electrode area with large hemispherical grains polysilicon(1st publication by NEC in 1990 [25]), or a cylindrical capacitor (1st publication in 1989 by Mitsubishi [26]) which have been extended to Multigigabit DRAMs till nowadays.

The concept of the COB-type stacked capacitor cell—that various kinds of materials can be stacked on the switching transistor using a lower temperature process—has been carried on in new memories with a three-dimensional structure such as Fe-RAM (Ferroelectric RAM), P-RAM (Phase Change RAM), R-RAM (Resistive RAM) and M-RAM (Magnetic RAM). [20]

Further on Koyanagi spent much of his energy on the generalization of 3D stacking. His work with his team at Tohoku University is recognized as a reference in the packaging and 3D community. By intensively using wafer bonding and Through Silicon Vias (TSV), he has been instrumental in creating a way to give a new breath to Moore's law. He did that not only to increase DRAM capacity but also to cointegrate heterogeneously different types of circuits [27].

# Soft Errors and the "DRAM Midlife Crisis"

Once the DRAM circuits complexity and production volume increased, stochastic and statistical effects started to appear such as Soft Errors. In 1979, two research groups at Intel [28] and Bell Laboratories [29] revealed that 16kbit DRAMs could suffer from transient error due to bombardment by alpha-particles and subsequent excess minority carrier generation in the substrate. Dennard points out: "The alpha particles were identified as coming from radioactive impurities in the materials of the hermetically-sealed packages...an analysis of the possible soft-error rate due to cosmic rays showed that this source could be significant. Personally, I felt very responsible because of my early role with dynamic RAM's and because I failed to anticipate the problem." [1] A good understanding required building a model based on a Monte Carlo approach developed by G Sai-Halasz. A solution based on a self-aligned buried n-grid to protect against radiation-induced charge collection was proposed [30] (Figure 5 Left): "It was shown that error rates would rise in response to scaling to smaller dimensions, but that design changes including error-correction techniques would contain the problem. The midlife crisis was over."

In our exchanges, Dennard further commented: "IBM was also careful to replace radioactive lead and other sources of alpha-particle emissions in order to limit soft-error rates (SER). IBM chose trenches to avoid disrupting our back end of line (BEOL) process with a tall stacked capacitor. The designers wanted a big memory-cell capacitor to support large arrays (long bit lines) and we knew how to etch really deep trenches."

Within Hitachi, the concern on SER, besides the caution taken on packaging, led to make drastic choices on the architecture. The different approaches of Trench DRAM and Stacked capacitor (STC) were shown to behave quite differently with respect to the soft errors. Sunami comments "Hitachi was one of the biggest main frame makers in the world at that time, and was as much concerned like IBM, the huge giant. The computer division of Hitachi became very nervous to degraded SER of which home-made DRAM provided." He considers that DRAM in consumer equipment market did not require main-frame level SER. Consequently, many manufacturers such as NEC, Toshiba, IBM, TI, Siemens shipped 1-Mbit DRAM integrating trench capacitors. "Some of them applied modified trench capacitors having improved SER." The idea was based on the collection of minority carriers through a highly conductive buried electrode. Examples such as the use of self-aligned buried grids [30], p+ substrate or n+ sheath plates under the storage capacitor have been used [31], [32], [33], as well, to control cell to cell leakage current.

Koyanagi showed to the DRAM community in Japan the results that a soft error rate could be dramatically reduced by almost three orders of magnitude by employing a Stacked Capacitor Cell as compared to a planar capacitor cell. This very important result was mentioned in his IEEE TED paper in 1980 [34]. Koyanagi comments: "My boss in

Figure 5 (Left) Self aligned buried n-grid protection for soft error immunity, as proposed by Wordemann et al. [30]; (Right) Dependence of Soft Error Rate on 16 kDRAM cycle time. Comparison of Stacked Capacitor Cell and unprotected Planar Capacitor Cell [20]

Hitachi at that time cut the Figure of soft error characteristics from the 1980 TED paper. He said that data of STC soft error was very important internally in Hitachi and hence data indicating the superior immunity to soft error of STC should be confidential for outside." Koyanagi obtained permission for publication on the evidence of the superiority of STC on soft error immunity only in a Japanese paper [35]. The Figure demonstrating such a superiority appeared in IEEE SSCS News in 2008 [20] (Figure 5 Right). Koyanagi concludes: "Today, the three major DRAM companies are Samsung, Hynix and Micron. These three DRAM companies have been using the Stacked Capacitor Cell from 4 Mbit DRAM to 8 Gbit DRAM and maybe 16 Gbit DRAM."

#### **Folded Bitline and Revised Open Bitline Architectures**

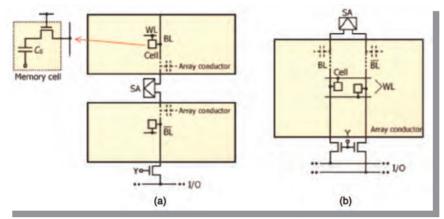

Another benchmark innovation for DRAM success, that had become an industry standard from the 1980s to the mid-2000s, is the invention of the Folded Bitline (Folded BL) arrangement at the end of 1974 by IEEE Fellow Kiyoo Itoh of Hitachi CRL [13]. The first demonstration was made by a presentation of a 64-kb DRAM at ISSCC in Feb. 1980 [36].

The Folded BL uses a pair of balanced BLs running close to one another and are parallel on the same conductor, equalizing and thus cancelling noise voltages coupled to the pair, caused by voltage bounces in an array, with the differential amplifier [37] (Figure 6). Moreover, a metal BL reduced soft-error noise caused by diffused-BL structures of the Open BL. Although in principle the Open BL realizes a smaller cell size of  $6F^2$  (F is feature size) than the Folded BL  $(8F^2)$ , the much larger cell compensates the noise voltages with a larger signal voltage. Itoh comments: "Unfortunately, a simple single metal-layer 5-µm process available at that time could not suppress the noise voltages sufficiently. Consequently, the 64-kb DRAM enabled stable operations despite a drastic reduction of the operation voltage  $V_{DD}$  to a TTL-compatible 5 V from 12 V for the 16-kb DRAM... In the cradle of DRAM, no one knew solutions for stable operations under array noise and soft errors and thus at the beginning I could not convince top managers on the importance of the innovation." Since that time until the mid-2000s, the Folded-BL was adopted for nearly all DRAM chips produced. In 2002, however, based on in-depth analysis of array noise,

Figure 6 Comparisons of [37]: (a) Open Bitline arrangement and (b) Folded-Bitline arrangement. SA: Sense amplifier; Y; Column select-line; I/O: Common data-in-and data-out-lines-see also [13]

Itoh's team [38] revealed the possible revival of the open-BL with  $6F^2$ , if an advanced vertical capacitor cell for a larger cell signal voltage and a threelevel metal layer process for reduced voltage bounces were used. Triggered by the 2002 JSSC paper [38], major DRAM players such as Samsung, SK Hynix and Micron have gradually changed the cell to the 6F2 Open BL, starting with 512-Mb DRAMs in 2005 [39], reaching nowadays 10-nm-class 16-Gb DRAMs [40]. Stacked modules with 8 single-16-Gb-DRAM chips [41] contribute to high density servers and mobile applications. Itoh underlines: "The addition of an on-chip voltage down-converter to protect internal miniaturized devices [42] and reduction circuits of the everlarger subthreshold-leakage current [43], are also key contributors to DRAM success."

The simplicity of Dennard's 1T-1C DRAM principle has kept it unbeaten by any other solution and certainly qualifies it a Marvel of Microelectronic Technologies. A lot of technical progress has been achieved worldwide, since its invention, year after year: Dennard, Sunami, Koyanagi and Itoh are certainly key persons who made it happen. Future prospect to reach a smallest footprint of 4F<sup>2</sup> have already been highlighted, thanks to a vertically stacked access transistor and a high aspect ratio ca-

pacitor based cell [44], featuring a revised Open BL architecture.

#### References

[1] R.H. Dennard, "Reflections on Creativity in My Microelectronics Career," 2013 Kyoto Prize Lecture, 18 pages Available at: https://www.kyotoprize.org/wp/wp-content/uploads/2016/02/29kA\_lct\_EN.pdf

[2] R.H Dennard, "Evolution of the MOSFET Dynamic RAM—A Personal View," IEEE Trans on Electron Devices, vol. ED-31, n"11, pp. 1549–1555, 1984 and RH Dennard, "Revisiting "Evolution of the MOSFET Dynamic RAM—A Personal View," IEEE SSCS NEWS, Winter 2008, p. 10, 2008.

[3] J.D. Schmidt, "Integrated MOS random access memory," Solid State Design, p.21, Jan. 1965.

[4]. P. Pleshko and L.M. Terman, "An investigation of the potential of MOS transistors memories," IEEE Trans. On Electron. Computer, vol EC-15, Aug 1966, pp. 423–427.

[5] L.M. Terman, "MOSFET Memory Circuits," Proc. IEEE, vol. 59, pp. 1044– 1058, July 1971.

[6] R.H. Dennard, "Field Effect Transistor Memory," US Patent 3 387 286, June 4, 1968.

[7] W.M. Regitz and J.Karp, "A three transistor cell 1024 bits, 500ns MOS RAM," ISSCCTech. Dig. p.42, Feb 1970.

[8] L.Cohen, R. Green, K.Smith, and J.L. Seely, "Single-transistor cell makes

room for more memory on a MOS chip," Electronics, p. 69, Aug. 2, 1971.

[9] V.Leo Rideout, "One-Device Cells for Dynamic Random-Access Memories: A Tutorial," IEEE Transactions on Electron Devices, Vol. ED-26, No. 6, June 1979.

[10] D.L. Chritchlow, "Sense Amplifier for IGFET Memory," IBM Tech Discl. Bull., vol. 13, n°6, p. 1720, 1970.

[11] K.U. Stein, A. Sihling, E. Doering, "Storage Array and Sense/Refresh Circuit for Single-Transistor Memory Cells," ISS-CC Dig. Tech. Papers. pp. 56–57, Feb. 1972.

[12] Heller, L.G. and Spampinato, D.P., "Cross-Coupled Charge Transfer Sense Amplifier Circuits," U.S. Patent 4,039,861; Aug. 2, 1977, and L.G. Heller, "Cross-Coupled Charge-Transfer Sense Amplifier," ISSCCTech Digest, pp. 20, 1979.

[13] K. Itoh, Jap Patent-1146400, filed Dec. 25, 1974 and US Patent-4044340, Dec. 29, 1975.

[14] Schuster, S.E., "Multiple Word/ Bit Line Redundancy for Semiconductor Memories," IEEE J. Solid-State Circuits, 92-13, pp. 698–703, 1978.

[15] R. Cenker , D. Clemons , W. Huber et al. , "A fault-tolerant 64K dynamic RAM," ISSCCTech Digest , p. 150, 1979.

[16]. H. Sunami and S. Nishimatsu, Japanese patent application, Tokugansho 50–53883, 1975.

[17] K. Itoh, R. Hori, J. Etoh et al, "An Experimental 1Mbit DRAM with On-Chip Voltage Limiter," Technical Digest of IEEE Internat. Solid-State Circuits Conf., pp. 282-283, San Francisco, Feb. 22–24, 1984.

[18] H. Sunami, T. Kure, N. Hashimoto et al., "A CORRUGATED FOR CAPACITOR MEGABIT DYNAMIC MOS MEMORIES CELL (CCC)," Dig. of Tech. Abstracts IEDM 1982, pp. 806–808.

[19] H. Sunami, T. Kure, N. Hashimoto et al., "A Corrugated Capacitor Cell (CCC)," IEEE Trans. Electron Devices, Vol. ED-31, No. 6, pp. 746–753, 1984.

[20] Mitsumasa Koyanagi, "The Stacked Capacitor DRAM Cell and Three-Dimensional Memory," IEEE SSCS News, pp. 37–41, Winter 2008.

[21] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, "Novel High Density, Stacked Capacitor MOS RAM," Ext. Abs. of the 10th Conference on Solid State Devices, 1978.

[22] M. Kovanagi and K. Sato, Japanese patent application, Tokugansho 51-78967, 1976. and M. Koyanagi and K. Sato, USP-4151607, Jan. 5, 1977.

[23] M. Koyanagi, H. Sunami, N. Hashimoto and M. Ashikawa, "Novel High Density, Staked Capacitor MOS RAM," IEDM Tech. Dig., pp. 348-351, Dec. 1978.

[24] T. Ema: S. Kawanago, T. Nishi et al., "3-dimensional stacked capacitor cell for 16 M and 64 M DRAMS," IEDM, pp. 592-595, 1988.

[25] M. Sakao, N. Kasai, T. Ishijima et al. "A CAPACITOR-OVER-BIT-LINE (COB) CELL WITH A HEMISPHERICAL-GRAIN STORAGE NODE FOR 64Mb DRAMS." IEDM, pp. 655-658, 1990.

[26] W. Wakamiya, Y. Tanaka, H. Kimura et al., "Novel Stacked Capacitor Cell for 64Mb DRAM," Symposium on VLSI Technology Dig. Tech. Papers, pp. 69-70, 1989.

[27] T. Fukushima, Y. Yamada, H. Kikuchi, and M. Koyanagi, "New Three-Dimensional Integration Technology Using Self-Assembly Technique," IEDM Tech. Dig., pp. 359-362, Dec. 2005.

[28] T.C. May and M.H. Woods, "Alpha Particles Induced Soft Errors in Dvnamic Memories," IEEE Trans. On Electron Devices, vol. ED-26, n°1, pp. 2-9, 1979.

[29] D.S. Yaney, J.T. Nelson, L.L. Vanskike, "Alpha-Particle Tracks in Silicon and their Effects on Dynamic MOS RAM Reliability," IEEE Trans. On Electron Devices, vol. ED-26, n°1, pp.10-16, 1979.

[30] M.R. Wordeman R.H. Dennard G.A. Sai-Halasz, "A Buried n-grid for Protection Against Radiation-Induced Charge Collection in Electronic Circuits," IEDM Digest Tech. Papers, pp. 40-43, 1981.

[31] N. Lu, P. Cottrell, W. Craig et al., "THE SPT CELL-A NEW SUBSTRATE-PLATETRENCH CELL FOR DRAMS." IEDM Tech Digest, pp. 771-772, 1985.

[32] Sunami H., Kure T., Kawamoto Y. and Miyao M., Semiconductor Memory, Japanese patent application: Tokuhansho 57-192478(1982); Semiconductor memory, US Patent 4,901,128.

[33] Toru Kaga, Yoshinobu Nakagome, Hideo Sunami et al., "Half- Vcc Sheath-Plate Capacitor DRAM Cell with Self-Aligned Buried Plate Wiring," IEEE Trans. on Electron Devices, ED-35, n°8, pp. 1257-1263, 1988.

[34] Mitsumasa Koyanagi, Yoshio Sakai, Masamichi Ishihara et al., "A 5-V Only 16-kbit Stacked-Capacitor MOS RAM," IEEE Transactions on Electron Devices;, Vol. ED-27, n°8, August 1980, pp. 1596-1601.

[35] M. Koyanagi, Y. Sakai, M. Ishihara et al. "16-kbit Stacked Capacitor MOS RAM," IEICE Technical Report (Japanese), SSD80-30, 1980.

[36] K. Itoh, R. Hori, H. Masuda et al., "A single 5V 64K dynamic RAM," ISSCC Dig. Tech. Papers, pp. 228-229, Feb. 1980.

[37] Kiyoo Itoh, "The History of DRAM Circuit Designs-At the Forefront of DRAM Development," IEEE SSCS News, pp. 27-31, Winter 2008

[38] T. Sekiguchi, K. Itoh, T. Takahashi et al., "A low-impedance open-bitline array for multigigabit DRAM", JSSC, vol. 37, pp. 487-498, Apr. 2002.

[39] Geoff MacGillivray "Process vs. Density in DRAM", EETimes, 07.04.05.

[40] Seokbo Shim, Sungho Kim, Jooyoung Bae et al., "A 16Gb 1.2V 3.2Gb/s/pin DDR4 SDRAM with Improved Power Distribution and Repair Strategy", ISSCC Dig. Tech. Paper, pp. 212-213, Feb. 2018.

[41] Seongju Lee, Byungdeuk Jeon, Kyeongpil Kang et al., "A 512GB 1.1V Managed DRAM Solution with 16GB ODP and Media Controller", ISSCC Dig. Tech. Paper, pp. 384-385, Feb. 2019.

[42] M. Horiguchi, M. Aoki, J. Etoh et al., "Dual-Regulator dual-Decoding-Trigger DRM Voltage Limiter for Burn-In Test," JSSC, vol. 26, no.11, pp. 1544-1549, Nov. 1991.

[43] M. Horiguchi, T. Sakata, and K. Itoh, "Switched-Source-Impedance CMOS Circuit For Low Standby Subthreshold Current Giga-Scale LSI's," IEEE JSSC, vol. 28,n11, pp. 1131-1135, Nov.

[44] Ki-Whan Song, Jin-Young Kim, Huijung Kim et al.," A 31ns Random Cycle VCAT-based 4F2 DRAM with Enhanced Cell Efficiency," 2009 Symposium on VLSI Circuits Digest of Technical Papers, pp. 132, 133.

## HIGHLIGHTS OF THE 2019 IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE

BY NED EKINS-DAUKES AND SARAH KURTZ

The 46th international 2019 IEEE Photovoltaic Specialists Conference (PVSC-46), was held June 16-21, 2019, at the Sheraton Grand Hotel in Chicago, Illinois. The PVSC is held annually and is the leading international conference on PV science and technology and one of the flagship conferences of IEEE sponsored by the Electron Devices Society. The conference hosted 1,150 attendees from 46 different countries: 56% from the USA, 7% from Japan, 5% from Germany, 4% from Australia, 3% from China and the remaining 25% from other nations. During the conference, 885 presentations were delivered.

The William R. Cherry Award is the highest award presented at the conference and was conferred to Harry Atwater (CalTech, USA) in recognition of his creative work since 1988, contributing to world-record GaAs cell efficiencies. His presentation highlighted the importance of the optical design and internal radiative efficiency of solar cells, introducing a luminescent concentrator GalnP cell integrated above a silicon cell. He cofounded Alta Devices and ETC Solar.

The Young Professional Award was renamed this year after the late Stuart R. Wenham. This year the award went to Zachary Holman for his research at Arizona State University. He gave a presentation "Advancements in Silicon Heterojunction Solar Cells," providing a cost analysis of tandem cells. He discussed examples such as III-V on silicon, perovskite on silicon and spectrum splitting configurations.

Best Student Paper Awards and Poster Awards were issued in various categories.

#### Outreach

The PVSC High School Competition hosted nine teams (32 students). Their solar energy research projects were supported by teacher-facilitators from their local schools as well as mentors from Arizona State University, University of New Mexico, and Purdue. Thanks to a generous grant from the NSF, 12 high school scholars from Arizona were able to travel to the conference to participate in person in the Monday-afternoon poster session with their Chicago-area peers. This cross-age event helped create a sense

of belonging for young aspiring engineers, communicating that we are all photovoltaics scholars, different in level, not type; all agreed that the event was a resounding success!

#### Keynote

The opening keynote was given by Dr. Ron Sinton on "The Path Towards a Major Utility Commitment for 100% Carbon-Free Electricity." Dr. Sinton explained how one of the largest electricity utility companies in the USA, Xcel, has pledged to become carbon-free by 2050. While the transition is motivated by an appetite from consumers for clean electricity, the transition is enabled by the competitive costs of wind and solar electricity; now cheaper than the marginal cost of coal in many locations. Additionally, Xcel makes the case that investment in solar and wind is advantageous for Xcel's investors, suggesting the beginning of a trend where investor-owned utilities may become primary drivers of solar expansion.

#### Special Session—Understanding the Value of Efficiency in Mainstream PV Markets

Kelsey Horowitz presented a comprehensive argument that solar power

conversion efficiency has a premium in space-constrained applications, e.g. rooftop generation in situations with high electrical demand, such as a household with an electric vehicle. Industry representatives shared a range of viewpoints, noting that note everyone is looking for the same product and sharing maps of where Winner technologies, Loser technologies, Niche products and Super Winners exist.

#### **Conference Highlights**

The PVSC-46's Technical Program included 12 areas covering cuttingedge developments in PV technology, ranging from fundamentals to applications, with an emphasis on material science, devices, PV systems, solar resources and policy. At present, the technical program can be easily digitally explored at https:// www.ieee-pvsc.org/ePVSC/mobile/ with papers available to conference attendees. The proceedings will be available in September. To give readers insights on the conference's vast program, this Technical Brief provides an overview of the conference highlights by area.

# Area 1 Fundamentals and New Concepts for Future Technologies

The Area 1 Plenary was given by Tom Markvart from the University of Southampton, UK, who used thermodynamics to explain the operation of a solar cell and the way the chemical potential of emitted photons is recovered through photon recycling. Recognizing that a significant fraction of the incident energy is lost to carrier thermalization. Tom outlined a thermoelectric approach for the implementation of a hot carrier solar cell, in which SQ efficiency could be surpassed. Jeronimo Buencuerpo from NREL presented ultrathin III-V solar cells using photonic crystals, demonstrating that a 2D photonic crystal on front and rear of 300 nm thin III-V cells enables absorption close to the Lambertian limit. Jacob Krich presented a figure

Conference participants, Richard King, Thorsten Trupke and Ron Sinton congratulate the new Cherry Award winner, Harry Atwater, second from right

of merit for intermediate band absorbers to predict when it is worthwhile to make devices. The figure of merit well described devices using a new open source device model, Simudo, available at github.com/ simudo/simudo. Daisy Xia described research on laser power conversion at 1310 nm, predicting that a 20 junction photonic power converters would achieve 13.7 V with a power conversion efficiency of 60%. Ian Sellers presented exciting results about hot carrier effects in thin bulk systems without nanostructuring. He demonstrated an InGaAs/AlInAs system, with an extrapolated V<sub>ss</sub> of 1.375 V, limited by the L valley of the conduction band rather than the conduction band minimum. Finally, Rob Patterson presented a computational study to screen new candidate materials for the top cell for a silicon tandem cell, such as CuZnSI, CuZn,S,I and CuZnSI,.

#### Area 2 Chalcogenide Thin Film Solar Cells

The Area 2 plenary was given by Raffi Garabedian, the CTO of First Solar. He summarized the transformation over the past decade in PV electricity generation, not just achieving grid parity but actually now being the cheapest source of energy; in some locations being cheaper than the marginal cost of a coal power plant. He emphasized that despite concerns from a decade ago, solar plants are now actually adding to grid stability.

Motoshi Nakamura from Solar Frontier presented record breaking results in "Cd-free Cu(In,Ga) (Se,S), thin-film solar cell setting a new record efficiency of 23.35%." Key were a CsF treatment and careful optimisation of the bandgap profile obtained by controlling Ga/(Ga+In) and S/(S+Se) ratios. Mahisha Amarasinghe from the University of Illinois reported that high group-V doping > 1016 cm-3 in CdSeTe thin films could be achieved by vapor transport deposition. An extensive study of KF,

Raffi Garabedian gives plenary lecture for Area 2

K, RbF, and Rb post-deposition treatments on (AgCu)(InGa) Se, solar cells by M. Edoff showed a low V<sub>ss</sub> deficit of 0.4 V. Thomas Fiducia presented 3D imaging of selenium distributions in high efficiency Se-graded CdTe solar cells, combining highresolution cathodo-luminescence images with elemental distributions to show a selenium deficit at grain boundaries in the regions with high selenium concentrations near the cell top surface and a surplus in bulk regions, induced by the diffusion processes during CdCl<sub>2</sub> treatment of CdSeTe/CdTe bilayers. Li et al., Danielson et al., and Yan et al. described innovations in the electron and hole contacts in CdTe solar cells, including air-free CdCl<sub>2</sub> treatments that prevent large conduction band offsets at the CdTe/MZO interface, a 30X increase in PL intensity compared to reference cells.

#### Area 3 Multijunction and **Concentrator Technologies**

Ryan France from NREL announced a 6-junction inverted metamorphic solar cell with a record efficiency of 47.1% at a concentration of 144 suns AM1.5D and 39.2% under the AM1.5G spectrum. Relatedly, Manuel Hinojosa further elucidated the behavior of Zn diffusion at sub-cell

interfaces and the role that point defects play in affecting dopant diffusion from tunnel junctions and M. Steiner described improvements made to the AlGalnP top junction. Steve Askins presented a CPV module with planar micro tracking that achieved 29% efficiency at CSTC and up to 25% energy boost with the diffuse contribution. Duanhui Li from MIT presented micro-prism spectrum splitting optics with a 75% optical efficiency. Matt Lumb presented a 5J CPV cell that achieved 35.4% that was assembled into a module using transfer printing. Sodabanlu et al. from AIST presented InGaP growth rate by MOVPE of >30 µm/hr with GaAs grown at 120 µm/hr. Metaferia et al. from NREL presented GaAs solar cells by HVPE with growth rates exceeding 300 µm/hr. Recognizing the competition between perovskite/ silicon and III-V / silicon technologies. there were a number of sessions on Hybrid Tandems dubbed "Battle Royale," S. Fan et al. reported on a 20% MBE-grown GaAsP/Si tandem solar cell. T. Grassman improved his group's 2018 record 20.1% epitaxially grown GaAsP/Si tandem cell to 21.8%. Improving the current of the Si cell, improving the GaP nucleation, and reoptimizing the top cell and buffer layer, showed a path to a 30% efficient device. Michael Rienaecker presented how three terminal silicon bottom cells work for tandems that are current mismatched in various configurations.

#### Area 4 Silicon Photovoltaic Materials and Devices

The Area 4 plenary was given by Denis De Ceuster from DDC Solar, providing an overview of passivating contacts for silicon solar cells. Standard Al-BSF technology is limited to 20% efficiency, rising to 23.5% with the emerging PERC architecture. To achieve higher efficiencies (up to 25%) requires passivated contacts. PERC also enables bifacial modules and is free from light-induced degradation. He reviewed three architectures: (1.) the silicon heteroiunction cell benefits from a short process flow with no high-temperature processing but may be 2.5x more expensive than the PERC process. (2.) Thin Tunnel Oxide Passivated Contact (TOPCon) is compatible with the PERC process, and adds only a couple of additional process steps to the production line, so is the least expensive of these. The TOPCon layer can be implemented on the rear of the cell with a standard diffusion on the front, or on both sides of the cell. (3) Non-silicon heterojunctions, where the doped amorphous silicon layers in (1) are exchanged with carrier-selective materials, e.g., TiO<sub>3</sub> as an electron contact and MoO as a hole contact and has similar disadvantages as the silicon heterojunction approach.

The session on "Innovations in Manufactured Solar Cells" was declared 'simply amazing' by the session chairs since the industry is entering an era of 23% screen printed cells with standard metallization processes. Trina Solar showed passivating contact n-type cell production (TOPCon) with record efficiency of 24.6%. ECN showed several approaches for passivating contacts, including PERC poly p-IBCQ-cells and bifacial PERC devices reaching

22 % (0.1% less than for monofacial PERC) with a bifacial factor of up to 0.77. SERIS is also working on passivating contact approach called monoPoly reaching 23.5% with 0BB. Meyer Burger showed a HJT 2.0 cell with record efficiency of 24.5%. Felix Hasse demonstrated a hybrid IBC structure using n-poly over tunnel oxide for n-contact and local Al-BSF for p-contact and have reached 21.8% on p-type (Ga-doped) on  $2 \times 2$ cells with screen-printed electrodes. Abhijit Kale presented comprehensive and convincing analysis of the tunnel layer formed by TOPCon and POLO approaches respectively. He showed an increase in recombination at the textured surface is caused by microroughness at the pyramid facets and nonuniformity of the oxides. The issue can be mitigated by an extra acid treatment.

# Area 5 Characterization Methods

The Area 5 plenary was given by Uwe Rau from Fz. Julich who showed how losses in a solar cell can be determined by either performing a detailed bottom up analysis, or by using reciprocity relationships between absorption and emission it is possible to use top-down methods such as luminescent imaging to extract surprisingly rich data from a solar cell. T. Song from NREL demonstrated the reliability of the asymptotic P<sub>max</sub> method, as compared to others methods (MPP tracking, SCFC) to measure IV curves of emerging PV devices. An uncertainty of more than 1 percent was estimated to persist. S. Reichmuth presented an overview of measurement issues encountered by calibration laboratories when measuring silicon solar cells with thin or discontinuous busbars. Use of coaxial I-V probes at Fraunhofer ISE shows promise over traditional I-V-I "triplet" configurations. Detailed procedures used for measuring "busbarless" cells were also presented. The ability to measure the voltage on the nanoscale to characterize individual PERC back contacts using photoconductive AFM tips was demonstrated by Bryan Huey. Using luminescence imaging, the temperature coefficient of implied voltages was demonstrated on multi-crystalline wafers from different positions of the ingot by Shuai Nie.

The Area 6 plenary was given by

# Area 6 Perovskite and Organic Solar Cells

David Cahen from the Weizmann Institute, who presented a comprehensive survey of halide perovskite materials and their application to PV. He noted perovskite materials' unusual properties, chiefly as a rare instance of a soft inorganic semiconductor. They also have remarkably low defect densities and in common with CIGS, they have a self-healing ability but with a much shorter time constant, 10 minutes as opposed to 10 years for CIGS. He summarized recent device results including 28% for a perovskite/silicon tandem cell by Oxford PV. C. Bailie presented work from Tandem PV on the complexities of scaling up halide perovskite PV architectures from cells to minimodules pointing out the relative advantages of laser versus mechanical methods for scribing through the various layers. V. Zardetto described Solliance's progress on scalable fabrication of 100 cm<sup>2</sup> area, semi-transparent halide perovskite PV modules using primarily slot-die coating and S2S ALD. Y. Huang employed a model to study the diffusion of mobile ions in perovskite solar cells and reproduce key characteristics such as hysteresis, etc. He applied 'Big data' analyses to determine key degradation mechanisms and sort them by significance (moisture, inclusion of oxygen, heat, type of CTL etc.) Finally, S. Lee reported on attempts to deposit a perovskite top solar cell on textured Si bottom solar cell by a dry two-step process. The perovskite layers grown on textured Si solar cells show good conformal layers, proven by partial LBIC and spatial PL. S. Manzoor performed optical modelling of all perovskite tandem PV cells, for the first time providing a complete set of optical constants of low- and wide bandgap perovskites.

#### Area 7 Space and Specialty **Technologies**

The Area 7 plenary was given by Yannick Combet from Thales, unveiling the concept for the Stratobus airship. Classed as a High Altitude Pseudo Satellite (HAPS) it is 140 m in length, operates at an altitude of 20 km and provides communication, navigation and observation services to civil and military clients. Power will be supplied by 300 kWp of PV with an array voltage of 1200 V. M. Imaizumi presented a novel mechanically stacked 3J cell made by from a top InGaP/ GaAs dual-junction (2J) cell and a 1.1 eV CIGS bottom cell designed for very high radiation resistance, with 94% efficiency remaining at EOL. P. Espinet-Gonzalez described the potential of Nanowire based GaAs and InP solar cells in terms of radiation hardness. A world record Nanowire cell with 16.9% efficiency (BOL) was presented. P. Chiu reported the qualification results for the lattice matched triple junction XTE family of cells developed at SpectroLab, including 32% BOL and 27.8% EOL efficiency. M. O'Neill gave a comprehensive overview of the technology development at NASA of space PV concentrators for outer planet missions, and in particular the cost and weight savings achieved from line-focus and pointfocus Fresnel lenses. He reported the lightest lenses made to date with 1 gram for 10 cm x 10 cm area.

#### Area 8 PV Modules Manufacturing and Applications,

K. Passow of First Solar analyzed mistracking related losses, which had large implications on a daily basis. K. McIntosh of PV Lighthouse presented a ray-tracing approach to analyze the performance of bifacial systems. He showed how SunSolve software uses cloud-based computation, micron-

level tracing of 20 million rays and includes intricate effects such as cell texture, coupled with SPICE simulation of the module circuitry. He was able to quantify the mismatch losses in single-axis tracker systems with bifacial modules. The non-uniform backside irradiance due to edge brightening and torque tube shading can lead to 0.2% cell-to-cell mismatch loss on the modules, the actual value depending on the module position. In addition, A. Wheeler showed that a GaAs module delivered a daily performance ratio (PR) of 98% while silicon modules had a PR of 90-94% on a cool day. B. Newman introduced the concept of dynamic shading; a momentary shading that can interfere with maximum power point tracking. Overall electricity yield losses due to dynamic shading could be >5% with the wrong electronics. At present, there is no specification supplied by a power optimizer manufacturer that could help inform optimizer choice. Finally, N. Shiradkar spoke on the damage to PV plants due to extreme flooding. In some cases the damage was extreme, while in other cases, often when the PV panels were at low inclination, damage to submerged panels was minimal and power output remained the same. The most frequent source of damage was due to flooded inverters that caught fire.

#### Area 9 PV Modules and System Reliability

Chris Deline from NREL gave an inspiring plenary talk on the fact and fiction associated with bifacial modules. The PERC silicon solar cell process lends itself to bifacial cell manufacturing; presently bifacial modules command a premium price in the photovoltaic market of around 5-6c/W. The fractional energy gain over a monofacial module is highest under diffuse irradiance, so the overall gain depends upon overall irradiance conditions as well as ground albedo. Bifacial modules now account for 2 GW cumulative installed capacity. R. Witteck demonstrated improved UV stability of PERC cells through the use of different AR coatings. This is important since UV with wavelength less than 365nm is often transmitted through EVA encapsulation. A graded layer of SiN, SiO/SiN, or a thermal oxide showed the best stability. L. Bruckman provided comparison of field exposed and accelerated exposures of backsheets. Jones provided a comparison of indoor and outdoor tests measured by the change of series resistance. IEC61215 TC200/ Qualification Plus TC500 tests were compared with outdoor exposures and clear correlations were observed. Saleh introduced a new analysis method (SSTDR) of PV arrays. Using an injected electrical pulse reflected at impedance discontinuities, disconnection, DH degradation, and PID could be detected. Several presentations addressed soiling of PV panels. M. Mazumder presented how a transparent electrodynamic screen can be used to remove particles from the PV module surfaces without water or moving parts. The scheme requires less than 0.2 Wh to clean a m2 of PV surface. The overall O&M advantages of electrodynamic film based systems were presented.

#### Area 10 Power Electronics and **Grid Integration**

Patrick Chapman from Enphase gave the Area 10 plenary describing how Solarbridge was spun out of the University of Illinois to become one of two successful microinverter companies. The business was acquired by SunPower in 2014 and then sold to Enphase last year. The Enphase product has a 97.5% end to end efficiency averaged over load and voltage and a 40-year design life, using a resonant AC link design including MOSFET and ASIC components. A. Haque presented a study of the effect of solar variability (cloud induced) on shortterm and long-term flicker severity for distributed and centralized PV across different geographical locations. B. Pierre described the issues caused by momentary cessation in grids with high PV penetration. A simulation of an actual feeder showed that with high PV penetration can cause over frequency on the feeder during fault with both slow and fast ramp rate. J. Roy spoke about a new multiport PV inverter architecture designed to suppress Idc ripple and thereby minimizing the dc-bus capacitor requirement.

# Area 11 Solar Resource and Forecasting

R. Perez showed how solar power can provide firm power at relatively low cost if state-of-the-art forecasts are used with over-sized PV power plants and energy storage. N. Engerer described how in Australia solar power forecasting on distribution systems is on the verge of being used operationally by distribution system operators for maintenance scheduling and management/operations. J. Peterson presented on how a disparity between reference-cell performance and pyranometer measurement data motivates a high quality experimental

sensor station in Golden, Colorado. The output from the IMT reference cells can be predicted to within -2% for zenith angles less than 85 degrees.

# Area 12 PV Deployment, Policy, and Sustainability

Andrew Blakers from UNSW made a compelling case for pumped hydroelectric storage in the area 12 plenary, presenting the technology as the key to a 100% renewable energy electricity supply. He argued that PV and Wind have won the energy race, and that pumped hydro can provide the needed storage. His survey of pumped hydro sites has identified 616,000 off-river sites with a storage capacity of 23 million GWh, much more than is required to store renewable energy for the entire planet. An online atlas of pumped hydro sites is available http://re100 .eng.anu.edu.au/global/. I. Kaizuka summarized the freshly released annual report from IEA-PVPS on global PV markets. The global cumulative capacity has reached 500 GW and heading towards the terawatt era. At present 2.6% of global electricity generation is derived from PV. A. Jaeger-Waldau summarized the New EU RE directive 2018/2001/EU. describing at least 32% RES share in the EU allowing households and businesses to become clean energy producers. The EU PV market is recovering in many EU countries, possibly totaling around 15GW this year. H. Apostoleris discussed the role of financing in achieving ultra-low electricity prices in the Middle East, finding that the low power purchase agreement prices were the result of factors like low-interest rates and hvbrid ownership models.

The authors acknowledge the full Program Committee and the many authors and presenters who chose to present their outstanding work at PVSC-46. Our difficulty in choosing highlights from such a strong field of presentations testifies to the quality of the work presented.

## THE ITRS AND THE NEW IRDSTM

By Francesca Jacopi and Terry Hook

Most of us are probably familiar with the semiconductor industry's roadmaps for the future. For the past four decades, the transistor has been king. Closely assisted by courtiers such as advanced lithography, advanced gate technologies, and the associated plethora of new oxide and contact materials, and supported by increasingly complex interconnects, the transistor has governed the semiconductor roadmap over the last several decades. For many generations, a smaller transistor meant a faster and more powerful processor. These were halcyon years for the Electron Devices Society as well. Devices were in the driver's seat; and the Roadmap

was ours. The semiconductor community would do anything necessary to keep on scaling down the channel length. Today's world is far more complex—and interesting—and today's Roadmap reflects that.

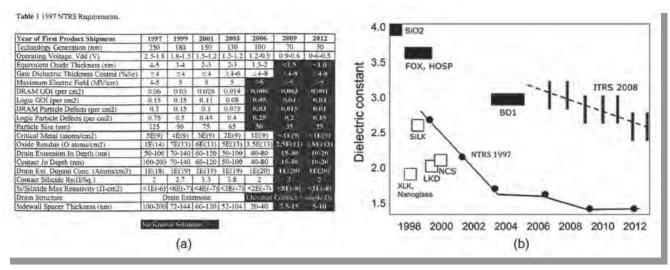

Both industry and academia consult the Roadmap to obtain perspective on where to direct their own efforts, even if their underlying purpose is to "beat the Roadmap;" that is, for their own internal plans to reference the Roadmap but to do better. The "old" Roadmap can claim a number of successful predictions. In the mid-90's the Roadmap (then known as the NTRS) sounded the tocsin of doom for gate dielectric scaling, not-

ing that there were then no solutions known to drive below a 1.5 nm effective thickness, which was expected to be required in 2009 (Fig. 1a). Research was accelerated, and, as early as 2007, high-k dielectrics were introduced into high-volume manufacturing, breathing new life into classic Dennard transistor scaling. Similarly, the limitations of conventional photolithography were delineated in Roadmaps through the 1990's, prompting enormous innovations over the following decade such as double -exposure and then immersion lithography, to drive dimensional scaling beyond the diffraction limit in air. Had the Roadmap not articulated a unified

Figure 1 (a) Excerpt from 1997 NTRS Roadmap [1]. (b) Early optimistic predictions for dielectrics [2]

pre-competitive perspective of those key challenges early on, building consensus and buy-in from the whole semiconductor value chain, would these and other vital innovations have been developed? Perhaps so, but certainly not in such a timely fashion. In the interest of honesty, the Roadmap has also had its share of misses—they could also be described as "unfulfilled challenges" or maybe even "wishful thinking"-either way they have set a goal for the whole community to try and achieve. In one of the most notorious examples, the 1997 version anticipated interconnects insulators with a dielectric constant of less than 1.5 in 2012 (Fig 1b). Despite intense R&D in materials and integration for over a decade, even today's production has never really gone much beyond the integration of materials with k = 2.5. Interconnects have been one of the most underestimated challenges in the history of the semiconductor roadmap. Nevertheless, the Roadmap has successfully brought nanotechnology to mass-scale production, bridging the long valley of death between lab-based conceptual solutions to production-scale technologies from advanced lithography to novel materials for frontend to backend technologies.

The classical CMOS transistor has not really been exclusively preemi-

nent for some time, however. Today's systems need broad diversification. Even within the context of classic Von Neumann computing, hardwarebased accelerators, such as intimate CPU/GPU connections like NVlink and CPU/FPGA interfaces such as CAPI, are responsible for much of the recent advances in HP computing [3], [4]. Additionally, while the full potential of digital computing has not yet been exhausted as described in the More Moore chapter. Very different approaches such as analog computing with neuromorphic systems and quantum computing are driving toward on the one hand, intelligent decision-making systems, and maximum computational power on the other hand.

The latest manifestation of the Roadmap extends the scope beyond "how to make a smaller transistor" into the realm of "how to make an improved, miniaturized and tailored system." The mutation of the name ITRS-International Technology Roadmap for Semiconductorsto IRDS™—International Roadmap for Devices and Systems-is much more than window dressing. The latest Roadmap structure connects new system requirements to the technology elements needed and their combinations. Again, IRDS™ is expected to bring pre-competitive consensus

across an increasingly more interdisciplinary community (from technologists to designers to quantum and computer scientists) to materialize ground-breaking innovations. Who knows-perhaps in a decade's time we may be writing that "the IRDS™ extrapolation regarding 3D monolithic integration and magnetoresistive neuromorphic synapses was prescient." The IRDS™ has not surrendered its continued role in anticipating the needs of transistors and "classic" wafer-scale semiconductor manufacturing. The new release of the Roadmap still contains chapters on More Moore and Beyond CMOS devices, and Factory Integration, Lithography, Metrology, and Yield, for example. It also emphasizes further the Environmental aspects of semiconductor industry. In addition, IRD-S<sup>™</sup> includes chapters on Application Benchmarking, Systems and Architectures, and Cryogenic and Quantum Computing. It is beyond the scope of this article to summarize the hundreds of pages contained in the IRDS™ just released; the interested reader is encouraged to locate all the documents at https://IRDS.ieee.org/. Here, the intention is to give some highlights and perspectives regarding the activities, challenges and directions of the International Roadmap for Devices and Systems.

Before delving into the newest esoterica, let's examine the vision for 'traditional' logic transistors in the Roadmap, whose characteristics are largely contained in the More Moore chapter. The mainstream device in the 2025 timeframe is expected to be a lateral GAA structure (Fig. 2). In 2028 pitch scaling is expected to stagnate at a 40 nm gate pitch and 16 nm interconnect pitch; 3D constructs are introduced to improve area scaling. Vdd also stagnates, and power density emerges as the primary challenge, along with containment of parasitics. As the scaling is no longer following the pace of the last few decades, a semantics debate is recurrent in the community, regarding the nomenclature for future technology nodes. The team is discussing the use of a suffix of plusses to indicate fractional node implementation. Silicon Germanium is expected to supplant Si as the pFET channel material. Considerable research investment has been made already in those areas, but though these devices are still basically semiconducting CMOS switches supporting the Von Neumann computing paradigm, absorbing so many key inflections will be challenging to the industry. It is important to note that none of the CMOS-compatible switching devices discussed in the Beyond CMOS chapter such as ferroelectric negative-capacitance FETs, TFETs, III-V, and 2D channel materials are explicitly required to meet the scaling and performance goals as defined in this scenario. It is possible that one or more of these devices may find their way into the stream in the out-years, but LGAA and 3D monolithic integration, which are relatively device-agnostic, form the basis for the improvements in the Roadmap. One important open challenge recently reinforced by the More Moore team, is that there is currently no known solution for achieving a steeper sub-threshold slope. TFETs have so far failed to deliver, partly due to inaccurate band-to-band models and predictions. A potential break-

through may though come with the implementation of 2D materials.

In addition, further scaling of on-chip interconnects is seeing a "return to the future," with copper interconnects being likely phased out by higher resistivity materials, though more appropriate to scaled performance and reliability. This may lead to a complete rethinking of interconnect technologies, including the notoriously complex copper damascene approach.

Memory has been, and will continue to be a key driver to the overall scaling and performance of systems. While DRAM and Flash are expected to essentially maintain scaling through these years (there is an anticipated difficult transition to the Vertical Channel Transistor cell architecture for DRAM), there are various options in play for non-volatile memories. All forms basically rely on a permanent, reversible change to the impedance of a link. Phasechange, ferroelectric effect, and filamentary resistance are all current options for the storage element. Each has its own challenges, ReRAM density being one of the key pinchpoints for future scaling.

While the Roadmap continues in its important work of anticipating the technological needs of the mainstream semiconductor industry, the new IRDS™ also considers radically different computing paradigms and the underlying technologies required. The rebooted Roadmap aims at "built for purpose" hardware, as opposed to the old approach of "general purpose" computation systems. This is reflected into two widely different "bookend" approaches to complement classic mobile and High Performance computing addressed in the latest IRDS™. On the one extreme are the cryogenic computers, including Quantum Information Processing.

The complex cooling infrastructure demands centralized location of these computers and they would be directed to high-performance computation, the new IRDS™ Chapter on Cryogenic and Quantum computing addresses

Superconducting electronics, crvogenic application of semiconductors, and the emerging quantum computing. Cryogenic semiconductors have been considered for many years as cooling can improve performance and leakage of silicon-based CMOS, and is needed for cryogenic environments. Superconducting electronics offers the possibility of very low switching energy, even when cooling power is considered. However, today state of the art superconducting chips have fewer than 1 million junctions and many challenges need to be overcome to achieve the 1 billion range to be comparable to today's conventional CMOS chips. Quantum computing is in its infancy as well, with the largest quantum computers sporting fewer than 100 qubits.

Although the landscape of technological contenders in quantum computing is large, challenges abound in fabricating physical qubits, especially in scaling up their number, ensuring and maintaining their coherence for a useful duration of time, in devising an appropriate error correction strategy to produce adequate logical qubits, and overall in enabling quantum information processing to realize its potential over conventional computing. There will be a critical need for developing fault-tolerant computation approaches, and a need for early co-design with quantum software is anticipated. A dedicated working group on Quantum Computing has spun off in 2018 in IRDS™, testimony to the vast and specific challenges of this field.

At the other extreme lies edge, or frontend, distributed computing. This approach promises to be a solution to the computational problems where complex classification and decision making (thus artificial intelligence) need an enormous amount of data transmission back and forth between the logic unit and the memory. Currently, the limited data transmission rates between the different partitions are the bottleneck to the further progress of artificial intelligence in Von

| YEAR OF PRODUCTION                            | 2018            | 2020   | 2022           | 2025             | 2028               | 2031           | 2034           |

|-----------------------------------------------|-----------------|--------|----------------|------------------|--------------------|----------------|----------------|

|                                               | G54M36          | G48M30 | G45M24         | G42M21           | G40M16             | G40M16T2       | G40M16T4       |

| Logic industry "Node Range" Labeling (nm)     | "7"             | "5"    | "3"            | "2.1"            | "1.5"              | "1.5"          | "1.5"          |

| IDM-Foundry node labeling                     | i10-f7          | i7-f5  | i5-f3          | i3-f2.1          | i2.1-f1.5          | i2.1-f1.5      | i2.1-f1.5      |

| Logic device structure options                | finFET<br>FDSOI | finFET | finFET<br>LGAA | LGAA<br>VGAA     | LGAA<br>VGAA       | 3DVLSI<br>VGAA | 3DVLSI<br>VGAA |

|                                               | * 501           | 4      | tere d'appoile | Lateral Manavice | Vertical No-sowing | or Galkiercore | Veta Neodie    |

| Mainstream device for logic                   | finFET          | finFET | finFET         | LGAA             | LGAA               | LGAA           | LGAA           |

| Vdd (V)                                       | 0.75            | 0.70   | 0.70           | 0.65             | 0.65               | 0.60           | 0.60           |

| Gate length (nm)                              | 20              | 18     | 16             | 14               | 12                 | 12             | 12             |

| Number of stacked tiers                       | 1               | 1      | 1              | 1                | 1                  | 2              | 4              |

| Number of stacked devices                     | 1               | 1      | 1              | 3                | 3                  | 4              | 4              |

| Digital block area scaling - node-to-node     | -               | 0.60   | 0.75           | 0.82             | 0.79               | 0.57           | 0.50           |

| Cell height limitation - high-density         | device          | M0     | M0             | M0               | M0                 | MO             | MO             |

| SoC area scalling (stacked) - node-to-node    |                 | 0.70   | 0.79           | 0.84             | 0.83               | 0.60           | 0.60           |

| CPU frequency (GHz)                           | 2.90            | 3.13   | 3.32           | 3.80             | 4.09               | 3.59           | 3.33           |

| Frequency scaling - node-to-node              |                 | 0.08   | 0.06           | 0.15             | 0.08               | -0.12          | -0.07          |

| CPU frequency at constant power density (GHz) | 2.90            | 1.92   | 1.69           | 2.10             | 2.01               | 1.26           | 0.73           |

| Power at iso frequency - node-to-node         |                 | -0.23  | -0.14          | -0.35            | -0.24              | -0.10          | -0.14          |

| Power density - relative                      | 1.00            | 1.64   | 1.96           | 1.81             | 2.04               | 2.86           | 4.53           |

Figure 2 excerpt from IRDS<sup>TM</sup> [5]

Neumann architectures, where logic hardware is separated from memory, making GPUs underutilized. The minimum memory needed for image learning is at least 1GB, and needs very fast access times, with no less than 1 month retention time. New technologies that could ease this bottleneck are going to be carefully considered.

While this will take many forms, including conventional computing enabled by More Moore scaling, some of the most exciting elements of this involve brain-inspired models such as neuromorphic computing hardware. The latter, with all of its different potential approaches, potentially spiking neural networks is expected to become key for Al implementation at the edge, offering a more efficient interaction with the analog world, and in addition, could dramatically reduce computing energy consumption. Vital for image recognition, matrices of tunable elements are programmed based on a learning phase and then used in very rapid analog calculations to identify patterns during the inference operation. Various means of fabricating these artificial synapses are under development, such as ferrolelectric tuning, magnetic

moment manipulation, and modulation of resistance. Networks can also be formed with coupled oscillators, which in some ways more closely mimics brain function, and fabrication of VO<sub>2</sub>-based structures is known, The Beyond CMOS chapter of the IRDS™ contains an extensive assessment of neuromorphic computing technologies and other approaches that are not replacements for CMOS switches, but are rather entirely new means of doing computations.