OCTOBER 2021 VOL. 28, NO. 4 ISSN: 1074 1879

EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI

#### TABLE OF CONTENTS

| * Micro-Transfer Printing Technology Enables     Heterogeneous Integration for 3D ICs     * 2021 IEEE International Memory Workshop                                                                                                                                                      |  |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| UPCOMING TECHNICAL MEETINGS                                                                                                                                                                                                                                                              |  |  |  |  |

| Message from EDS Newsletter Editor-in-Chief     In Memory of T.P. Ma     Letters to the Editor     A Message from Vice President of Publications and Products     A Message from EDS Vice President of Membership and Services     EDS Optoelectronic Devices Technical Committee Report |  |  |  |  |

| AWARDS AND RECOGNITION                                                                                                                                                                                                                                                                   |  |  |  |  |

| YOUNG PROFESSIONALS                                                                                                                                                                                                                                                                      |  |  |  |  |

| WOMEN IN ENGINEERING                                                                                                                                                                                                                                                                     |  |  |  |  |

| CHAPTER NEWS                                                                                                                                                                                                                                                                             |  |  |  |  |

| REGIONAL NEWS                                                                                                                                                                                                                                                                            |  |  |  |  |

| EDS MEETINGS CALENDAR                                                                                                                                                                                                                                                                    |  |  |  |  |

| EDS FIELD OF INTEREST, MISSION AND VISION STATEMENTS                                                                                                                                                                                                                                     |  |  |  |  |

# TECHNICAL BRIEFS

# MICRO-TRANSFER PRINTING TECHNOLOGY ENABLES HETEROGENEOUS INTEGRATION FOR 3D ICS

BOB CONNER, JOHANN WEINHÄNDLER

3D heterogeneous integration of many diverse ultra-thin components improves the power, performance, area, cost, time-to-market, and security of high-performance computing, communications, mobile, automotive, industrial, medical, and defense systems. These diverse components include high electron mobility transistors (HEMTs), heterojunction bipolar transistors (HBTs), power transistors, gate drivers, photonics, sensors, hardware assurance devices, capacitors, inductors, filters, and antennas manufactured using many different process nodes and technologies, including SOI, GaAs, GaN, InP, and SiGe.

Micro-transfer printing (MTP) technology, a patented process developed by X-Celeprint, employs a massively parallel pick-and-place process to stack large arrays of ultra-thin (1–20 micron) diverse components, called x-chips, from one or more separately manufactured wafers on a variety of destination substrates to improve heterogeneous integration to create a 3D IC with the following improvements in:

- Performance—by re-partitioning, disaggregating, and re-integrating by stacking separately manufactured components

- Power—by reducing parasitics and resulting power losses by using ultra short interconnects

- Area—by using the z-dimension for integration rather than growing x- and y-dimensions and producing ultra-thin 3D ICs for embedding in substrates and organic interposers

- Cost—by separately manufacturing each component using the optimal material and technology node, reducing die size,

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at daniel.tomaszewski@imif.lukasiewicz.gov.pl

### **ELECTRON DEVICES** SOCIETY

#### President

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

#### Treasurer

Bin Zhao Freescale Semiconductor Email: bin.zhao@ieee.org

#### Secretary

M.K. Radhakrishnan NanoRel

Email: radhakrishnan@ieee.org

#### Jr. Past President

Fernando Guarin GlobalFoundries Email: fernando.guarin@ieee.org

### Sr. Past President

Samar Saha Prospicient Devices Email: samar@ieee.org

#### Vice President of Education

Navakanta Bhat Indian Institute of Science Email: navakant@gmail.com

#### Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

#### Vice President of Membership and Services

Patrick Fav University of Notre Dame Email: pfay@nd.edu

#### Vice President of Publications and Products

Joachim Burghartz Institute for Microelectronics Stuttgart

Email: burghartz@ims-chips.de

#### Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

#### Vice President of Strategic Directions

Paul Berger The Ohio State University Email: pberger@ieee.org

#### Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullving. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2021                                                                                                                                      | TERM                           | 2022                                                                                                                            | TERM                     | 2023                                                                                                                                              | TERM                                                 |

|-------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| Paul Berger<br>Navakanta Bhat<br>Merlyne De Souz:<br>Kazumari Ishimari<br>William (Bill) Nehrei<br>Murty Polavarapu<br>Camilo Velez Cuerv | a (1)<br>u (1)<br>r (1)<br>(2) | Constantin Bulucea<br>Daniel Camacho<br>John Dallesasse<br>Mario Lanza<br>Geok Ing Ng<br>Claudio Paoloni<br>Hitoshi Wakabayashi | (1)<br>(1)<br>(1)<br>(1) | Roger Booth<br>Xiojun Guo<br>Edmundo A. Gutierrez-D.<br>Francesca Iacopi<br>Benjamin Iniguez<br>P. Susthitha Menon<br>Manoj Saxena<br>Sumant Sood | (2)<br>(1)<br>(2)<br>(1)<br>(2)<br>(1)<br>(2)<br>(2) |

#### NEWSLETTER **EDITORIAL STAFF**

#### **Editor-In-Chief**

Daniel Tomaszewski

Institute of Microelectronics and Photonics Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### Associate Editor-in-Chief

Manoj Saxena

Deen Dayal Upadhyaya College

University of Delhi Email: msaxena@ieee.org

#### REGIONS 1-6, 7 & 9 Eastern, Northeastern & Southeastern USA (Regions 1, 2 & 3)

Rinus Lee

TEL Technology Center, America Email: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University Email: mmadachi@sfu.ca

#### Southwestern & Western USA (Regions 5 & 6)

Muhammad Mustafa Hussain University of California—Berkeley Email: MuhammadMustafa. Hussain@kaust edu sa

#### Latin America North (Region 9)

Joel Molina Reves INAOE

Email: jmolina@inaoep.mx

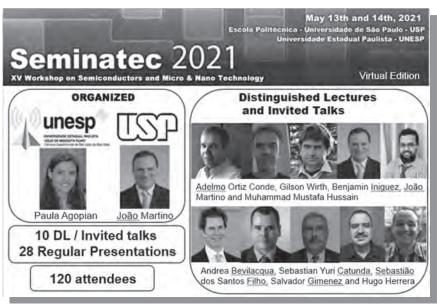

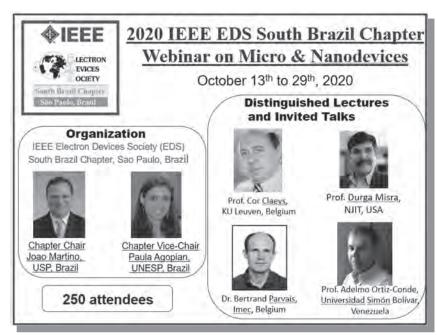

#### Latin America South (Region 9)

Paula Ghedini Der Agopian UNESP. Sao Paulo State University Email: paula.agopian@unesp.br

#### **REGION 8** Eastern Europe

Kateryna Arkhypova **IRE NASU**

Email: arkhykate@ieee.org

#### Scandinavia & Central Europe

Marcin Janicki

Lodz University of Technology Email: janicki@dmcs.pl

#### United Kingdom, Middle East & Africa

Stewart Smith

Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

#### Western Europe

Mike Schwarz Mittelhessen University of **Applied Sciences** Email: mike.schwarz1980@ googlemail.com

#### **REGION 10**

#### Australia, New Zealand & South East Asia

Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University

Email: thhou@mail.nctu.edu.tw

#### South Asia

Soumya Pandit University of Calcutta Email: soumya\_pandit@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission

#### NEWSLETTER DEADLINES

**DUE DATE** ISSUE October July 1st January October 1st January 1st April July April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2021 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

## MICRO-TRANSFER PRINTING TECHNOLOGY ENABLES HETEROGENEOUS INTEGRATION FOR 3D ICS

(continued from page 1)

increasing utilization of expensive semiconductor wafers, using low-cost, massively parallel manufacturing processes and relaxing manufacturing thermal constraints

- Time-to-market—by combining x-chips produced in different fabs and re-using them in multiple designs by stacking them in different configurations to manufacture many different 3D ICs

- **Security**—by integrating multiple hardware authentication and sensor x-chips

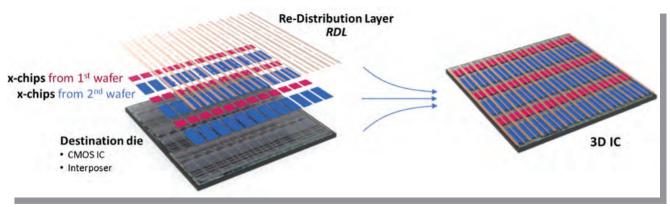

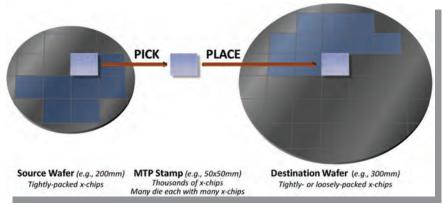

MTP technology supplements other conventional and advanced packaging technologies, providing 3D IC manufacturers with a unique "tool-in-thetoolbox" optimized for heterogeneous integration of large arrays of ultra-thin, diverse components. An MTP-based 3D IC (Figure 1) is manufactured using the following steps: 1) Source wafer fabrication; 2) Destination wafer or substrate fabrication; 3) MTP stamp fabrication; 4) MTP pick-and-place; and 5) Thin film interconnects.

#### 1) Source Wafer

Tightly packed x-chips are fabricated on source wafers made using the optimal process node and technology (such as SOI, GaN, GaAs, InP and

SiGe) for each component. A sacrificial layer is formed underneath the x-chips using different techniques depending upon the source wafer technology, such as:

- For SOI x-chips on silicon wafers with <100> or <111> crystal plane orientation, a standard tetramethylammonium hydroxide (TMAH) or potassium hydroxide (KOH) etch removes the silicon under the x-chips with the oxide beneath the x-chips serving as a barrier against etch of x-chips above.

- For compound semiconductors grown on silicon wafers with <100> or <111> crystal plane orientation, a TMAH etch removes the silicon under the x-chips while not removing the compound semiconductor x-chips.

- For compound semiconductors grown on native substrates, various lattice matched sacrificial layers can be used to undercut the x-chips.

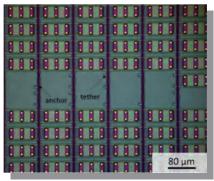

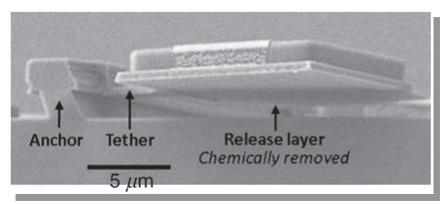

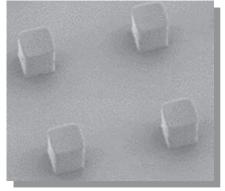

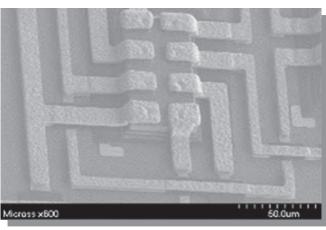

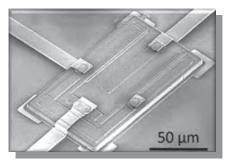

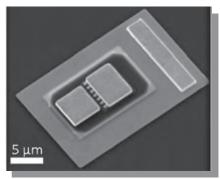

A tether/anchor system (Figures 2 and 3) holds the x-chips aloft after the source wafer is anisotropically etched to remove the sacrificial layer everywhere but underneath the anchor.

#### 2) Destination Substrate

There are many options for the destination substrate, including silicon

Figure 2. X-chips on source wafer after partial x-chip pick-up.

wafers with integrated CMOS ICs, silicon, glass, or ceramic interposer wafers, and large-area glass, ceramic, or plastic panels. The substrate's surface may be planar or non-planar and be smooth or rough.

#### 3) MTP Stamp Fabrication

A low-cost, reusable mold is used to make the MTP stamp (Figure 4) which consists of an array of soft posts composed of a compliant elastomer material, polydimethylsiloxane (PDMS), on a stiff glass substrate. The stamp is stiff in the x-y dimensions, providing high placement accuracy, and compliant in the z-dimension, accommodating non-planar and rough destination

Figure 1. 3D IC made with MTP Technology.

`Figure 3. X-chip after chemical etch.

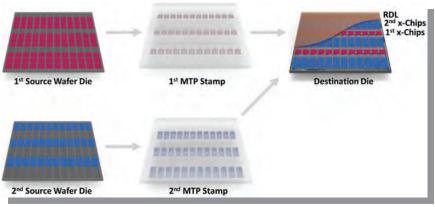

substrates. The post array on the stamp (Figure 5) is customized to match the desired destination substrate locations for massively parallel, selective pick-and-place of thousands of x-chips.

The stamp's posts adhere to the x-chips via van der Waals force. The stamp's viscoelastic behavior uses fast separation speed during pick-up to break the tethers and remove the x-chips, and slow separation speed to place the x-chips on the

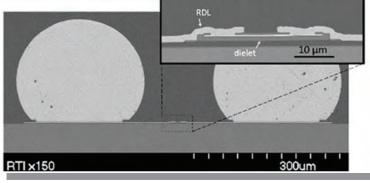

destination substrate. Using a "step and repeat" process, the entire destination substrate is populated with xchips. The stamp can pick-and-place x-chips from smaller to larger wafers (Figure 6) with high wafer utilization, as the stamp readily handles x-chips at the wafer's edge.

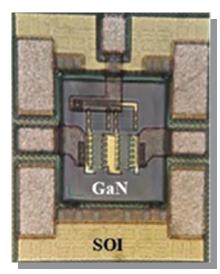

The x-chips may be transferred from multiple source wafers to different locations within the same die on the destination wafer to combine components made using multiple process technologies (Figure 7). By adjusting the pattern and spacing of the small posts on the transfer stamp, the x-chips may be tightly-packed on the source wafer, reducing cost via high wafer utilization, and either tightly- or loosely-packed on the destination wafer.

#### 4) MTP Pick-and-Place

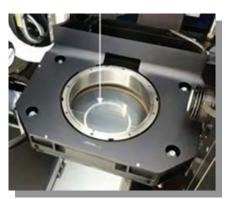

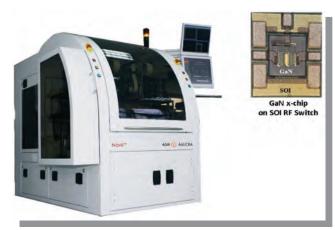

An ultra-high precision pick and place tool developed by AMS Amicra is used to implement MTP technology via a high throughput, fully automatic ISO clean room class 10 system employing a 50 × 50 mm MTP stamp for massively parallel pick-and-place of x-chips from source wafers, which can be up to 300 mm, to destination substrates, which can be up to 300 mm wafers or 450 × 450 mm panels. Placement accuracy is plus-or-minus 1.5-microns

Figure 4. MTP stamp.

Figure 6. Transfer from smaller source wafer to larger destination wafer.

Figure 5. Close-up of MTP stamp's posts.

Figure 7. Single die close-up of transfer from two source wafers to a destination wafer.

Figure 8. High volume MTP manufacturing system developed by AMS Amicra; for details of inset see Fig. 12 caption.

Figure 9. X-chip with RDL top view.

with a 40 second cycle time. Other implementations of the MTP technology include systems with higher placement accuracy (plus-or-minus 0.5-micron) and a low-volume system to serve R&D and specialized manufacturing markets.

#### 5) Thin Film Interconnects

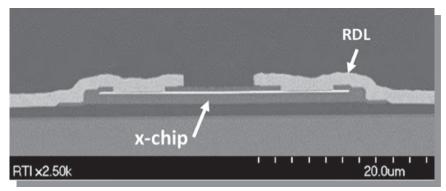

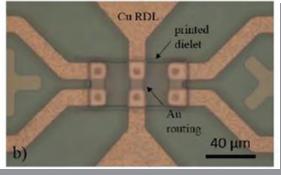

Since the x-chips are ultra-thin (1–20 micron), thin film interconnects may be readily used to connect the

x-chips and destination die, resulting in very short path lengths, since both are active side up. Figures 9 and 10 show the top and cross section views of x-chips interconnected with a copper redistribution layer (RDL). The RDL provides a low electrical and thermal resistance path and enables use of multiple conventional and advanced packaging options.

#### **Examples**

Figure 10. X-chip with RDL cross-section view.

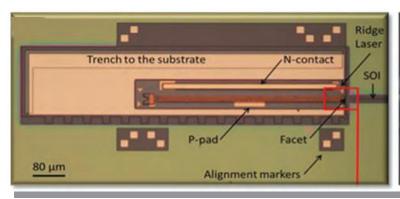

Figures 11–16 show a wide variety of prototypes manufactured using MTP:

Figure 12. Drillet, F., Loraine, J., Saleh, H., ...

U'Ren, G. (2021). RF Small and large signal

characterization of a 3D integrated GaN/

RF-SOI SPST switch. Int. J. Microwave and

Wireless Technol., 13(6), 517-522. doi:10.1017/

S1759078721000076.

Figure 11. Fan-Out Packaging of Microdevices Assembled Using Micro-Transfer Printing (https://doi.org/10.1109/ECTC.2016.269).

Figure 13. Integration of GaN HEMTs onto Silicon CMOS by Micro Transfer Printing (https://doi.org/10.1109/ ISPSD.2016.7520875).

Figure 14. Mathews, I., Quinn, D., Justice, J., ... Corbett, B., Microtransfer Printing High-Efficiency GaAs Photovoltaic Cells onto Silicon for Wireless Power Applications. Adv. Mater. Technol. 2020, 5, 2000048. https://doi.org/10.1002/admt.202000048. Copyright Wiley-VCH GmbH. Reproduced with permission.

Figure 15. Microtransfer-Printed InGaAs/ InP HBTs Utilizing a Vertical Metal Sub-Collector Contact (https://doi.org/10.1109/ DRC46940.2019.9046426).

Figure 16. Edge-coupling of O-band InP etched-facet lasers to polymer waveguides on SOI by micro-transfer-printing (https://doi.org/10.1109/JQE.2019.2958365).

#### About the Authors

Bob Conner is VP of Business Development at X-Celeprint. Previously, he was CEO of Sarda Technologies and Symmor-

phix. Bob has held VP positions at Semprius, Nextreme, and Cirrus

Logic and worked for Applied Materials, Intel, and GE. Bob earned his MBA at University of Chicago and BSME at Duke University.

Dr. Johann Weinhändler is Managing Director at ASM AMI-CRA. Previously, he has held different management positions at Oerlikon Systems, Datacon/ Besi, and Lam Research.

Johann earned his Ph.D at the Trinity Colleges Dublin and an MBA from the Open University Business School in the UK.

# 2021 IEEE International Memory Workshop (IMW)

The Thirteenth IEEE International Memory Workshop (IMW) was held as a virtual event from 16-19 May 2021, due to the outbreak of COVID-19. The IMW is sponsored by the IEEE Electron Devices Society and meets annually in May. The workshop is a unique forum for specialists in all aspects of semiconductor memories (non-volatile & volatile). The target audience covers specialists from different areas of microelectronics and people with different backgrounds who wish to gain a better understanding of the field. More than 280 people took part in our virtual meeting this vear. The technical sessions were organized in a manner of presentations and live Q&A that provided ample time for informal exchanges amongst presenters and attendees.

This year's program included a oneday short course chaired by Srivardhan Gowda from Intel and Tomoya Sanuki from Kioxia, with lectures on the New computing paradigms with memories and 3D memories-beyond Flash.

The single-track conference spanned three days, including a couple of invited talks given by experts in the memory field-X. Xu (Chinese Academy of Sciences), J. Okuno (Sony), D.H. Kim (Samsung), F. Schanovsky (GlobalTCAD Solutions), and J. J. Sun (Everspin)-providing an exciting overview of the main trends for memory technologies and applications. The IMW is also an excellent forum to present new and original technical works. This year's technical program comprised 28 excellent papers selected by the technical committee among more than 50 papers submitted and covering the major categories of memory technologies (NAND, DRAM, SRAM, ReRAM, FeRAM, MRAM, emerging technologies) and applications (Automotive, In memory computing). Among the most exciting news presented at the conference were, an

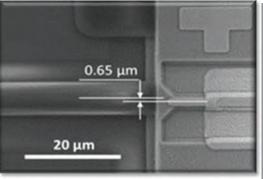

Embedded ReRAM compatible with 28 nm FDSOI technology (after: L. Grenouillet, et al., "16kbit 1T1R OxRAM arrays embedded in 28 nm FDSOI technology demonstrating low BER, high endurance, and compatibility with core logic transistors", DOI: 10.1109/IMW51353.2021.9439607).

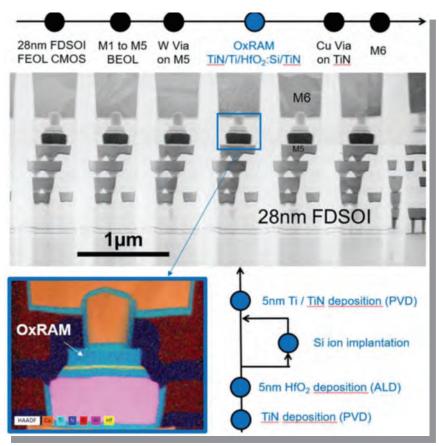

Draft and cross-sectional view of 3D FE-FET with trench architecture (after: K.Banerjee, et al., "First demonstration of ferroelectric Si:HfO2 based 3D FE-FET with trench architecture for dense nonvolatile memory application", DOI: 10.1109/IMW51353.2021.9439620).

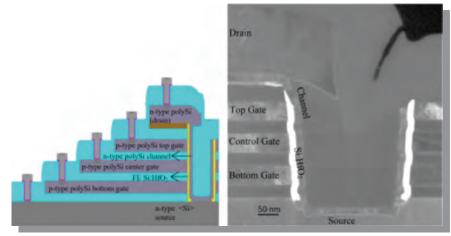

Draft and cross-sectional view of 3D AND-type flash memory cell (after: H.-T. Lue, et al., "Write-In-Place Operation and It's Advantages to Upgrade the 3D AND-type Flash Memory Performances," DOI: 10.1109/IMW51353.2021.9439621).

embedded ReRAM array compatible with 28 nm FDSOI technology, a 3D FE-FET with trench architecture for dense nonvolatile memory application, a 3D AND-type flash memory with the inplace page write time around 110 usec.

The next IMW will be held in May 2022 in Dresden, Germany. For more details on the IMW conference please visit the IMW website (http://www.ewh.ieee.org/soc/eds/ imw/). IMW technical proceedings are available on the IEEE Xplore database https://ieeexplore.ieee.org/xpl/ conhome/9439548/proceeding.

> Zhiqiang Wei 2021 IMW Publicity Chair Avalanche

# UPCOMING TECHNICAL MEETINGS

# 2021 IEEE INTERNATIONAL ELECTRON DEVICES MEETING HIGHLIGHTS EDUCATIONAL OPPORTUNITIES IN LEADING-EDGE SEMICONDUCTOR TECHNOLOGIES

At IEDM each year, the world's best scientists and engineers in nano/ microelectronics gather to participate in a technical program consisting of more than 220 presentations, along with a variety of panels, focus sessions, Tutorials, Short Courses, a supplier exhibit, IEEE/EDS award presentations and other events highlighting leading work in more areas of the field than any other conference. The 67th IEDM is scheduled for 11-15 December 2021, under the theme "Devices for a New Era of Electronics: From 2D Materials to 3D Architectures."

While the comprehensive technical program for the 2021 IEEE International Electron Devices Meeting (IEDM) will be finalized soon, the popular IEDM Tutorials and Short Courses are already set. The broad reach, interdisciplinary nature and technical depth of the topics that will be discussed in these educational events can serve as a "crystal ball" of sorts to show where the industry is headed. For those who wish to get a jump on learning about the 67th IEDM, this news release provides descriptions of these educational offerings.

"As the COVID-19 pandemic has demonstrated, the world is becoming increasingly reliant on electronic technologies. The good news is that the IEDM Tutorials and Short Courses will provide attendees with the invaluable knowledge and information needed to advance the state-of-theart in critical areas of the field," said Meng-Fan (Marvin) Chang, IEDM 2021 Publicity Chair, IEEE Fellow, Distinguished Professor of Electrical Engineering at National Tsing Hua

University, and Director of Corporate Research at TSMC. "The opportunity to engage with the world's technical leaders in these highly specialized areas is one of the hallmarks of the IEDM conference."

"New, fast-growing electronics applications often require novel semiconductor solutions," said Srabanti Chowdhury, IEDM 2021 Publicity Vice Chair and Associate Professor of Electrical Engineering at Stanford University. "The IEDM Tutorials and Short Courses represent a great opportunity to explore evolving areas of the field, with topics that include novel materials and device types; advances in process and packaging technologies; new design approaches; and much more."

#### IEDM Tutorials — Saturday, December 11

Now in their 12th year, the 90-minute Saturday tutorial sessions on emerging technologies and specialized topics have become a hugely popular part of IEDM. They are presented by experts in the respective areas, the goal being to bridge the gap between textbook-level knowledge and leading-edge current research. The topics for 2021 are:

#### 2:45 p.m.-4:15 p.m.

Beyond the FinFET Era: Challenges and Opportunities for CMOS Technology, Kai Zhao, IBM

- TCAD-Based DTCO and STCO, Asen Asenov, University of Glasgow

- 6G Technology Challenges from Devices to Wireless Systems, Aarno Pärssinen, Oulu University

#### 4:30 p.m.-6:00 p.m.

- Selective and Atomic-Scale Processes for Advanced Semiconductor Manufacturing, Robert Clark, TEL

- Machine Learning for Semiconductor Device and Circuit Modeling, Elyse Rosenbaum, University of Illinois, Urbana-Champaign

- GaN Power Device Technology and Reliability, Dong Seup Lee, Texas Instruments

#### IEDM Short Courses—Sunday, December 12

In contrast to the Tutorials, the fullday IEDM Sunday Short Courses are focused on a single technical topic. Early registration is recommended, as they are often sold out. They offer the opportunity to learn about important areas and developments, and to network with global experts.

- Future Scaling and Integration Technology, organized by Dechao Guo, IBM Research

- Processes and Materials Engineering Innovations for Advanced Logic Transistor Scaling, Benjamin Colombeau, **Applied Materials**

- Interconnect Resistivity: New Materials, Daniel Gall, Rensselaer Polytechnic Institute

- Metrology and Material Characterization for the Era of 3D Logic and Memory, Roy Koret, Nova Ltd.

- Beyond FinFET Devices: GAA, CFET, 2D Material FET, Chung-Hsun Lin, Intel

- Heterogeneous Integration

Using Chiplets & Advanced

Packaging, Madhavan Swaminathan, Georgia Tech

- Design-Technology Co-Optimization/System-Technology Co-Optimization, Victor Moroz, Synopsys

- Emerging Technologies for Low-Power Edge Computing, organized by Huaqiang Wu, Tsinghua University and John Paul Strachan, Forschungszentrum Jülich

- Mobile NPUs for Intelligent Human/Computer Interaction, Hoi-Jun Yoo, KAIST

- Brain-Inspired Strategies for Optimizing the Design of Neuromorphic Sensory-Processing

- Systems, Giacomo Indiveri, University of Zurich

- Memory-Based Al & Data Analytics Solutions, Euicheol Lim, SK hynix

- Material Strategies for Memristor-Based AI Hardware and their Heterointegration, Jeehwan Kim, MIT

- RRAM Devices for Data Storage and In-Memory Computing, Wei Lu, University of Michigan

- Practical Implementation of Wireless PowerTransfer, Hubregt Visser, IMEC

# Vendor Exhibition/Poster Sessions

A vendor exhibition will be held once again in conjunction with the technical program.

#### **Further information about IEDM**

For registration and other information, visit www.ieee-iedm.org.

#### Follow IEDM via social media

- Twitter: www.ieee-iedm.org/twitter

- LinkedIn: www.ieee-iedm.org/ linkedin

- Facebook: www.ieee-iedm.org/ facebook

Gary Dagastine Dagastine & Co. PR gdagastine@nycap.rr.com

Chris Burke BtB Marketing Communications chris.burke@btbmarketing.com

# 23rd International Vacuum Electronics Conference (IVEC 2022)

On behalf of the IVEC 2022 Organizing Committee, we are pleased to announce that the Twenty-Third International Vacuum Electronics Conference (IVEC) will be held in Monterey, California, from 25–28 April 2022. In addition to the traditional in-person conference format, virtual access will be available for presenters and attendees who cannot travel to Monterey.

Plenary talks will provide insights into the history, emerging technology, and future directions of vacuum electronics. The conference will include invited and contributed papers and posters on topics ranging from the fundamental physics of electron emission and modulated electron beams to the design and operation of advanced devices at UHF to THz frequencies. In addition, presentations on the development of computational tools for vacuum electron device (VED) design,

supporting technologies, and VED-based systems will be made. IVEC provides a unique snapshot of the current state-of-the-art of VEDs, devices that continue to produce unmatched power and performance at frequencies up to and including the THz band.

A one-day minicourse, with tutorials offered by international vacuum electronics experts, will be held on 25 April 2022. The mini-course will also be accessible to remote participants. The John R. Pierce Award for Excellence in Vacuum Electronics, the

Vacuum Electronics Young Scientist Award, and a Student Paper Award will be presented at the conference.

The most up-to-date information about the conference can be found at ieeeivec.org.

We invite you to submit papers on your work and experiences in vacuum electronics and electron sources, and we hope to see you all in Monterey or online for IVEC 2022.

> Jack Tucek 2022 IVEC General Chair

### IEEE INTERNATIONAL RELIABILITY Physics Symposium 2022

The IEEE International Reliability Physics Symposium (IRPS) is the world's premier forum for leadingedge research addressing developments in the Reliability Physics of devices, materials, circuits, and products used in the electronics industry. IRPS is the conference where emerging reliability physics challenges and practical solutions to achieve realistic end-of-life projections and mitigation are first discussed.

In 2022, the IRPS will be held 27-31 March at the Hilton, Dallas, Texas. Over the course of the conference, IRPS will offer a blended mix of keynote talks, tutorials, year-in-reviews, workshops, vendor exhibits, and technical presentations. Abstracts are due by 23 October 2021. Late breaking news submissions are welcome by 23 January 2022.

The IRPS draws presentations and attendees from industry, academia and governmental agencies worldwide. No other meeting presents as much leading work in so many different areas of reliability of electronic devices, encompassing silicon device, non-silicon device, process technology, nanotechnology, optoelectronics, photovoltaic, MEMS technology, circuits and systems reliability including packaging. IRPS 2022 is soliciting increased participation in the following areas: Circuit Reliability and Aging, Reliability of RF/ mmW/5G Devices, System Electronics Reliability, and Neuromorphic Computing Specific Reliability Issues.

IRPS 2022 will be kicked off by keynote presentations from reliability experts at Intel, Synopsys, Micron, and TSMC, covering the latest reliability trends and mitigation approaches from various industry perspectives.

Further opportunities at the symposium include:

• Tutorial Program. The IRPS tutorial program is a comprehensive event designed to help both the new engineers and experienced

Mohsen Alavi Corporate VP and GM of Quality & Reliability, Intel

Shankar Krishnamoorthy GM, Digital Design Group, Corporate Staff, Synopsys

Nagasubramaniyan Chandrasekaran Senior VP, Technology Development, Micron

Jun He VP Corporate Quality & Reliability, TSMC

- researchers. The program contains both beginner and expert tracks and is broken down into topic areas that allow the attendee to participate in tutorials relevant to their work with minimal conflicts between subject areas.

- Year-in-Review Session. These seminars provide a summary of the most significant developments in the reliability community over the past year. This serves as a convenient, single-source of information for attendees to keep current with the recent reliability literature. Industry and academic experts serve as the "tour guides" and save you time by collecting and summarizing this information to bring you up to date in a particular area as efficiently as possible.

- Poster Reception. The poster session provides an additional opportunity for authors to present their original research. The setting is informal and allows for easy discussion between authors and other attendees.

- Workshops. These workshops enhance the symposium by providing the attendees an opportunity to meet in informal groups to discuss key reliability physics topics with the guidance of experienced moderators. Some of the workshop topics are directly coupled to the technical program to provide a venue for more discussion on the topic.

- Vendor Exhibits. Held in parallel with the technical sessions, the equipment demonstrations provide a forum for manufacturers of state-of-the-art laboratory equipment to present their products. Attendees are encouraged to visit the manufacturers' booths for information and demonstrations.

- IRPS Paper Awards. IRPS bestows awards for Best Paper, Best Student Paper, Best Posters, and People's Choice.

- **IEW Co-Location**. This year the IRPS will be co-located with the International ESD Workshop (IEW). Now in its 16th year, the IEW provides a relaxed, invigorating atmosphere to present new work and engage in discussions about the latest issues confronting the ElectroStatic Discharge (ESD) and Electrostatic OverStress (EOS) communities.

For the call for papers and other information, visit the IRPS 2022 home page at www.irps.org or join the IRPS linked-in group.

The IRPS committee members look forward to seeing you in Dallas, Texas!

> Charlie Slayman 2022 IRPS General Chair Cisco Systems

Chris Kim 2022 IRPS Publicity Chair University of Minnesota

# SOCIETY NEWS

#### MESSAGE FROM EDS NEWSLETTER EDITOR-IN-CHIEF

Daniel Tomaszewski FDS Newsletter Editor-in-Chief

Dear Readers, Members of the IEEE EDS Community, Welcome to the IEEE EDS Newsletter issue October 2021. I am very glad to introduce this issue to you.

First, I would like to draw your attention to the Tribute to Prof. T.P. Ma who passed away on 6 April 2021.

In the Technical Briefs section we continue the presentation of articles on emerging technologies and devices, which, I believe, may be of interest to you. This time you can read an interesting material introducing the Micro-Transfer Printing (MTP) technology, which employs a massively parallel pick-and-place process to stack large arrays of ultra-thin (1-20 micron) diverse components from one or more separately manufactured wafers on a variety of destination substrates to improve heterogeneous integration to create 3D ICs. Except for the material on MTP, we also present a brief report on 2021 IEEE International Memory Workshop (IMW).

In this issue we share with you further details of the IEDM 2021 program and announce two technical conferences that will be held next year, namely IRPS 2022, and IVEC 2022.

In the sections EDS Women in Engineering (EDS WiE) and EDS Young Professionals (EDS YP) we continue to present outstanding female researchers. I believe that their impressive achievements in different domains, and their thoughts and suggestions may be inspiring, in particular to the young members of EDS. In this issue the WiE section includes two articles presenting Prof. Elyse Rosenbaum and Prof. Deblina Sarkar, whereas the YP section includes excerpts of the interview that Manoj Saxena made with Dr. Pragya Kushwaha.

The Regional News and Chapter News sections bring information about continuous daily activities of numerous EDS chapters from most of the parts of Regions 8, 9, 10. I deeply appreciate the efforts of all those chapters that delivered materials for the issue. It is worth mentioning that the Chapter News section includes this time four articles concerning two aspects: a help of EDS members and student-members to communities touched by COVID-19 pandemic, and efforts of researchers and engineers involved in the state of the art technologies, to cope with a progressing climate destruction and its effects. Undoubtedly, these plagues are great threats for our ecosystem.

Dear Readers, in May and June, 2021 we carried out a series of four WebEx meetings with the Regional Editors responsible for the Newsletter cooperation with different Regions. Therefore, the Vice President of Regions & Chapters, representatives

of the Regions & Chapters Committee and Subcommittee for Regions & Chapters were also present. The meetings were organized by Joyce Lombardini, who coordinates the Editorial Team work. A goal of the meetings was to get to know each other better, recognize the needs of the Editors, answer their questions, and share with them expectations concerning both cooperation with the assigned chapters and cooperation with the Editor-in-Chief, Associate Editor-in-Chief, and the Team coordinator. I believe that the meetings were fruitful. We were able to discuss and improve recommendations for the Editorial Team, in particular for the Regional Editors. I am very grateful to them for their efforts. I am happy that the recently appointed Regional Editors do also an excellent job.

Dear Readers, if you have any suggestions, comments regarding the Newsletter contents, please do not hesitate to contact me or Manoi Saxena. We will be very glad to receive your feedback. As you can see, in this issue a rubric Letters to the Editor has appeared. Your questions and our answers will be presented there.

Finally, I would like to express again my thanks to all the article Authors and to all the members of the Editorial Team. I hope that the Readers will find the issue interesting.

> Sincerely, Daniel Tomaszewski

### IN MEMORY OF PROF. T.P. MA

By Mukesh Khare, Huiming Bu, Dechao Guo, and Terry Hook, IBM Research

Tso-Ping (T.P.) Ma, the Raymond J. Wean Professor of Electrical Engineering and Applied Physics at Yale University for 44 years, passed away peacefully on April 6, 2021, at the age of 75, after a brief illness. He left behind his wife of 49 years, Dr. Pin-Fang Ma, his children Mahau Ma and Jasmine Ma, and a legacy of mentoring countless students, of which many have become prominent and groundbreaking leaders in the semiconductor industry. Although Ma spent a relatively short time at IBM, his former Yale students make up a talented and appreciative cohort within IBM Research.

Terry Hook, Senior Technologist at IBM, fondly recalls a time at Yale when he accidentally spent more than \$20,000 in computer time in one month. "I don't know how they solved that problem, but TP shielded me from the consequences. He forever loved that story and enjoyed roasting me when we encountered one another at conferences around the world in the following years. He even defined a new metric of computer usage: one "Hook" is \$20,000 worth of CPU time."

Ma was born on November 13, 1945, in Lanzhou, China and graduated from National Taiwan University in 1968. He completed his Ph.D. degree at Yale University in 1974, then joined IBM for a few years before returning to Yale as a faculty member in 1977. He focused his research and teaching on semiconductors, CMOS technology, and nanoelectronics, and over the years received numerous awards and honorary degrees for his achievements, including election to the US National Academy of Engineering, a Foreign Member of the Chinese Academy of

Prof. Tso-Ping Ma (November 13, 1945-April 6, 2021)

Sciences, an Academician of the Academia Sinica in Taiwan, and a life Fellow of the Institute for Electrical and Electronic Engineering (IEEE). He also received the 2008 Connecticut Medal of Technology, the 2006 Semiconductor Industry Association University Researcher Award, the 2005 IEEE Andrew S. Grove Award, and a 2005 Pan Wen-Yuan Research Award.

One notable story from his time at IBM was recounted by Huiming Bu, Vice President Semiconductor Technology Research and Director Albany Lab. "Ma and one of his IBM colleagues discovered the ionizing radiation effects in MOS devices, after failing many times to cure defects by trying all kinds of furnace annealing techniques. One day he decided to put the silicon wafer in a microwave, and surprisingly it worked. "Of course, nowadays you can't put a 12" wafer in a microwave as the size doesn't fit." Ma would add."

Ma was an internationally recognized pioneer for his contributions to semiconductor science and technology-in particular, breakthroughs in advanced gate dielectrics, which paved the path for high-k dielectrics and extended the scaling of CMOS technology. His research also generated fundamental and lasting impacts on many other applied physics fields, notably ferroelectrics and ionizing radiation sciences.

"As the father of high-k gate dielectrics, Professor T.P Ma will be deeply remembered as an influencer, a mentor, and a friend by the semiconductor world", said Dechao Guo, Director Advanced Logic Technology Research. "At conferences, workshops and seminars, Ma was always surrounded by friends from the industry and academia. People always enjoyed interactions with him, for his view on technology, his stories of the semiconductor industry, his sense of humor, and his inspiring advice."

Mukesh Khare, Vice President of Semiconductor, Systems, and Cloud, credits Ma with "inspiring me to take challenges, and coaching me all the way to the finish line, with his trademark humility and humor. He would take students to "Naples Pizza" to celebrate every occasion, and I would attempt to speak in a Chinese dialect. This became a tradition, and TP would burst out laughing every time. "Nǐ yǒngyuǎn shì wǒ xīnzhōng de yīngxióng" (You will always be my hero)."

For many of us who had the opportunity to interact with him in person, Ma was a scholar with a sharp mind, a mentor with great wisdom, and a person with a kind heart. He will be dearly missed by the semiconductor community, and all who benefitted from his humanity.

#### LETTERS TO THE EDITOR

Dear Dr. Tomaszewski,

I was reading the Technical Briefs: Beyond CMOS, and I was wondering why technology, devices and circuits for THz electronics (>100 GHz) were not even mentioned (this part felt during the IRTS in the More than Moore section). Is this topic out of scope within the International Roadmap for Devices and Systems (IRDS)?

With kind regards Thomas Zimmer (University Bordeaux) Dear Prof. Thomas Zimmer,

I am very glad that the recent article in the series based on IRDS International Focus Team (IFT) reports has drawn your attention and triggered your comment with some criticism.

The THz electronics topic appeared in two IRDS IFT reports, namely "Cryogenic Electronics and Quantum Information Processing" (e.g. for astronomy applications), and "Outside System Connectivity" (for communication at very high frequencies).

It is the intention of the IRDS teams led by Dr. Paolo Gargini to present all their reports in the Newsletter. The EDS Newsletter team is also very interested in introducing IRDS reports to the EDS community. So, I believe you will be able to read Technical Briefs including THz electronics in the future Newsletter issues.

With kind regards, Daniel Tomaszewski (Newsletter EiC)

# A Message from Vice President of Publications and Products

Dear Fellow EDS Members:

Joachim N. Burhartz EDS Vice President of Publications and Products

It is my great pleasure to update you on the status and the ongoing activities around our EDS publications. Our flagship journals, the IEEE Transactions on Electron Devices (T-ED), the IEEE Electron

Devices Letters (ED-L), and the IEEE Journal of the Electron Devices Society (J-EDS), continue to do very well under the outstanding leadership of the respective Editor-in-Chiefs (EiCs), Giovanni Ghione for T-ED, Jesus del Alamo for ED-L and Enrico Sangiorgi for J-EDS. ED-L has been steadily increasing its impact factor to 4.187 now (5-year average is 3.967), and T-ED and J-EDS have maintained their impact factors of 2.9 and 2.5, respectively. The real strength of our flagship journals, however, are their superior turn-around times, which are a great value to authors.

ED-L, aiming particularly at rapid publication of letters, forwards accepted manuscripts to ePublication after only 3.9 weeks from submission, while T-ED and J-EDS have constant figures of 13.4 and 11.8 weeks, respectively, which are well in line with their 5-year averages. Our publications also perform very well in terms of usage. When considering PDF downloads and HTML views in Xplore, ED-L, T-ED and J-EDS are ranking at positions 24, 10, and 102, respectively, out of 383 IEEE publications overall (2019 figures).

Also, our co-sponsored journals do very well, having ranks between 28 and 125. In cases where the journal's performance declined during past years, though the scope and industrial relevance is high, we started new initiatives. This applies to the Transactions on Display Technology (T-DT) which are intended to succeed the Journal of Display Technology (J-DT), formerly owned by the Photonics Society. An LOI has been approved by the EDS Board of Governors (BoG) and was submitted re-

cently. Launching a co-sponsored publication can be a major effort, as seen with the new IEEE Journal on Flexible Electronics (J-FLEX). It took more than two years of planning, negotiations and approval by the IEEE Periodicals Review and Advisory Committee (PRAC) to finally launch this new and very timely publication which is co-sponsored by EDS, the Sensors Council (SC), and the Circuits and Systems Society (CAS). The two founding editors are Ravinder Dahiya from SC and Paul Berger from EDS; the journal's steering committee is chaired by Sandro Carrara from CAS. We are now looking forward to a highly successful new journal that can well be associated with the two IEEE conferences IFETC and FLEPS.

Another topic that currently receives a lot of our attention is the consideration of an EDS Magazine. Numerous IEEE societies offer such magazines to their members as a society benefit, meaning that electronic subscription is free to them and that printed copies can be purchased

with a substantial discount. Some societies offer both a magazine and a newsletter, while others prefer to merge those contents into a magazine only. Yet quite a few societies just offer a newsletter, such as we do at EDS. Our newsletter has emerged from a communication media to a publication that is enriched by technical articles and historical reviews, such as the series on 'marvels of microelectronic engineering' from July 2018 through January 2020. The key difference between a newsletter and a magazine is that a magazine is to be treated as an IEEE publication with access through Xplore, while a newsletter is owned by the society. That means that a magazine can achieve an impact factor due to technical and review articles published. In some cases, IEEE magazines have reached impact factors beyond 10. A magazine also offers opportunities to publish articles of practical value to industry, articles about celebrated society members, and on many more topics that are not covered by our flagship publications or by our newsletter. It should be pointed out that the new EDS Magazine should not be compared to the former Circuit & Devices Magazine which was co-sponsored by the IEEE societies EDS, CAS, LEOS, and CPMT. This was a magazine of IEEE Division-I rather than a society magazine as we target now. The current plan is to take the steps towards launching the EDS Magazine, which has been approved by BoG and will be prepared for PRAC approval, in coexistence with our successful EDS Newsletter. This will be a major effort but we will look

forward to providing the EDS Magazine as a benefit to our existing members and help attracting other IEEE members to join EDS.

Finally, I want to take the opportunity to thank the Editors-in-Chief of our flagship journals and of our co-sponsored publications, as well as the associate editors and peer reviewers involved, for their outstanding service to our society. I would like to acknowledge the EDS staff and the IEEE publications staff for their excellent support.

I would very much welcome comments and suggestions related to our EDS publications.

Joachim N. Burghartz **EDS Vice President of Publications** and Products e-mail: burghartz@ims-chips.de

## Message from EDS VICE President OF MEMBERSHIP AND SERVICES

Patrick Fay EDS Vice President of Membership and Services

As I write this, we are more than a year into the pandemic and many aspects of our lives-both personal and professional-have been disrupted in many ways. It is my sincere hope

that the members of our "EDS family" find the support and care they need to persevere in challenging times. While of course the health and safety of all our members and their families, friends, and colleagues are at the forefront of our thoughts, EDS members have continued to work to advance the state of the art in electron devices through research and industrial efforts. In that same spirit, EDS members and volunteers have also ramped up their efforts to continue to serve you, our members, despite the challenges we collectively face. Recognizing that some of our traditional venues for education and interaction have been disrupted, EDS has significantly expanded our educational webinar series (https:// eds.ieee.org/education/webinars). Featuring a wide range of topics of interest to EDS members and presented by leading practitioners and researchers, these webinars offer our members unique educational opportunities. Our podcast series (https:// eds.ieee.org/education/podcasts) is another excellent way to gain insights and perspective from leaders in the electron devices field. While we all look forward to the time when we can resume in-person conferences, symposia, and workshops, in the interim EDS members and volunteers have made tremendous efforts to host high-quality conferences; while the circumstances have required that these be hosted on-line or in hybrid

formats, they continue to provide opportunities for networking, learning, and stimulating new ideas for participants. I encourage everyone to check out EDS's social media feeds (Facebook, Twitter, LinkedIn, and Instagram) for the latest news, opportunities, and initiatives.

Speaking of new initiatives, I would like to call your attention to two new programs that may be of interest. For students, the "EDS Awarded Student Membership" program is designed to recognize students that contribute to the IEEE and EDS missions. Students involved/engaged in EDS activities, and studying topics within the EDS areas of interest, can be nominated for these awards. I encourage you to nominate worthy candidates for these recognitions; the details can be found online (https://eds.ieee.org/members/eds -awarded-student-membershipprogram). A second initiative focuses

on supporting our chapters to grow, try new things, and flourish. This "EDS Special Membership Growth" program is intended to fund new, experimental activities by groups or chapters that will help to enhance the participation of students, young professionals, women, and under-represented communities (i.e., ethnic, social, or economic groups that are under-represented in EDS membership). These can be one-time or multiyear initiatives but must be creative and new ideas that can expand the appeal of EDS and help our society grow. The details are available online (https://eds.ieee.org/members/ eds-chapter-membership-growth -program). Finally, while not a new initiative, I would like to encourage eligible members to consider applying for Senior Member status. If you have been in professional practice for 10 years or more (including credit for college-level education), you may be eligible. Senior member status is the highest grade of membership for

which an individual can apply and is a mark of distinction that is widely recognized professionally. EDS chapters may also wish to coordinate Senior Member recruiting events to strengthen their local chapter profile. Please see https://eds.ieee.org/members/eds-senior-member-program for full program details.

Finally, I'd like to take this opportunity to note that since our goal as a society is to serve you, our members, I hope you will let me, or other members of the membership committee know if you have thoughts or ideas that would improve the value of the society for you. EDS is wellestablished and very active in providing high-quality publication venues (including Electron Device Letters, Transactions on Electron Devices, the Journal of the Electron Devices Society, Transactions on Semiconductor Manufacturing, the Journal of Microelectromechanical Systems, Transactions on Device and Materials Reliability, and the Journal of Photovoltaics), as well as premier electrondevice focused technical conferences, educational opportunities such as the distinguished lecture series and webinars, and outreach and service opportunities. But we are very interested in expanding the services and benefits that we can provide to our members, and we very much value any suggestions you have. The current membership committee consists of Shuji Ikeda, Benjamin Iniguez, Carmen Lilley, Durga Misra, Angele H. M. E. Reinders, Mike Schwarz, and Bin Zhao. I hope you will pass along your thoughts or suggestions directly to me or to any of us on the committee (https://eds.ieee.org/about-eds/ governance/standing-committees/ membership-committee).

Patrick Fay

EDS Vice President of Membership

and Services

University of Notre Dame

Indiana, USA

e-mail: pfay@nd.edu

# EDS OPTOELECTRONIC DEVICES TECHNICAL COMMITTEE REPORT

Can Bayram Chair of the EDS Optoelectronic Devices Committee

Optoelectronic

Devices Technical

Committee serves

the society in the

areas of light and

light—matter interactions through

organizing webinars, creating

special invited issues in the EDS

journals, and con-

tributing to the conferences through organizing special sessions. In the wake of the COVID-19 pandemic, we witnessed increased responsibilities in teaching, research, and at home. The TC continues to support the IEEE and EDS Missions through newsletter contributions and webinar organizations. Recent topics covered include photovoltaics, opto-electromechanics, detectors, and emitters and (recently archived 7+) webinars are available for viewing at your convenience. On a path towards (re) normalization, the TC will benefit from the pandemic era learning and continue to build its online content as traditional in-person engagement

mechanisms are being (re)vitalized. Recent needs in photonic disinfection and the continuous goal of going carbon-neutral reassures the value of fundamental and applied research in optoelectronics to enable energy-efficient and scalable solutions to the grand challenges in energy, communication, and health.

Can Bayram Chair of the EDS Optoelectronic Devices Committee e-mail: cbayram@illinois.edu

#### AWARDS & RECOGNITIONS

#### 2020 EDS GEORGE E. SMITH AWARD

A high priority of the IEEE Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. The George E. Smith Award was established in 2002 to recognize the best paper appearing in a fast turnaround archival publication of EDS, targeted to the IEEE Electron Device Letters. Among other criteria including technical excellence, an important metric for selection for the Award is comprehensive and impartial referencing of prior art.

The paper winning the 2020 George E. Smith Award was selected from over 420 articles that were published in 2020. The paper is entitled, "Theoretical Limit of Low Temperature Subthreshold Swing in Field-Effect Transistors." This paper appeared in the February 2020 issue of the IEEE Electron Device Letters and authored by Arnout Beckers, Farzan Jazaeri and Christian C. Enz.

The Award will be presented during the IEEE International Electron Devices Meeting to be held in December 2021. In addition to the Award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the IEEE Electron Devices Society, I would like to congratulate the authors for this achievement.

Joachim Burghartz EDS Vice-President of Publications and Products

#### 2020 EDS PAUL RAPPAPORT AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. Every year, the Society confers its prestigious Paul Rappaport Award to the best paper published in the *IEEETransactions on Electron Devices*. Among other criteria including technical excellence, an important metric for selection for the Award is comprehensive and impartial referencing of prior art.

The winning paper was selected from over 850 articles that were published in 2020. The winning paper is entitled "Improved Air Spacer for Highly Scaled CMOS Technology". This paper was published in the December 2020 issue of the IEEE Transactions on Electron Devices, and was authored by Kangguo Cheng, Chanro Park, Heng Wu, Juntao Li, Son Nguyen, Jingyun Zhang, Miaomiao Wang, Sanjay Mehta, Zuoguang Liu, Richard Conti, Nicholas J. Loubet, Julien Frougier, Andrew Greene, Tenko Yamashita, Balasubramanian Haran and Rama Divakaruni.

The Award will be presented during the IEEE International Elec-

tron Devices Meeting to be held in December 2021. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of some of the authors follow.

Joachim N. Burghartz EDS Vice-President of Publications and Products

### 2020 EDS LEO ESAKI AWARD

The Leo Esaki Award was established in 2019 to recognize the best paper appearing in a fast turn around archival publication of the IEEE Electron Devices Society, targeted to the IEEE Journal of Electron Devices Society. Among other criteria including technical excellence.

The paper winning the 2020 Leo Esaki Award was selected from over 199 articles that were published in 2020. The paper is entitled, "A New 8T Hybrid Nonvolatile SRAM with Ferroelectric FET." This paper appeared in the February 2020 issue of the IEEE Journal of the Electron Devices Society and authored by Wei-Xiang You, Pin Su and Chenming Hu.

The Award will be presented during the IEEE International Electron Devices Meeting to be held in December 2021. In addition to the Award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the IEEE Electron Devices Society, I would like to congratulate the authors for this achievement.

Joachim Burghartz EDS Vice-President of Publications and Products

# ELECTRON DEVICES SOCIETY MEMBERS NAMED RECIPIENTS OF 2021 IEEE MEDALS

Two EDS members were named 2021 IEEE Medal recipients. Please be sure to visit the IEEE website at https://corporate-awards.ieee.org/recipients/current-recipients/ to view all of the award recipients.

#### 2021 IEEE James H. Mulligan, Jr. Education Medal

John D. Cressler, has been named as the recipient of the 2021 IEEE James H. Mulligan, Jr. Education Medal. The citation states, "For

inspirational teaching and mentoring of undergraduate and graduate students."

A world-renowned researcher in nanoscale-engineered silicon-germanium (SiGe) electronics, John D. Cressler's vocation in life has been educating and mentoring young people, and he has excelled at that as one of Georgia Tech's most decorated professors. Silicon-germanium alloys are a lower-cost alternative to expensive compound semiconductor components but can still provide the performance necessary to enable the higher-frequency requirements of today's and the future's wireless and wired communications devices. As leader of one of the largest and most visible SiGe-focused research teams in the world, Cressler and his students at Georgia Tech have helped pioneer this emerging field that is providing the infrastructure to fuel the global communications revolution. During his tenure there, Cressler has introduced very popular courses. His "Introduction to the Microelectronics and Nanotechnology Revolution" is open to all majors/years, and he started the graduate-level "Siliconbased Heterostructure Devices and Circuits." Both courses utilize textbooks that Cressler wrote, and they

have been adopted at other universities. He also teaches his "Science, Engineering, and Religion: An Interfaith Dialogue" course within Georgia Tech's Ivan Allen Liberal Arts College. This course is open to undergraduate students of all years and majors. Mentoring students is Cressler's great passion, and he feels that his greatest accomplishments are measured by the success of his students. His graduate students have become leaders in the most prominent electronics companies of the world, including IBM, Intel, Texas Instruments, and National Semiconductor; many have received fellowships; and others have become professors and started their own businesses. He also has been asked on many occasions to share his thoughts on teaching, mentoring, and work-life balance with incoming Georgia Tech faculty, staff, and students.

An IEEE Fellow and recipient of the 2013 Georgia Tech Class of 1934 Distinguished Professor Award, Cressler is the Schlumberger Chair Professor in Electronics in the School of Electrical and Computer Engineering and the Ken Byers Teaching Fellow in Science and Religion at the Georgia Institute of Technology, Atlanta, Georgia, USA.

#### 2021 IEEE Jun-Ichi Nishizawa Medal

James J. Coleman, has been named the recipient of the 2021 IEEE

Jun-Ichi Nishizawa Medal. The citation states, "For contributions to the development of strained-layer semiconductor lasers".

Ushering in a new era of laser design, James J. Coleman's work on strained-layer semiconductor lasers has enabled high-power lasers for all-optical telecommunications systems and technologies we take for granted today such as DVD players and laser pointers. Coleman recognized early the importance of strained laver lasers as efficient sources in the 980-nm pump band of erbium-doped fibers and was the first to systematically study and demonstrate reliable strained-layer semiconductor layers operating in the 900-1100-nm range using indium gallium arsenide quantum wells. His pioneering studies were the first to relate strain, performance, and reliability in this system and confirmed earlier predictions that threshold current densities are lower for these devices compared to unstrained lasers. These lasers are now widely used in fiber-optic telecommunications networks as pump sources for optical amplifiers. The simple, all-optical erbiumdoped optical-fiber amplifier has replaced more complex, more costly, and less reliable optical-electricaloptical regeneration circuitry. Prior

to Coleman's work there had been theoretical predictions of the potential advantages of strained quantum-well lasers in the 980-nm band; however, his experimental work established their commercial viability, which was crucial for the acceptance of this technology. Today, virtually all semiconductor lasers routinely use strain-reduced valence band (hole) effective mass as a design variable. In his early career, Coleman contributed to the development of long wavelength telecommunication diode lasers grown by liquid phase epitaxy, and he was involved in early demonstrations of the effectiveness of metalorganic chemical vapor deposition (MOCVD) to make quantum well lasers, solar cells, and photodetectors with better performance characteristics. His more recent work includes high-performance lasers, integrated lasers, and other photonic devices produced through selectivearea epitaxy and novel growth processes for quantum-dot lasers and other three-dimensional nanostructures. Other commercial products also utilize his laser designs for applications in displays and information storage and retrieval.

An IEEE Fellow and member of the U.S. National Academy of Engineering, Coleman is the Presidential Distinguished Professor of Photonics at the University of Texas at Arlington, Arlington, Texas, USA.

> Fernando Guarin EDS Awards Chair Global Foundries

## CALL FOR NOMINATIONS IEEE EDS WILLIAM R. CHERRY AWARD

The IEEE Electron Devices Society invites the submission of nominations for the 2022 William R. Cherry Award.

This Award is named in honor of William R. Cherry, a founder of the photovoltaic community. In the 1950's, he was instrumental in establishing solar cells as the ideal power source for space satellites and for recognizing, advocating, and nurturing the use of photovoltaic systems for terrestrial applications. The William R. Cherry Award was instituted in 1980, shortly after his death. The purpose of the Award is to recognize an individual engineer or scientist who devoted a part of their professional life to the advancement of the science and technology of photovoltaic energy conversion. The nominee must have made significant contributions to the science and/or technology of PV energy conversion, with dissemination by substantial publications and presentations. Professional society activities, promotional and/or organizational

efforts and achievements are not considerations in the election for the Award.

The Award consists of a plaque, monetary award, recognition and a dedicated Cherry Award Talk during the Photovoltaic Specialists Conference.

#### Nominate:

William R. Cherry Award online nomination form: https://ieeeforms.wufoo.com/forms/eds-william-r-cherry-award-nomination-form/

#### **Submission Deadline:**

15 January 2022

#### For more information:

https://ieee-pvsc.org/PVSC49/awards-cherry.php#

# EDS Young Professionals

## PRAGYA KUSHWAHA: REFLECTIONS OF AN EDS YOUNG PROFESSIONAL

The Young Professional guest in this issue of the Newsletter is Pragya Kushwaha, Electron Devices Society's 2019 Early Career Award win-

ner and a scientist at Space Application Centre (SAC), Ahmedabad, India, which is one of the centers of Indian Space Research Organization (ISRO). Her perceptions about EDS and views regarding professional development and career growth are reflected in the discussion. Here are the excerpts of the interview with Pragya Kushwaha made by Manoj Saxena, the Newsletter Associate Editor-in-Chief.

Manoj Saxena: My first question is what was the specific temptation, if any, which made you join EDS which is a part of the largest professional organization in the globe?

Pragya Kushwaha: Most of the universities/institutes have subscription of IEEE journals/conferences. However, students seldom realize this opportunity and the importance of IEEE membership. During my masters I came to know that I can access IEEE research papers even from my home. That was the tipping point which tempted me to take IEEE membership for the first time. Eventually I realized that being a researcher in the field of electron devices, it is the need of the hour to stay tuned with cutting edge technologies. IEEE EDS serves this purpose by facilitating an access for young professionals to a knowledge sharing platform.

MS: You won the prestigious EDS Early Career Award, an honor most of the young professionals aspire to. How do you consider this recognition and what are your plans to further develop your research career?

PK: I am honored to have this prestigious award as it not only recognizes my work internationally but has also made me India's first woman scientist a recipient of this award. This award encourages me to carry out my future research work with more enthusiasm. Till date my contributions in the field of electron devices revolve around the characterization techniques and industry standard compact model development for a betterment of the state-of-the-art CMOS devices, i.e. FinFETs, FDSOI MOSFETs, NCFETs. We are witnessing an era where the semiconductor industry is facing radical changes due to the emergence of several new computing techniques such as quantum computing, neuromorphic computing and artificial intelligence. My vision is to make these emerging computing techniques compatible with the state-of-the art CMOS devices to facilitate more and more functionality from a single chip at low cost.

MS: As a Young Professional, how do you position your interest in your own field with the activities and services you perform as an EDS member/volunteer?

**PK:** IEEE EDS is an umbrella entity which runs numerous technical and non-technical activities under which it serves our society. The Society not only facilitates access to the research platform for sharing knowledge but also connects young professionals

with their peer groups. I am fortunate enough to be a part of technical as well as non-technical activities running under the Society such as EDS Compact Modeling Committee, EDS Women in Engineering (WIE) and EDSYoung Professionals (YP) Committee. The IEEE VLSI Symposia is one of the events where EDS YP are present every year. During my doctorate, I felt that these kinds of networking platforms provided me the opportunity to explore new areas of interest and to meet experts of my field. Having a specialization in the very-large-scale integrated circuits (VLSI) field, I was invited to organize the online mentoring event for VLSI Symposia 2020 where I invited my colleagues and senior experts from Academia/Industry to make this event successful. Many young researchers joined this event to get answers for their queries and to get guidance from experts. I will be happy to give my services to EDS technical/non-technical activities also in future.

MS: What are your thoughts about the EDS membership and its paybacks? Whether the EDS membership benefited you at any time in your career growth? If so, how?

PK: I have been an active member of IEEE EDS since 2016. Online subscription of EDS Newsletter and IEEE Spectrum keeps me aware of the latest technology and its R&D efforts worldwide. As an IEEE EDS member, I regularly receive information about upcoming IEEE events and conferences. These international conferences organized by the Society provide a platform where academia and industry representatives meet and share their visions on future technologies.

As a young professional, it has always been a great opportunity for me to attend EDS conferences (i.e. IEDM, S3S) where I got a chance to meet academia/industry partners. This is one of the reasons that my research is recognized as state-of-the-art work and the developed compact models are still appreciated by companies like Globalfoundries and Qualcomm. Today I am serving Society as a reviewer of many reputed EDS journals (i.e., IEEETED, MTT and EDL) and the only woman member of EDS compact modeling technical committee which I believe are the paybacks for me.

MS: As an YP, how do you consider the ED Society as a whole and what are the changes or developments you would like to see in evolving this professional body as a group devoted to humanity and its causes?

PK: EDS as a professional body has a vision to nurture good quality research work worldwide for the betterment of humankind. EDS not only provides technical platforms to the young professionals but also recognizes professors/ industry experts for their contributions in the field of education and research. I feel this kind of recognition of hard work by the IEEE EDS will definitely motivate young engineers to contribute in the field of electron devices.

MS: What are your suggestions and recommendations for those young professionals who may aspire to join EDS?

**PK**: I still remember those happy student life moments when I benefited from IEEE EDS student member discounts while registering for IEEE conferences. These are schemes which show that EDS has a vision to motivate young engineers to attend conferences and to get benefited technically. During the COVID pandemic, IEEE continued its services by providing free access to many e-books and even conducted free online webinars for its members on state-of-the art topics which shows dedication of the Society towards technology development. EDS membership has helped me a lot in growing professionally in my career. I would strongly recommend young professionals to join this prestigious community for their bright future.

MS: As an EDS Young Professional and a young researcher in the field, how do you consider the prospects of scientific research in this field for the progress of Humanity as a whole?

PK: We are born in the era when technology changes every day. Researchers are trying their best to make human life simpler than before. I am thankful to EDS for providing a common platform to the academia as well industry to collaborate. I believe these kinds of efforts will definitely improve scientific research and serve humanity.

#### Biography

Pragya Kushwaha received her Ph.D. degree in microelectronics specialization from Indian Institute of Technology Kanpur in 2017. She completed her postdoctoral fellowship (2017-2020) in the University of California Berkeley, USA. Dr. Kushwaha is the first Indian woman scientist to receive IEEE EDS Early Career Award in 2019. Dr. Kushwaha has been selected for IN-SPIRE faculty fellowship 2019 and a prestigious Ramanujan fellowship 2020 by Department of Science and Technology, India. She joined Space Applications Centre (SAC) Ahmedabad, India, a center of ISRO, in July 2020 as SD scientist in the microelectronics group. Dr. Kushwaha has over 55 publications in international journals and conferences and two book chapters on her name. She is reviewer of many reputed EDS journals (i.e., IEEE TED, MTT and EDL). Dr. Kushwaha is the only woman member of EDS compact modeling technical committee since July 2020.

### NEW! **EDS Podcasts Available to Everyone!**

EDS is pleased to announce our new podcast series. Join us as we host interviews with some of the most successful members of our Society sharing their lives and careers. Their insight and wisdom will be invaluable inspiration and knowledge for those in the engineering field. Stay tuned to our social media channels and website for future announcements on upcoming events.

# WOMEN IN ENGINEERING

## ELYSE ROSENBAUM—A CAREER IN ACADEMIA— IMPRESSIONS AND HINTS

My intended audience for this article is early-career engineers, especially those still engaged in university studies. I, too, spend much

of my time on a university campus, but as a faculty member rather than a student. I am the Hasselbrock Professor in Electrical and Computer Engineering at the University of Illinois at Urbana-Champaign. Some of you may be considering a career in academia. This article will shed a bit of light on what it is that professors do when we are not lecturing in the classroom or reviewing our graduate students' research results. I will also provide focused advice for the woman readers.

I was asked to contribute a nontechnical article for the Women in EDS series. Why did I agree? Many readers may be unaware that professors are evaluated annually for their contributions in three spheres: teaching, research, and professional service. Those evaluations determine our next year's salary and eligibility for promotion in rank. My authorship of this article constitutes professional service, and that was one of my motivations for doing it. That brings me to my first piece of advice for young engineers: Look for service opportunities that fit your interests and are not overly burdensome (i.e., very time consuming). Do not reflexively say yes to all requests.

If you had asked me to make predictions about the year 2021 back when I was a student in electrical engineering, I would not have projected that the EDS Newsletter would contain a series of articles on Women in EDS. I could not have imagined that there would be anything noteworthy about women in our profession. Indeed sadly, the engineering workforce of 2021 doesn't have significantly higher female representation than that of 1991. Perhaps the young women reading this article will be the ones to finally achieve parity. There are no good reasons for you not to do so! Engineering competency and engineering brilliance are found in equal measures among male and female students. My perception is that historically, more young men entered the university with confidence in their hands-on technical skills, perhaps having developed them by participating in a robotics club or an Eagle Scout project. Today, we find that more and more young women participate in "tech" activities during their high school years. However, even if a student did not participate in youth engineering activities, it is not an impediment to successful completion of an engineering degree or to a long, productive career as an engineer.

Since the engineering workplace will be majority male for at least the next decade, how is a woman to cope with her minority status? You should strive to rapidly establish a reputation for excellence and reliability, so work hard starting day one. Advocate for yourself; ask to be assigned to high-excitement, high-visibility new projects. Choose your battles carefully for maximum impact; if you refrain from objecting every time a male coworker says something a bit offensive or you detect implicit bias, people will take notice when you do call out an inequity or an inappropriate statement. In the