# ELECTRON DEVICES SOCIET

Newslette

OCTOBER 2022 VOL. 29, NO. 4 ISSN: 1074 1879

**EDITOR-IN-CHIEF: DANIEL TOMASZEWSKI**

#### TABLE OF CONTENTS

| MORRIS CHANG-2022 IEEE EDS CELEBRATED MEMBER 1                                                                                                                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 75TH ANNIVERSARY OF THE TRANSISTOR                                                                                                                                  |

| • The 2022 IEEE VLSI Symposium on Technology & Circuits                                                                                                             |

| UPCOMING TECHNICAL MEETINGS                                                                                                                                         |

| SOCIETY NEWS                                                                                                                                                        |

| AWARDS AND RECOGNITIONS                                                                                                                                             |

| EDS YOUNG PROFESSIONALS25 • Mentoring                                                                                                                               |

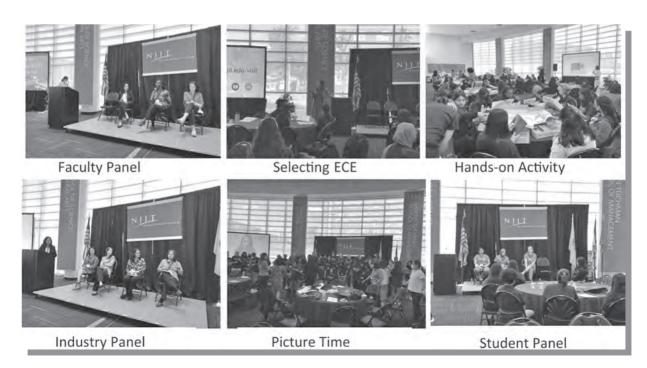

| Women in EDS and Computational Electronics     Where the ECE Event at New Jersey Institute of Technology     Special Offer for Members of IEEE Women in Engineering |

| EDS HUMANITARIAN NEWS                                                                                                                                               |

| CHAPTER NEWS                                                                                                                                                        |

| REGIONAL NEWS                                                                                                                                                       |

| EDS MEETINGS CALENDAR52                                                                                                                                             |

| CALL FOR PAPERS54                                                                                                                                                   |

| EDS FIELD OF INTEREST, MISSION AND VISION STATEMENTS 56                                                                                                             |

## **IEEE**

# MORRIS CHANG RECOGNIZED AS THE 2022 IEEE EDS CELEBRATED MEMBER OF THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

The Institute of Electrical and Electronics Engineers (IEEE) named Dr. Morris Chang, TSMC, as the "IEEE EDS Celebrated Member" of 2022. This recognition will take place during the 2022 IEEE International Electron Devices Meeting (IEDM) in San Francisco, California, U.S.A. EDS takes pride in the accomplish-

ments of our Celebrated Members and draw from the inspiration to advance our field and to achieve more because it is not only their work but ours as well, that can help transform the world around us.

Dr. Morris Chang founded Taiwan Semiconductor Manufacturing Company Ltd. (TSMC) in 1987, served as its Chairman for 31 years, and its CEO for many of those 31 years. Dr. Chang retired from TSMC in June 2018. TSMC pioneered the dedicated silicon foundry business model and has served as a powerful force of innovation in the information industry.

Prior to his career in Taiwan, Dr. Chang's career was in the United States. He served at Texas Instruments for 25 years (1958–1983), where he was Group Vice President responsible for worldwide semiconductor business for six years.

Dr. Chang received his B.S. and M.S. degrees in Mechanical Engineering from M.I.T. in 1952 and 1953, and his Ph.D. in Electrical Engineering from Stanford in 1964. He has received honorary doctorates from eight universities worldwide.

Dr. Chang received many honors and awards in his career. Among them were: the "Exemplary Leadership Award" of the Global Semiconductor Alliance (GSA) (1999), the IEEE Robert N. Noyce Medal for Exceptional Contributions to Microelectronics Industry (2000), Nikkei Asia Prize (2005), and the highest honor of the Semiconductor Industry Association (U.S.), its Robert N. Noyce Award (2008). He received the IEEE Medal of Honor (2011), the R.O.C. Order of the Brilliant Star (2011), the SEMI Akira Inoue award for green

## ELECTRON DEVICES SOCIETY

#### President

Ravi Todi Western Digital Technologies Email: rtodi@ieee.org

#### President-Elect

Bin Zhao Freescale Semiconductor Email: bin.zhao@ieee.org

#### Treasurer

Roger Booth Qualcomm

Email: boothrog@yahoo.com

#### Secretary

M.K. Radhakrishnan NanoRel Email: radhakrishnan@ieee.org

#### Sr. Past President

Fernando Guarin GlobalFoundries

Email: fernando.guarin@ieee.org

#### Vice President of Education

Navakanta Bhat Indian Institute of Science Email: navakant@gmail.com

#### Vice President of Meetings

Kazunari Ishimaru Kioxia Corporation

Email: kazu.ishimaru@kioxia.com

#### Vice President of Membership and Services

Merlyne de Souza University of Sheffield Email: m.desouza@sheffield.ac.uk

#### Vice President of Publications and Products

and Products Arokia Nathan

University of Cambridge Email: an299@cam.ac.uk

#### Vice President of Regions/ Chapters

Murty Polavarapu Space Electronics Solutions Email: murtyp@ieee.org

#### Vice President of Strategic Directions

Doug P. Verret IEEE Fellow

Email: dougverret@gmail.com

#### Vice President of Technical Committees

John Dallessase University of Illinois at Urbana-Champaign Email: jdallesa@illinois.edu

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2022               | TERM   | 2023               | TERM | 2024                 | Term |

|--------------------|--------|--------------------|------|----------------------|------|

| Constantin Buluce  | a (1)  | Roger Booth        | (2)  | Mario Aleman         | (1)  |

| Daniel Mauricio    |        | Xiaojun Guo        | (1)  | Paul Berger          | (1)  |

| Camacho Monteio    | (1)    | Edmundo A.         |      | Yogesh Singh Chauhan | (1)  |

| John Dallesasse    | (1)    | Gutierrez-D.       | (2)  | Patrick Fay          | (1)  |

| Mario Lanza        | (1)    | Francesca lacopi   | (1)  | Kazunari Ishimaru    | (1)  |

| Geok Ing Ng        | (1)    | Benjamin Iniquez   | (2)  | Bill Nehrer          | (1)  |

| Claudio Paoloni    | (1)    | P. Susthitha Menon | (1)  | Merlyne de Souza     | (1)  |

| Hitoshi Wakabayash | ni (1) | Manoj Saxena       | (2)  | ,                    |      |

| ,                  |        | Sumant Sood        | (2)  |                      |      |

## NEWSLETTER EDITORIAL STAFF

#### Editor-In-Chief

Daniel Tomaszewski Institute of Microelectronics and Photonics Email: daniel.tomaszewski@imif.lukasiewicz.gov.pl

#### Associate Editor-in-Chief

Manoj Saxena Deen Dayal Upadhyaya College University of Delhi

University of Delhi Email: msaxena@ieee.org

## REGIONS 1-6, 7 & 9 Eastern, Northeastern & Southeastern USA

(Regions 1, 2 & 3) Rinus Lee

TEL Technology Center, America Email: rinuslee@ieee.org

#### Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University Email: mmadachi@sfu.ca

#### Southwestern & Western USA (Regions 5 & 6)

Lawrence Larson Texas State University Email: Larry.Larson@ieee.org

#### Latin America North (Region 9)

Joel Molina Reyes INAOE Email: jmolina@inaoep.mx

#### Latin America South (Region 9)

Paula Ghedini Der Agopian UNESP, Sao Paulo State University Email: paula.agopian@unesp.br

#### REGION 8 Scandinavia & Central Europe

Marcin Janicki

Lodz University of Technology

Email: janicki@dmcs.pl

#### Eastern Europe

Mykhaylo Andriychuk Pidstryhach Inst. for App. Problems of Mech. and Math. Email: andr@iapmm.lviv.ua

#### United Kingdom, Middle East & Africa

Stewart Smith Scottish Microelectronics Centre Email: stewart.smith@ed.ac.uk

#### Western Europe

Mike Schwarz Mittelhessen University of Applied Sciences Email: mike.schwarz1980@ qooglemail.com

### REGION 10 Australia, New Zealand & South East Asia

Sharma Rao Balakrishnan Universiti Sains Islam Malaysia Email: sharma@usim.edu.my

#### North East and East Asia

Tuo-Hung Hou National Yang Ming Chiao Tung University Email: thhou@mail.nctu.edu.tw

#### Email. timod@mail.nctd.edd.tv

#### South Asia

Soumya Pandit University of Calcutta Email: soumya\_pandit@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in-Chief or the Regional Editor for your region. The email addresses of all Regional Editors are listed on this page. Email is the preferred form of submission.

#### Newsletter Deadlines

October July 1st

January October 1st

April January 1st

July April 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2022 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

#### 5TH ANNIVERSARY TRANSISTOR

#### Moore's Law Scaling and Radiation EFFECTS IN MOS DEVICES

BY DAN FLEETWOOD, VANDERBILT UNIVERSITY

Microelectronic devices and ICs experience high radiation levels in space, defense, and particle accelerator environments. After the invention of the transistor in 1947 [1]. radiation effects research focused primarily on defect creation in semiconductor materials and displacement damage in bipolar junction transistors [2]-[5]. The sensitivity of MOS transistors to total ionizing dose (TID) effects was discovered by Hughes and Giroux in 1964 [6], just one year before Moore's law was postulated [7], [8]. An early and influential study of TID effects in MOS devices was co-authored in 1967 by a young Andy Grove, while still at Fairchild Semiconductor [9], [10], The modern era of radiation-tolerant MOS electronics began in 1971 with the development of radiation-hardened pMOS technology by Hughes Aircraft Company [8], [11].

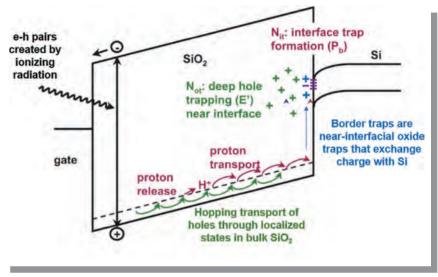

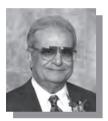

Fig. 1 illustrates the chain of events that occur during and after TID-irradiation of MOS devices [8], [12], [13]. Primary effects include hole transport and trapping in gate and isolation oxides and buildup of interface and border traps at or near gate-dielectric/ semiconductor boundaries. Proton (H+) release during hole transport and field-induced H+ transport to the Si/ SiO<sub>2</sub> interface play critical roles in interface and border-trap formation [8], [12], [13].

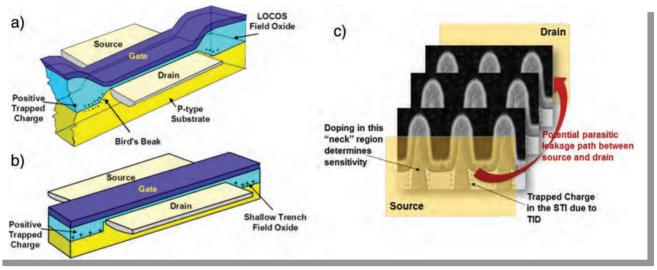

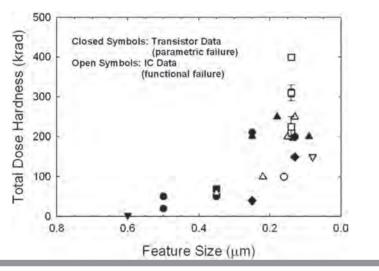

Moore's Law scaling and changes in device architecture significantly affect MOS radiation response [10], [14]-[17]. Progressively thinner gate and isolation oxides in highly scaled devices (Fig. 2) generally lead to enhanced TID tolerance (Fig. 3). How-

Figure 1. Schematic illustration of electron-hole pair generation, charge transport, and trapping in irradiated MOS devices. (After 181, 1121, 1131.)

ever, in current and future generation FinFETs (Fig. 2(c)), gate-all-around, and nanosheet or forksheet devices, the thickness and quality of the gate insulator and isolation oxides, transistor channel/edge doping levels, and strength of gate control all strongly affect charge trapping [10], [14]-[17]. Thus, significant variations are expected and observed in the TID response of MOS devices and ICs [10], [16].

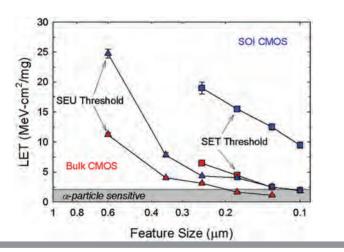

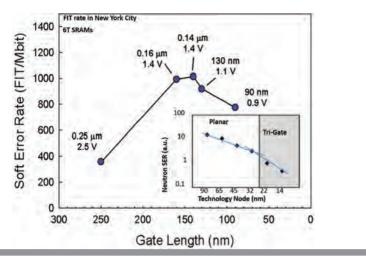

As MOS technologies have evolved and device dimensions and operating voltages have decreased, single-event effects (SEE) due to cosmic rays and/or high-energy protons have become an increasing concern. When a single high-energy charged particle deposits a sufficient amount of energy per unit path length to generate a densely ionized track, soft or hard errors can result, with probabilities determined by the amount of collected charge and resulting device/ IC response [10], [16], [18]-[20]. Until the ~130 nm technology node, SEE in electronics in space environments typically increased with decreasing feature size, as seen in Figs. 4 and 5. This is due primarily to reductions in operating voltage and critical charge to upset [10], [16], [18]-[20]. Fortunately, Moore's Law scaling greatly enhances design, layout, modeling, and simulation capabilities, which are increasingly necessary to understand and mitigate the resulting effects [14], [16], [18].

By the mid-1990s, device scaling made terrestrial electronics sensitive to soft errors caused by reactions of atmospheric neutrons in silicon and surrounding materials [21], [22]. Removing B<sub>10</sub> from processing and changing to FinFET/Tri-Gate

Figure 2. MOS devices with (a) LOCOS (local oxidation of silicon) or (b) shallow-trench isolation, STI [15]. (c) Bulk FinFETs [17].

Figure 3. Hardness of MOS ICs to TID vs. feature size. (After [16].)

Figure 4. Critical ion LET (linear energy transfer) to failure vs. feature size for planar bulk and SOI (silicon on insulator) CMOS ICs. The buried oxide layer makes SOI devices less sensitive to SEE. (After [16].)

architecture (Fig. 5, inset) can greatly reduce SERs in ICs [19], [22]. However, as transistor sensitive volumes become smaller than ion tracks and transistor packing densities continue to increase, multiple-bit errors and "charge sharing" among adjacent devices become more significant [10], [16], [18]. ICs now are more three-dimensional, and nanoscale MOS devices can be sensitive to single-particle displacement damage [10], [23]. Thus, each new IC technology generation continues to present new radiation-effects challenges.

#### **Biography**

Dan Fleetwood received his Ph.D. from Purdue University in 1984. He joined Sandia National Laboratories in 1984 and was named a Dis-

tinguished Member of Technical Staff in 1990. Dan joined Vanderbilt University as a Professor of Electrical Engineering in 1999. From 2003–2020 he chaired Vanderbilt's EECS Department; since 2009 he has been appointed Olin H. Landreth Chair in Engineering. He received the 2009 IEEE Nuclear and Plasma Sciences Merit Award, and is a Fellow of IEEE, AAAS, and the American Physical

Figure 5. Feature size dependence of terrestrial-neutron soft-error rates (SER) in bulk planar six-transistor static RAMs and (inset) tri-gate (FinFET) CMOS ICs. One FIT = one failure in 10° h. (After [16] [22])

Society. His research interests include radiation effects on microelectronics, low-frequency noise, and defects in microelectronic materials and devices.

#### References

[1] J. Bardeen and W. H. Brattain, "The transistor - A semi-conductor triode," Phys. Rev., vol. 74, no. 2, pp. 230-231, Jul. 1948.

[2] W. E. Johnson and K. Lark-Horovitz. "Neutron irradiated semiconductors," Phys. Rev., vol. 76, no. 3, pp. 442-443, Aug. 1949.

[3] G. H. Kinchin and R. S. Pease, "The displacement of atoms in solids by radiation," Rep. Prog. Phys., vol. 18, no. 1, pp. 1-51, Jan. 1955.

[4] G. C. Messenger and J. P. Spratt, "The effects of neutron irradiation on germanium and silicon," Proc. IRE, vol. 46, no. 6, pp. 1038-1044, Jun. 1958.

[5] J. R. Srour, C. J. Marshall and P. W. Marshall, "Review of displacement damage effects in silicon devices." IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 653-670, June 2003.

[6] H. L. Hughes and R. R. Giroux, "Space radiation affects MOS FET's," Electronics, vol. 37, pp. 58-60, Dec. 1964.

[7] G. E. Moore, "Cramming more components onto integrated circuits," Electronics, vol. 38, no. 8, pp. 114-117, Apr. 1965.

[8] D. M. Fleetwood, "Total ionizing dose effects in MOS and low-dose-rate sensitive linear-bipolar devices," IEEE Trans. Nucl. Sci., vol. 60, no. 3, pp. 1706-1730, Jun. 2013.

[9] E. H. Snow, A. S. Grove, and D. J. Fitzgerald, "Effects of ionizing radiation on oxidized silicon surfaces and planar devices," Proc. IEEE, vol. 55, no. 7, pp. 1168-1185, Jul. 1967.

[10] D. M. Fleetwood, "Radiation effects in a post-Moore world," IEEE Trans. Nucl. Sci., vol. 68, no. 5, pp. 509-545, May 2021.

[11] K. G. Aubuchon, "Radiation hardening of MOS devices by optimization of the thermal SiO2 gate insulator," IEEE Trans. Nucl. Sci., vol. 18, no. 6, pp. 117-125, Dec. 1971.

[12]T. R. Oldham and F. B. McLean, "Total ionizing dose effects in MOS oxides and devices," IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 483-499, Jun. 2003.

[13] J. R. Schwank, M. R. Shaneyfelt, D. M. Fleetwood, J. A. Felix, P. E. Dodd, P. Paillet, and V. Ferlet-Cavrois, "Radiation effects in MOS oxides," IEEE Trans. Nucl. Sci., vol. 55, no. 4, pp. 1833-1853, Aug. 2008.

[14] D. M. Fleetwood, "Evolution of total ionizing dose effects in MOS devices with Moore's Law scaling," IEEETrans. Nucl. Sci., vol. 65, no. 8, pp. 1465-1481, Aug. 2018.

[15] M. R. Shaneyfelt, P. E. Dodd, B. L. Draper, and R. S. Flores, "Challenges in hardening technologies using shallowtrench isolation," IEEE Trans. Nucl. Sci., vol. 45, no. 6, pp. 2584-2592, Dec. 1998.

[16] P. E. Dodd, M. R. Shaneyfelt, J. R. Schwank, and J. A. Felix, "Current and future challenges in radiation effects on CMOS electronics." IEEE Trans. Nucl. Sci., vol. 57, no. 4, pp. 1747-1763, Aug. 2010.

[17] I. Chatterjee, et al., "Geometry dependence of total-dose effects in bulk Fin-FETs," IEEE Trans. Nucl. Sci., vol. 61, no. 6, pp. 2951-2958, Dec. 2014.

[18] P. E. Dodd and L. W. Massengill, "Basic mechanisms and modeling of single-event upset in digital microelectronics," IEEE Trans. Nucl. Sci., vol. 50, no. 3, pp. 583-602, Jun. 2003.

[19] R. C. Baumann, "Radiation-induced soft errors in advanced semiconductor technologies," IEEE Trans. Dev. Mater. Reliab., vol. 5, no. 3, pp. 305-316, Sep. 2005.

[20] D. Kobayashi, "Scaling trends of digital single-event effects: A survey of SEU and SET parameters and comparison with transistor performance," IEEE Trans. Nucl. Sci., vol. 68, no. 2, pp. 124-148, Feb. 2021.

[21] P. Hazucha and C. Svensson, "Impact of CMOS technology scaling on the atmospheric neutron soft error rate," IEEE Trans. Nucl. Sci., vol. 47, no. 6, pp. 2586-2594, Dec. 2000.

[22] N. Seifert, et al., "Soft error rate improvements in 14-nm technology featuring second-generation 3D tri-gate transistors," IEEE Trans. Nucl. Sci., vol. 62, no. 6, pp. 2570-2577, Dec. 2015.

[23] M. G. Esposito, et al., "Investigating heavy-ion effects on 14-nm process FinFETs: Displacement damage vs. total ionizing dose," IEEE Trans. Nucl. Sci., vol. 68, no. 5, pp. 724-732, May 2021.

## The Silicon-Germanium Heterojunction Bipolar Transistor

John D. Cressler

Regents Professor and Schlumberger Chair Professor in Electronics

School of Electrical and Computer Engineering

Georgia Tech

Seventy-five years of the transistor (shortened from "transresistance amplifier" to "transresistor" to "transistor"). Time flies. A remarkable little piece of quantum physics in action. In 2022, transistors are viralsized, nearly as fast as a speed of light, and importantly, cleverly possess that unique golden attribute of amplification, making tiny voltages and currents larger. There are over 10<sup>24</sup> transistors on Earth in 2022, made possible by the jaw-dropping exponential growth patterns embodied in Moore's law. Transistors are ubiquitous to modern life, whether seen or unseen by both purveyors and consumers of technology. Surely the word "transistor" should be added to the vocabulary of every single person on Earth. In sort, all of modern technology, without exception, from smartphones to automobiles to planes to internet to GPS, would instantly cease to function if they were subtracted from the planet. In fact, in terms of its impact on the trajectory of human civilization, one could fairly argue that the invention of the transistor is the single most important discovery in human history. Bold words, but defensible [1].

Transistor action was first observed by Bardeen and Brattain at Bell Labs in late 1947 using a point contact device. This demonstration of a solid-state amplifying object is also unique in the historical record for the precision with which we can locate it—December 23, 1947, at around 5:00 pm. The precise moment the world changed irrevocably. Snow was falling in Murray Hill, NJ. Not to be outdone, by February of 1948, Shockley, the third member of the "transistor three," developed the the-

ory for how this clever little object did its remarkable thing, and importantly, could be further improved, leading three years later to the first bipolar junction transistor (BJT) on April 12, 1950. That first BJT was made, ironically, from Ge, not Si.

The concept of the heterojunction (a iunction built from two different semiconductors) bipolar transistor (HBT) is a surprisingly old one, dating in fact to the fundamental BJT patent filed by Shockley in 1948. Given that the first bipolar transistor was built from Ge, and III-V semiconductors were not yet on the scene, it seems clear that Shockley envisioned the combination of Si (wider bandgap emitter) and Ge (narrower bandgap base) to form a SiGe HBT that would yield useful properties. The basic formulation and operational theory of the HBT, for both the traditional wide bandgap emitter plus narrow bandgap base approach found in most modern III-V HBTs, as well as the drift-base (graded) approach used in SiGe HBTs today, was pioneered by Kroemer, and was largely in place by 1957. It is noteworthy that Kroemer in fact worked hard early on to realize a SiGe HBT, without success, ultimately pushing him towards the III-V material systems for his heterostructure studies, a path that proved, in the end, to be quite fruitful for him, since he shared the Nobel Prize in physics in 2000 for his work in (III-V) bandgap engineering for electronic and photonic applications. While III-V HBTs (e.g., AIGaAs/ GaAs) began appearing in the 1970s, driven largely by the needs for active microwave components in the defense industry, reducing the SiGe/Si HBT to practical reality took 30 years after the basic theory was in place, due primarily to material growth limitations.

The achievement of practical SiGe/Si heterostructures, the key to building SiGe HBTs, solidly rests on the shoulders of material scientists and crystal growers, those purveyors of the semiconductor "black arts" associated with the deposition of pristine SiGe alloys of nanoscale dimensionality onto enormous Si wafers, with near-infinite precision. Once device-quality SiGe alloys were finally achieved in the mid-1980s, progress was guite rapid.

The first functional SiGe HBT was demonstrated in December of 1987, 40 years, nearly to the day, after the first transistor. That pioneering result showed a SiGe HBT with functional, albeit leaky, DC I-V characteristics; but it was a SiGe HBT, it worked, and it was the first. It is an often-overlooked historical point, however, that at least four independent groups were simultaneously racing to demonstrate the first functional SiGe HBT. Worldwide attention became squarely focused on SiGe HBT technology in June of 1990, with the eyebrow-lifting demonstration of a SiGe HBT with a peak cutoff frequency of 75 GHz by IBM, at the time twice the performance of state-of-the-art Si BJTs, clearly demonstrating the future potential of the Si-processing-compatible SiGe technology. The pursuit of SiGe HBTs for practical circuit applications began in earnest at a large number of industrial and university laboratories around the world, a trend that has not let up since and likely never will [2]-[3].

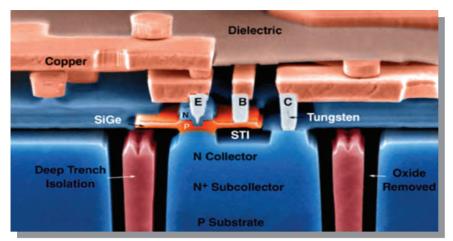

While it may be tempting to assume that CMOS is the only transistor game in town, SiGe HBTs are alive and well, and growing rapidly in both sophistication and diversity of utilization. SiGe HBT (Fig. 1) frequency response since

Figure 1. Decorated cross-sectional scanning electron micrograph of a SiGe HBT. The epitaxial SiGe alloy is shown in orange. (Courtesy of IBM Corporation.)

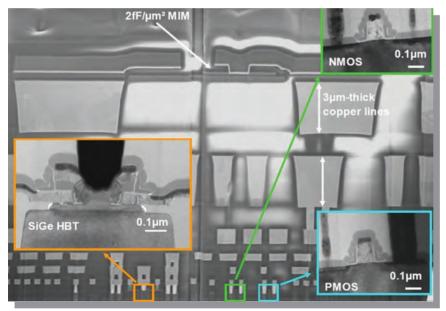

Figure 2. Cross-sectional scanning electron micrograph of a modern SiGe BiCMOS platform, showing SiGe HBT, CMOS devices (n-channel and p-channel), and the back-end-of-the-line metallization layers and passive elements. (Courtesy of P. Chevalier and ST Microelectronics.)

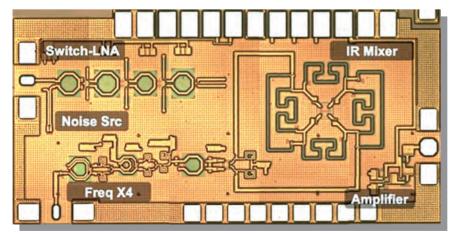

Figure 3. Example of a SiGe BiCMOS mm-wave integrated circuit, a 60 GHz SiGe radiometer for space-based remote sensing designed for use on a CubeSat. The die size is less than 2 mm².

that pivotal 1990 unveiling has grown by 10x in only thirty years! Quite a feat. SiGe HBTs are now approaching THz levels of performance in 100% Si manufacturing compatible commercial platforms (>700 GHz and counting at 300K in 2022), something unimaginable at the field's inception.

Now universally practiced as a BiC-MOS technology platform (SiGe HBT + CMOS together on die), SiGe technology (Fig. 2) offers an ideal division of labor between bipolars and FETs, which each have their own respective attributes, clearly, and remains in wide use globally in performance-constrained analog, RF through mm-wave, and even digital applications (Fig. 3). SiGe HBTs also possess a natural affinity for robust operation in so-called "extreme environments," which include exposure to intense space radiation and at deep cryogenic temperatures [4].

There you have it-the SiGe HBT. A remarkable product of human ingenuity and hard work. Happy anniversary to the transistor, and its remarkable SiGe HBT progeny!

#### **Biography**

John D. Cressler received his B.S. from Georgia Tech in 1984, and his Ph.D. from Co**lumbia** University in 1990. From 1984 to 1992, he

was on the research staff at the IBM Thomas J. Watson Research Center. and from 1992 to 2002 he served on the faculty at Auburn University. In 2002, he joined the faculty at Georgia Tech, and is currently Regents Professor and Schlumberger Chair Professor in Electronics in the School of Electrical and Computer Engineering, as well as the Ken Byers Teaching Fellow in Science and Religion. The basic thrust of Cressler's research is to develop Si/SiGe-based micro/nanoelectronic and photonic devices, circuits, and systems for next-generation applications within the global terrestrial and space-based electronics/ photonics infrastructure. His research interests include: Si-based (SiGe/ strained-Si) heterostructure devices and technology, mixed-signal circuits (analog, digital, RF to mm-wave) built from these devices, integrated Si/SiGe photonic devices and circuits, novel scientific instruments for spacesystems, radiation effects in electronic and photonic devices and circuits, cryogenic electronics for quantum systems, device-to-circuit interactions, reliability physics, device-level simulation (TCAD), and compact circuit modeling. He and his students have published over 750 scientific papers in this field, and he has graduated 66 Ph.D. students during his 30-year academic career. He was elected Fellow of the Institute of Electrical and Electronics Engineers (IEEE) in 2001 for his research contributions, and was awarded the 2010 Class of

1940 W. Howard Ector Outstanding Teacher Award (Georgia Tech's top teaching award), the 2011 IEEE Leon Kirchmaver Graduate Teaching Award (the IEEE's top graduate teaching award), the Class of 1934 Distinguished Professor Award (the highest honor Georgia Tech bestows on its faculty), and the 2021 IEEE James H. Mulligan, Jr. Education Medal (the highest award IEEE gives in teaching and mentoring). He has served the Electron Devices Society in a number of roles, including as Editor-in-Chief of IEEE Transactions on Electron Devices, from 2012-2015, Cressler's books include Silicon-Germanium Heterojunction Bipolar Transistors, Reinventing Teenagers: the Gentle Art of Instilling Character in Our Young People, Silicon Heterostructure Handbook, Silicon Earth: Introduction to Microelectronics and Nanotechnology, Extreme Environment Electronics, and the historical novels Emeralds of the Alhambra, Shadows in the Shining City, and Fortune's Lament, love stories set in medieval Muslim Spain.

#### References

[1] J.D. Cressler, Silicon Earth: Introduction to Microelectronics and Nanotechnology, Second Edition, CRC Press, Boca Raton, FL, 2016.

[2] J.D. Cressler and G. Niu, *Silicon-Germanium Heterojunction Bipolar Transistors*, Artech House, Boston, MA, 2003.

[3] J.D. Cressler (Editor), Silicon Heterostructure Handbook – Materials, Fabrication, Devices, Circuits, and Applications of SiGe and Si Strained-Layer Epitaxy, CRC Press, Boca Raton, FL, 2006.

[4] J.D. Cressler and A. Mantooth (Editors), *Extreme Environment Electronics*, CRC Press, Boca Raton, FL, 2013.

## MORRIS CHANG RECOGNIZED AS THE 2022 IEEE EDS CELEBRATED MEMBER OF THE INSTITUTE OF ELECTRICAL AND ELECTRONICS ENGINEERS (IEEE)

(continued from page 1)

management (2011), Businessman of the Year by Forbes Asia magazine (2012), the Visionary Award from SPIE (the international society for optics and photonics) (2014), and the R.O.C. Order of Propitious Clouds with Special Grand Cordon (2018).

Dr. Chang is a Member of National Academy of Engineering (U.S.A.),

a Laureate of the Industrial Technology Research Institute (Taiwan), a Life Member Emeritus of MIT Corporation (U.S.A.), and Fellow of the Computer History Museum (U.S.A.).

IEEE is the world's largest association of technical professionals, and the Celebrated Member distinction honors and recognizes

esteemed alumni whose accomplishments inspire young scholars and researchers and take the field to new heights.

For more information, please visit https://eds.ieee.org/members/celebrated-members.

Ravi Todi, EDS President

#### TECHNICAL BRIEFS

#### THE 2022 IEEE VLSI SYMPOSIUM ON TECHNOLOGY & CIRCUITS, NOW FULLY COMBINED AS A SINGLE EVENT

The 2022 Symposium on VLSI Technology & Circuits, completing its 42nd year of delivering a unique convergence of technology and circuits for the microelectronics industry, was held as a five-day hybrid event from 12-17 June 2022 in Honolulu, Hawaii, combining both live sessions onsite at the Hilton Hawaiian Village, as well as on-demand access to selected presentations. Newly merged as a single event, the Symposium featured the theme: "Technology & Circuits for the Critical Infrastructure of the Future." More than 1,293 people attended the Symposium, with a nearly equal split between those attending in person, and those participating virtually.

The weeklong Symposium continued its reputation as the microelectronics industry's premiere international conference integrating technology, circuits, and systems with a range and scope unlike any other conference, including advanced VLSI technology developments, innovative circuit design, and the applications they enable, such as artificial intelligence, machine learning, IoT, wearable/implantable biomedical applications, big data, cloud/ edge computing, virtual reality (VR)/ augmented reality (AR), robotics, and autonomous vehicles.

The main Symposium technical program featured 270 technical papers. In addition to the technical presentations, the Symposium program featured a demonstration session, evening panel discussions, joint focus sessions, short courses, workshops, and a special forum session on Friday following the Symposium main program.

#### **Plenary Sessions**

- "Holistic Patterning to Advance **Semiconductor Manufacturing** for the 2020s and Beyond," by Martin Van den Brink, President & CTO. ASML-Presented via video, this plenary session discussed the convergence of 5G, artificial intelligence, and the billions of connected devices that promise to start a new wave of innovation, bringing advanced computing power to massive amounts of data. The key enabler continues to be affordable scaling, driven by advanced EUV lithography, computational capabilities, fast metrology and inspection. Key developments in these areas included ASML's EUV roadmap for 0.33 NA (low-NA), and the next-generation 0.55 NA (high-NA), as well as a DUV roadmap to deliver cutting edge immersive lithography.

- "Semiconductor Innovations. from Device to System," by Yuh-Jier Mii, Senior Vice President for **R&DTSMC** – This year's Symposium coincides with the 75th anniversary of the invention of the

- transistor and of the semiconductor industry's profound impact on the world and society at large. Technology scaling has been the key driving force behind the numerous innovations that ushered in the Information Age. As the fast-expanding new applications in 5G, AI, ADAS, AR/VR and robotics continue to propel demand for data-centric products and services, future generations of semiconductor technology will require innovations across the entire stack-from material and device to design infrastructure, architecture and system-including 3D stacking technologies to extend scaling and enable more energy-efficient computing.

- "From System-on-Chip (SoC) to System-on Multichip (SoMC) **Architectures: Scaling Integrated Systems Beyond the Limitations** of Deep-Submicron Single Chip Technologies," by Chris Patrick, Senior Vice-President and General Manager, Mobile Handsets, Qualcomm Technologies, Inc. — Relying on IP integration platforms and processes that allow rapid innovation and integration of new IP such as 5G, the mobile wireless revolution has achieved low power and low cost by quickly leveraging new technology nodes. Complex systems have been integrated in SoCs and enhanced every year as technology shrinks. However, current trends in SOCs for diverse markets like mobile, compute, automotive and AI servers will lead to impractical die sizes due to diminishing percentage area shrinkage

- with future deep sub-micron technology nodes, highlighting the need for to transition to a System-on-Multichip (SoMC) approach. Partitioning the SoC into multiple die (also called chiplets) in a multichip configuration may help, but this also brings new challenges.

- "The Rise of Memory in the Ever-Changing AI Era-From Memory to More-Than-Memory," by Seok-Hee Lee, Executive Chairman, Solidgm-Innovation in the field of semiconductor memory has provided one of the key solutions to address the challenges of ever-changing, data-driven computing. It is no longer only important that memory technologies deliver their traditional metrics such as high performance, lower power, lower cost, and higher capacity. They also have to deliver smarter and more functionality in or near memory to minimize data movement, and break down the barrier between compute and memory.

Focus Sessions: As part of the Symposium's program integration, a series of joint focus sessions presented papers with both circuits and technology topics from BEOL processes, new concepts for transistor scaling, 6G, compute-in-memory, biomedical technology, and 3D heterogeneous integration.

### Short Courses on Key VLSI Topics

Three full-day short courses were presented prior to the Symposium technical program:

- The Technology Short Course

"Monolithic & Heterogeneous Integration" focused on advanced

monolithic and heterogeneous

integration with coverage of logic

and memory scaling in monolithic 3D integration, chiplet-based

technologies and systems, and

silicon photonics.

- The Joint Short Course "Advances in Application-Specific Com-

- puting Systems & Technologies" explored advances in application-specific computing systems and technologies, examining the latest developments in augmented reality, quantum and photonic computing, in- and near-memory computing, and computing in stretchable electronics.

- Finally, the Circuits Short Course

"Electronics That Drive the Next

Generation Smart Car" examined the electronics that will enable the next-generation smart

vehicle with presentations spanning hardware and software architecture, auto computing and

infotainment systems, connectivity, sensors, and battery management.

Forum Session: The Symposium program also featured a multi-speaker full day Forum Session on "VLSI for Infrastructure and Infrastructure for VLSI," held on Friday following the technical program sessions.

The VLSI Forum is devoted to a single topic that extends the scope of the current Symposia program, or explores emerging cutting-edge applications of VLSI. This year's forum focused on green mobility and smart semiconductor manufacturing, covering energy efficiency, security, communication, and big data, as well as technologies serving infrastructure.

In addition, three **Evening Panel Sessions** were held during the Symposium:

- "What Will It Take To Bring New Material From Lab To Manufacturing?"

- Robert Clark from Tokyo Electron moderated a panel of distinguished guests from across industry and academia to provide their valuable insights and thoughts, and share their experiences on this important topic. Questions included: How can we make sure the thousands of newly explored materials in academic, gov-

- ernment, and industry labs are relevant to manufacturing technologies? What are the fundamental factors to convert a success story to a technology transfer? Is there anything to be learned from history?

- "Building The 2030 WorkForce: How to Attract Great Students And What to Teach Them"

- Prof. Boris Murmann from Stanford University moderated a panel of experts from industry and academia to offer their insights and explore a critical challenge facing the semiconductor industry. With declining university enrollment in the semiconductor fields, and a shortage of skilled engineers across the industry, what can universities do to reverse the trend and ensure a robust workforce heading into 2030? What should the students learn to best prepare them for the industry's emerging needs?

- "Supply...Unchained? Will the Chip Shortage Continue?"

- This panel, moderated by Joe Macri from AMD, brought together industry experts representing viewpoints from leading foundries/IDMs, OSATs, fabless designers, materials suppliers, and equipment makers for a discussion on how the industry can come together to overcome the supply chain shortages. In addition, they addressed the topic of how the semiconductor industry landed in the current supply shortage, and what it will take to return to a healthy supply chain.

#### **Demonstration Session**

The popular in-person demonstration session was once again part of the Symposium program, after two years of virtual demonstrations. The session provided participants an opportunity for in-depth interaction with authors of selected papers from both Technology and Circuits sessions. These demonstrations, through table-top presentations, showcased device characterization, chip operational results, and potential applications for circuit-level innovations.

#### **Workshops**

A series of workshop sessions were held during the Symposium program to provide additional learning opportunities for participants. This vear's program included six workshops:

#### Technology Workshops

- Heterogeneous Integration—The Next Scaling Frontier: Material & **Process Challenges**

- Machine Learning Applications in Semiconductor Processes and **Equipment Development**

#### Circuit Workshops

- The Emerging Ecosystem of Open-Source Chip Design

- Analog/RF Circuits for IoT

Recent Advances in Radar. mmWave, and Sub-THz: Technology, Packaging, & Circuits

#### **Joint Workshop**

Cryogenic Electronics for Quantum Computing: covering scalable and reliable cryogenic electronics for quantum computing using a large number of aubits.

Special events at the Symposium included mentoring events for Women in Engineering and Young Professionals, sponsored by the IEEE Electron Devices Society and the Solid-State Circuits Society. The popular Joint Banquet/Luau was held on Wednesday evening, featuring Hawaiian music and dancing.

Best Student Paper Awards for each track Symposium are chosen each year based on the quality of the papers and presentations. The recipients receive a monetary award, travel cost support, and a certificate. For a paper to be reviewed for this award. the lead author and presenter of the paper must be enrolled as a full-time student at the time of submission, and must indicate on the web submission form that the paper is a student paper.

Further information about the Symposium is available at: http://www. vlsisymposium.org.

#### **Sponsoring Organizations**

The IEEE VLSI Symposium on Technology & Circuits is sponsored by the IEEE Electron Devices Society, in cooperation with the IEEE Solid-State-Circuits Society, and Japan Society of Applied Physics, in cooperation with the Institute of Electronics, Information and Communication Engineers.

#### Media Contacts

(North America and EU) BtB Integrated Marketing—Chris Burke, co-Media Relations Director E-mail: chris.burke@btbmarketing.com

(Japan and Asia) Secretariat for VLSI Symposia c/o JTB Communication Design, Inc. Tokyo, Japan E-mail: vlsisymp@jtbcom.co.jp

#### **EDS** is Celebrating the 75th Anniversary of the Transistor

Are you an EDS Forum Member or Chapter Chair and would like to hold an event to celebrate the 75th anniversary of the transistor? The IEEE Electron Devices Society is providing 75th-anniversary banners to any IEEE/EDS Forum Member or Chapter Chair that is holding an event to celebrate this important anniversary. Please submit the banner order form and we will ship a banner to you to display during your event. We ask that you also consider sending event photos/videos to eds@ieee.org for posting on EDS website, newsletter, and social media sites. A prize will be given for the best photo!

Order Form: https://ieeeforms.wufoo.com/forms/ s92tddv1kgbs7k/

#### UPCOMING TECHNICAL MEETINGS

# 2022 IEEE International Electron Devices Meeting (IEDM) to Showcase Breakthroughs in Semiconductors and Related Technologies

- The 2022 IEDM is planned as an in-person conference 3–7 December 2022 at the Hilton San Francisco Union Square Hotel, with on-demand access afterward for those unable to travel due to COVID-19 restrictions.

- The theme is "The 75th anniversary of the Transistor, and the Next Transformative Devices to Address Global Challenges," chosen to honor the industry's historic achievements while unveiling and exploring today's breakthroughs.

- IEDM 2022 will feature tutorials, short courses, focus sessions, an evening panel session, supplier exhibits, and a career-focused luncheon to complement the technical program.

- There will be three tracks of the increasingly popular tutorials this year, not just two.

"IEDM began shortly after the transistor was invented, in recognition of its revolutionary potential," said Srabanti Chowdhury, IEDM 2022 Publicity Chair, and Associate Professor of Electrical Engineering at Stanford University. "The breakthroughs described at the IEDM since then have pushed transistors and related technologies forward. This year, for example, many of the accepted papers indicate a growing interest in the use of 2D material systems for advanced devices."

"The broad reach, interdisciplinary nature and technical depth of the topics featured at the IEDM serve as a kind of crystal ball, be-

cause they show where the industry is placing its focus," said Jungwoo Joh, IEDM 2022 Publicity Vice Chair and Process Development Manager at Texas Instruments. "Many papers this year also deal with electrothermal considerations in extremely scaled devices, because reliability and thermal management go hand-in-hand."

#### **Plenary Talks**

IEDM 2022 will feature three Plenary talks on Monday, 5 December given by notable industry experts addressing some of the industry's most pressing issues. They are:

- Celebrating 75 Years of Transistor Innovation by Looking Ahead to the Next Set of Industry Grand Challenges, by Anne Kelleher, Executive Vice President/General Manager of Technology Development. Intel

- Expanding Human Potential through Imaging and Sensing Technologies, by Yusuke Oike, General Manager, Sony Semiconductor Solutions

- Enabling Full Fault-Tolerant

Quantum Computing with Sili con-Based VLSI Technologies, by

Maud Vinet, Quantum Hardware

Program Manager, CEA-Leti

#### **Evening Panel Session**

OnTuesday, 6 December there will be an evening panel session on the topic, 75 Years of Transistor Technology— (No) Time for Retirement? It will be moderated by Stefan De Gendt, Scientific Director at IMEC, and Suman Datta, Professor at Georgia Institute of Technology.

#### **Career Luncheon**

There also will be a career-focused luncheon on 6 December, featuring industry and scientific leaders talking about their personal experiences in the context of career growth. The speakers will be:

- Myung-hee Na, Vice President of SK Hynix's Revolutionary Technology Center

- Lisa Rutherford, Director of Research Science at Meta Reality

Labs Research

#### **Focus Sessions**

Among this year's technical highlights are five special Focus Sessions on key emerging technologies. They are:

#### Advanced Heterogeneous Integration: Chiplets and System-in-Packaging

Leading-edge integrated circuits have become so complex that it's difficult to add new features and achieve higher performance. Heterogeneous integration—where separately manufactured chips and chiplets (sub-processing units) are assembled into a single package in various ways—is an alternative.

Components having different functions can be built and optimized using the most appropriate technologies, and then combined into a unified circuit.

- Heterogeneous and Chiplet Integration Using Organic Interposer, S-P. Jeng et al, TSMC

- Hybrid Substrates for Chiplet Design and Heterogeneous Integration Packaging, J. Lau et al, **Unimicron Technology**

- Advanced System-in-Package Enabled by Wafer-Level Heterogeneous Integration of Chiplets, S. Bhattacharva et al. A\*Star

- Advanced Package FAB Solutions (APFS) for Chiplet Integration, S.W. Yoon, Samsung

- Advanced Substrate Packaging Technologies for Enabling Heterogeneous Integration (HI) Applications, G. Duan et al, Intel

- Advanced Packaging Technology Platforms for Chiplets and Heterogeneous Integration, L. Cao, **ASE**

#### **DNA Digital Data Storage**, Transistor-Based DNA Sequencing, and Bio-Computing

This Focus Session will feature papers at the intersection of computer science and biology. Some will explore the intriguing possibility of using DNA molecules as a potential data storage medium, because of DNA's extremely high density. Others will describe experimental nano-scale biosensors and related devices, which may lead to novel life-science technologies.

- Bacterial Nanopores Open the Future of Data Storage, M. Dal Peraro et al. EPFL

- DNA Storage: Synthesis and Sequencing Semiconductor Technologies, D. Lavenier, Univ. Rennes

- Wafer-Scale Biologically Sensitive Carbon Nanotube FETs: from Fabrication to Clinical Applications, Z, Zhang et al, Peking University

- System Design Considerations for Automated Digital Data Stor-

- age in DNA, C. Takahashi, Univ. Washington

- Single-Molecule Field-Effect Transistors: Carbon Nanotube Devices for Temporally Encoded Biosensing, K. Shepard et al, Columbia Univ.

- Advances in Electronic Nano-Biosensors and New Frontiers in Bioengineering, R. Bashir et al, Univ. Illinois Urbana-Champaign/Gachon Univ./Korea Univ./ Univ. California Irvine/Univ. Texas Austin

- The Nanopore-FET as a High-Throughput Barcode Molecule Reader for Single-Molecule Omics and Read-Out of DNA Digital Data Storage, P. Van Dorpe et al, IMEC/KU Leuven

#### **Emerging Implantable-Device Technology**

Researchers are investigating the use of advanced electronic technologies for new and improved implantable medical devices, in order to monitor and predict brain activity, to biodegrade after use, and for other purposes.

- Soft Wireless Optogenetic and Hybrid Implants for Advanced Neural Interfacing, J-W Jeong, **KAIST**

- Biodegradable Implantable Microsystems, J. Brugger et al, **EPFL**

- Bilayer-Nanomesh Transparent Neuroelectrodes on 10µm-Thick PDMS, J. Ryu et al, Dartmouth College/Northeastern Univ.

- Channels, Layout and Size Scalability of Implantable CMOS-Based Multielectrode Array *Probes*, L. Berdondini et al, Italian Institute of Technology

- The Future of Holistic Neural Interfaces: 2D Materials, Neuromorphic Computing, and Computational Co-Design, D. Kuzum et al, Univ. California San Diego

- Optogenetic Neural Probes: Fiberless, High-Density, Artifact-Free Neuromodulation, E. Yoon, Univ. Michigan

- A Transient, Closed-Loop Network of Wireless, Body-Integrated Devices for Autonomous Electrotherapy, J. Rogers, Northwestern Univ.

- Increasing the Lifetime of Implantable Neural Devices, S. Negi et al, Blackrock NeuroTech/Univ. Texas Dallas

#### Quantum Information and Sensing

Quantum sensing is the idea that sensors based on the properties of quantum mechanics (e.g., entanglement, coherence, tunneling, etc.) could be used to measure physical. electrical, magnetic, light and other quantities in ways that aren't possible otherwise. This may enable new technologies and ways of doing things, and papers in this Focus Session will discuss the fundamental work taking place to make various types of quantum sensors possible.

- Hybrid-Magnon Quantum Devices: Strategies and Approaches, A. Hoffmann, Univ. Illinois Urbana-Champaign

- Josephson Parametric Amplifiers for Rapid, High-Fidelity Measurement of Solid-State Qubits, S. Shankar, Univ. Texas at Austin

- Potential of Diamond Solid-State Quantum Sensors, M. Hatano et al, Tokyo Institute of Technology

- Rare Earth-Based Solid-State Qubit Platforms, S. Guha et al, Univ. Chicago/Argonne National Laboratory/MIT

- Spin Qubits in Silicon FinFET Devices, S. Paredes et al, IBM/Univ.

- Towards Topological Superconducting Qubits, J. Shabani et al, New York Univ.

#### Special Topics in Non-von **Neumann Computing**

Most computers are based on a socalled von Neumann architecture. named after computer pioneer John von Neumann, where a processor stores and fetches data from separate memory circuits, accessed with various input/output interfaces. With today's much faster processing speeds and denser chips, the inability of a processor to access memory quickly enough and at low power is becoming a serious limitation. Papers in this Focus Session will explore various ways to get around the "von Neumann bottleneck."

- Analog Compute-in-Memory For Al Edge Inference, D. Fick, Mythic

- Subthreshold Operation of SO-NOS Analog Memory to Enable Accurate Low-Power Neural Network Inference, S. Agrawal et al, Infineon/Sandia National Labs

- Multistable Neuromorphic Computing: Controlling Attractor Switches Using Waveforms, J.

- Chang et al, Univ. Texas at Austin

- Life is Probabilistic Why Should All Our Computers Be Deterministic? Computing with p-Bits: Ising Solvers and Beyond, B. Behin-Aein et al, Ludwig Computing

- Energy-Efficient Activity-Driven Computing Architectures for Edge Intelligence, S-C Liu et al, Univ. Zurich

- Training-to-Learn with Memristive Devices, E. Neftci et al, Peter Grunberg Institute

- Ferroelectric FET Configurable Memory Arrays and Their Applications, S. X. Hu et al, Notre Dame/ De La Salle Univ. /Univ.

South Florida

Scalable In-Memory Computing Architectures for Sparse Matrix Multiplication, J. Kendall et al, Rain Neuromorphics/Univ. Florida/Sandia National Laboratory

Visit https://www.ieee-iedm.org/ registration-overview to register for IEDM 2022.The deadline for early registration rates is 22 November 2022.

> Gary Dagastine Dagastine & Co. PR gdagastine@nycap.rr.com

Chris Burke BtB Marketing Communications chris.burke@btbmarketing.com

## 7<sup>th</sup> IEEE Electron Devices Technology and Manufacturing (EDTM) Conference

7–10 March 2023/COEX, Seoul, Korea https://ewh.ieee.org/conf/edtm/2023/

The 7th IEEE Electron Devices Technology and Manufacturing Conference (EDTM 2023) is a full four-day conference to be held in Seoul, Korea. EDTM is a premium conference sponsored by the IEEE Electron Devices Society that provides a unique forum to discuss and collaborate on a broad range of device/manufacturing-related topical areas including materials, processes, devices, packaging, modeling, reliability, and manufacturing and yield. The 7th EDTM will be held with the main theme: "Strengthen the global semiconductor research collaboration beyond the COVID-19 pandemic era."

The **Plenary** speakers include Dr. Suman Datta (Georgia Tech), Dr. Seon Yong Cha (SK Hynix), Dr. Jong Myeong Lee (Samsung Electronics), and Dr. Michael Lercel (ASML).

#### **Technical Sessions**

The EDTM 2023 solicits papers in all types of exploratory device concepts within the following broad technical areas:

- Materials

- Process, Tools, Yield, and Manufacturing

- Semiconductor Devices

- Memory Technologies

- Photonics, Imaging and Display

- Power and Energy Devices

- · Modeling and Simulation

- Reliability

- Packaging and Heterogeneous Integration

- Sensor, MEMS, Bio-Electronics

- Flexible and Wearable Electronics

- Nanotechnologies

- Disruptive Technologies IoT, Al/ ML, Neuromorphic & Quantum Computing

#### **Publications**

Submitted papers will be subjected to IEEE standard review processes and publishing guidelines, as well as EDTM 2023 review criteria. The

accepted and presented papers will be included in the EDTM 2023 Proceedings (Camera-Ready at submission and to be published AS IS if accepted), which will be published in IEEE Xplore. The authors of selected high-impact papers will be invited to submit extended versions for possible publication in the Special Issue on EDTM 2023 in IEEE Journal of Electron Devices Society (J-EDS), subjected to J-EDS author guidelines, and standard IEEE review and publication policy.

#### **Short Courses and Tutorials**

EDTM 2023 will start with a set of short courses and tutorials on 7 March 2023. Tutorials teach selected topics from the basics to the state-of-the-art, allowing the attendees to catch up on a topic quickly. Short Courses discuss the latest research and challenges on hot and advanced topics encompassing the EDTM 2023 theme. EDTM 2023 will offer 3 Short Courses on advances in manufacturing and processing

technologies, CMOS Image Sensor technology, power and energy devices, and 3Tutorials on innovation technology for advanced semiconductor manufacturing, a new paradigm for high-efficiency computing, packaging, and heterogeneous integration.

#### **Important Dates**

Paper Submission Deadline: 24 October 2022 Notification of Acceptance: 23 December 2022 (tentative) Early Registration Deadline: 10 February 2023 (tentative)

On behalf of the EDTM 2023 Organizing Committee, we invite you to join us in Seoul.

> Miso Kim EDTM 2023 Publicity Chair

#### 2023 IEEE International Reliability Physics Symposium (IRPS)

The IEEE International Reliability Physics Symposium (IRPS) is the world's premier forum for leadingedge research addressing developments in the Reliability Physics of devices, materials, circuits, and products used in the electronics industry. IRPS is the conference where emerging reliability physics challenges and practical solutions to achieve realistic end-of-life projections and mitigation are first discussed.

In 2023, the IRPS will be held on 26-30 March at the Hilton, Monterey, California. Over the course of the conference, IRPS will offer a blended mix of keynote talks, tutorials, yearin-reviews, workshops, vendor exhibits, and technical presentations. Abstracts are due by 24 October 2022. Late breaking news submissions are welcome by 23 January 2023.

The IRPS draws presentations and attendees from industry, academia and governmental agencies worldwide. No other meeting presents as much leading work in so many different areas of reliability of electronic devices, encompassing silicon device, non-silicon device, process technology, nanotechnology, optoelectronics, photovoltaic, MEMS technology, circuits and systems reliability including packaging. IRPS 2023 is soliciting increased participation in the following areas: Embedded/In-product memory/neuromorphic compute,

GAA, nanosheet, RibbonFET™, Forksheets, 3D IC advanced packaging.

IRPS 2023 will be kicked off by keynote presentations from reliability experts at Intel, AMD, and Ampere covering the latest reliability trends and mitigation approaches from various industry perspectives.

Further opportunities at the symposium include:

Tutorial Program. The IRPS tutorial program is a comprehensive

event designed to help both the new engineers and experienced researchers. The program contains both beginner and expert tracks and is broken down into topic areas that allow the attendee to participate in tutorials relevant to their work with minimal conflicts between subject areas.

Year-in-Review Session. These seminars provide a summary of the most significant developments in the reliability community over the past year. This serves as a convenient, single-source of information for attendees to keep current with the recent reliability literature. Industry and academic experts serve as the "tour guides" and save you time by collecting and summarizing this information to bring you up to

Ann Kelleher Executive Vice President and General Manager of Technology Development, Intel

Mark Fuselier Senior Vice President, Technology & Product Engineering, AMD

Rohit Vidwans Executive Vice President and Chief Engineering & Manufacturing Officer, Ampere

- date in a particular area as efficiently as possible.

- Poster Reception. The poster session provides an additional opportunity for authors to present their original research. The setting is informal and allows for easy discussion between authors and other attendees.

- Workshops. These workshops enhance the symposium by providing the attendees an opportunity to meet in informal groups to discuss key reliability physics topics with the guidance of experienced moderators. Some of the workshop topics are directly coupled to the technical program to provide a venue for more discussion on the topic.

- Vendor Exhibits. Held in parallel with the technical sessions, the equipment demonstrations provide a forum for manufacturers of state-of-the-art laboratory equipment to present their products. Attendees are encouraged to visit the manufacturers' booths for information and demonstrations.

- IRPS Paper Awards. IRPS bestows awards for Best Paper, Best Student Paper, Best Posters, and People's Choice.

- IEW Co-Location. In 2023, the IRPS will be co-located with the International ESD Workshop (IEW). Now in its 16<sup>th</sup> year, the IEW provides a relaxed, invigorating atmosphere to present new work and engage in dis-

cussions about the latest issues confronting the ElectroStatic Discharge (ESD) and Electrostatic OverStress (EOS) communities.

For the call for papers and other information, visit the IRPS 2023 home page at www.irps.org or join the IRPS linked-in group.

The IRPS committee members look forward to seeing you in Monterey, California!

Chris Conner 2023 IRPS General Chair Intel

Paula Chen 2023 IRPS Publicity Chair AMD

## 24th International Vacuum Electronics Conference (IVEC 2023)

On behalf of the IVEC 2023 Organizing Committee, we are pleased to announce that the Twenty-Fourth International Vacuum Electronics Conference (IVEC 2023), organized and sponsored by the University of Electronic Science and Technology of China (UESTC) with the technical co-sponsorship of the IEEE Electron Devices Society (EDS), will be held on-site in Chengdu, Sichuan Province, China, on 25-28 April 2023. Chengdu is known as the hometown of pandas, and we sincerely expect all attendees to fully interact with each other while immersing themselves in the natural beauty of Southwest China.

IVEC 2023 aims at being an international forum of information and technical discussion among various players in the fields of vacuum electronics: designers, researchers, young and experienced engineers, scientists, device users, manufacturers, operators, government/institutions, academics and of course, our valuable students.

We invite you to submit papers with the results of your latest work and experiences in the field of vacuum electronics. Submissions from all groups are highly encouraged and appreciated. IVEC 2023 strives to provide a unique platform for exchanging scientific and technical information and foster collaboration and cooperation in the vacuum electronics domain at Asian and global levels.

IVEC 2023 will focus on the Development of Vacuum Electronics for Requirements of the 21st Century as the conference theme. A special highlight of IVEC 2023 will be the introduction of Generalized Vacuum Electronics, which will try to extend the electron radiation from traditional vacuum

to solid-state materials, as well as combine vacuum technology with the semiconductor technology. IVEC 2023 is the ideal forum to present and discuss the promising research from this field with the wider vacuum electronics community.

The John R. Pierce Award for Excellence in Vacuum Electronics, the Vacuum Electronics Young Scientist Award and the Best Student Paper Award will be presented.

For more details and the most up-to-date information, please visit the conference website at https://ivec2023.org.

We hope to see you all in Chengdu or online for IVEC 2023.

Yubin Gong IVEC 2023 Chair University of Electronic Science and Technology of China ivec2023@ivec2023.org

#### SOCIETY NEWS

#### EDS STRATEGIC PLANNING

As you may know, the Strategic Planning Workshop was completed in June and I am very pleased to announce that it successfully completed its charter. There is now a Strategic Plan proposal which will be presented to the EDS Board of Governors and Forum for adoption. The Plan has five major components. In this article I would like to share the first three components with you. The Mission and Vision are the ones with which you are familiar. They have been on EDS website for quite some time. The Workshop delegates affirmed these with no major changes.

#### Mission

To foster professional growth of its members by satisfying their needs for easy access to and exchange of technical information, publishing, education, and technical recognition while enhancing public visibility in the field of Electron Devices.

#### Vision

Promoting excellence in the field of electron devices for the benefit of humanity.

The third component consists of five adjectives which describe the EDS Core Values. It was proposed by the EDS Executive Committee and adopted by the delegates. They articulate the human values of the Society as lived today and endure but which are distinct from what it aspires to be. They describe what anyone should expect who interacts with us and when we interact with each other.

#### **Core Values**

- · trustworthy.....we are honest and transparent; we keep our word

- respectful......we are civil, courteous and polite in our actions and discourse

- inclusive.....we seek full engagement from all members; we exclude no one; there are no ranks

- ethical.....we do nothing to harm individuals or the environment: we follow the law

- open.....we are listen to new ideas; we are aware of and adapt to change

The Strategic Plan is a dynamic plan which thrives when all members live its core values and participate in the realization of its vision and mission. Your role in this is vital. That is why I am calling on you to exemplify our core values in your professional life and to engage in a dialog with us about what the Society can do for you and what you can do to make our vision and mission come to life.

We need your feedback. You are the important ingredient for making this successful. Please go to: https://ieee-collabratec.ieee.org/app/ workspaces/8209/Electron-Devices-Society-Strategic-Plan/activities. You can log on with your IEEE credentials or simply register as a Collabratec user at no cost. Do it today.

> Doug Verret Strategic Directions Committee Vice President

#### Message from EDS Newsletter Editor-in-Chief

Daniel Tomaszewski EDS Newsletter Editor-in-Chief

Dear Readers. Members of the IEEE EDS Community,

Welcome to the IEEE EDS Newsletter issue October 2022. Let me briefly introduce to you the contents.

The Society News section brings you this time an interesting report by Monica Blank, Chair of EDS Vacuum Electronics Technical Committee. The article is illustrated by an exceptional picture of just how large electron devices are in the field of interest of the Society.

We continue the series of articles celebrating the 75th Anniversary of Transistor. In this issue, Prof. John

D. Cressler overviews developments of the SiGe HBTs, and Prof. Dan Fleetwood highlights Radiation Effects in scaled MOS Devices.

In the Technical Briefs section we offer a summary of the 2022 IEEE VLSI Symposium on Technology & Circuits, fully combined as a single event. Moreover, in Regional News we present short reports on recent editions of the International Memory

Workshop and Latin America Electron Devices Conference. What concerns the future, we present in the Upcoming Technical Meetings section the last update on IEEE International Electron Devices Meeting, and the advertisements of IEEE Electron Devices Technology and Manufacturing Conference, International Vacuum Electronics Conference, and International Reliability Physics Symposium. The upcoming editions of IEEE Workshop on Wide Bandgap Power Devices & Applications, International Memory Workshop, International Symposium on Power Semiconductor Devices and ICs are announced in Regional News.

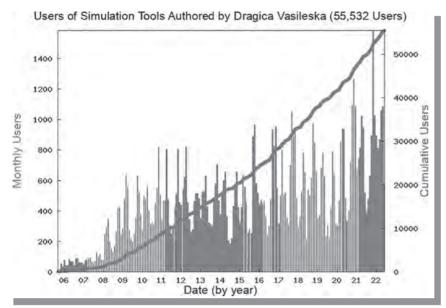

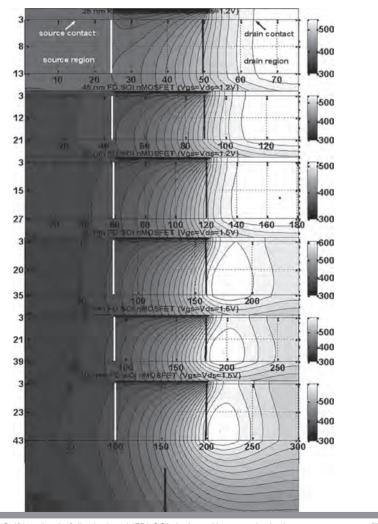

In the Women in Engineering section, please find the article by Prof. Dragica Vasileska who presents her career as a researcher and teacher in the area of computational electronics. The Young Professionals section contains an interesting article by Prof. Paul Berger who tells us how he has used the IEEE Collabratec platform for mentoring young people starting or willing to start their professional careers in the Electron Devices discipline. Based on his own positive experience. Paul encourages experienced members of the Society to try sharing their own experience and expertise with young people. It is a key message of this article.

Further parts of this Newsletter issue include news on technical, societal and humanitarian activities led by the Chapters in Regions 2, 8, 9, and 10. At this point, I would like to welcome in our Newsletter the IIITDM-Kancheepuram, ED15 Student Branch Chapter. This SBC was established very recently and now reports its first activities. Congratulations to the Chapter members, the Branch Advisor Dr. Pradhan and Chair Mr. Chandrasekar!

#### Mykhaylo Andriychuk

After a short presentation of the Newsletter content I would like to introduce to you Mykhaylo Andriychuk (IEEE M'95. SM'03) who

has been appointed as the EDS Newsletter Regional Editor for Region 8 - Eastern Europe after Kateryna Arkhypova's stepping down from this position. We, the whole EDS Newsletter Editorial Team, are grateful to her for dedication in voluntary work for EDS and wish her dreams come true. Dr. Andriychuk has been employed by the Pidstryhach Institute for Applied Problems of Mechanics and Mathematics (IAPMM), Lviv, Ukraine, for more than 40 years. Currently, he is the Head of

Department of the Numerical Methods in Mathematical Physics. He also holds a position of professor at the National University "Lviv Polytechnic", Lviv, Ukraine. His professional performance includes more than 180 papers in the scientific journals and international conference proceedings, which concern the diffraction and antenna synthesis theory, optimization methods and nonlinear integral and matrix equations. Dr. Andriychuk served for a long time as the IEEE Ukraine Section (West) MTT/ED/AP/EP/SSC Societies Joint Chapter Chairman. That time, the Chapter won the IEEE Antennas and Propagation, Electron Devices, and Microwave Theory and Techniques Societies Outstanding Chapter of the Year Awards. We are very glad to welcome Mykhaylo in our team and we wish him fruitful work for the EDS Newsletter.

Dear Readers, if you have any suggestions, comments regarding the Newsletter contents, please do not hesitate to contact us. We will be very glad to receive your feedback. Interesting views will be presented with the consent of the authors, along with our replies in the Letters to Editors section.

Sincerely, Daniel Tomaszewski

#### EDS VACUUM ELECTRONICS TECHNICAL COMMITTEE REPORT

The EDS Vacuum Electronics Technical Committee (VETC) was formed more than 20 years ago to represent the vacuum electron device community within EDS. The Committee has 11 members and 15 corresponding members, all of whom are world-recognized experts in one or more technical disciplines related to vacuum electronics. In addition to overseeing the International Vacuum Electronics Conference (IVEC) and

supporting EDS journals, the Committee works to promote and foster emerging technologies, new applications, and cutting-edge research in the broad field of vacuum electronics. With the Committee members from the academia, industry, and government labs in Asia, Europe, and North America, the VETC seeks to represent and advocate for the worldwide vacuum electronics community.

The dynamic, challenging, multidisciplinary field of vacuum electronics represented by the Committee continues to advance, evolve, and grow. Scientists and engineers working in the field of vacuum electronics seek to develop and exploit the most up-to-date technology, design tools, and design techniques to continuously advance the state-of-theart. As applications require vacuum electronic devices with progressively better performance, including higher power, higher frequencies, broader bandwidths, higher gains, and longer lifetimes, the Committee actively promotes the research and development to ensure that the technology continues to meet ever growing application demands.

The VETC is also responsible for selecting yearly winners of the John R. Pierce Award for Excellence in Vacuum Electronics as well as the Vacuum Electronics Young Scientist (VEYS) Award. Each year, these two awards are presented at IVEC, where the winners have the opportunity to deliver plenary addresses. The 2022 Pierce Award Winner, Dr. Keishi Sakamoto from Kyoto Fusioneering, gave at IVEC 2022 an enthusiastic and inspiring plenary address on how the continuous wave gyrotrons performance improvements at the megawatt power level, have moved electron cyclotron resonance heating from a lesser role to the main heating method for ITER and other groundbreaking fusion machines. The 2022 VEYS Award winner, Dr. Diana Gamzina from SLAC and Elve, delivered a career retrospective talk highlighting the most impressive of her numerous technical accomplishments as well as her establishment and oversight of the SLAC Accelerating Girls' Engagement in STEM (SAGE-S) program. Please join the VETC in congratulating Dr. Sakamoto and Dr. Gamzina, two extremely accomplished and deserving award winners, who represent the best our field has to offer.

Last year, the Committee's main areas of focus were the successfully concluded IVEC 2022, the upcoming IVEC 2023, a special issue of the IEEE Transactions on Electron Devices, and an updated technical Committee

Monica Blank, Chair of VETC, standing next to a 170 GHz, 1 MW power level gyrotron oscillator

website. IVEC 2022, the first hybrid in-person and online meeting in the IVEC series, was held in Monterey, CA, in April under the guidance of Dr. Jack Tucek of Northrop Grumman Corporation, the General Chair, and Technical Program Chair Dr. Max Mankin of Modern Electron Corporation. The meeting was comprised of 257 invited and contributed papers, 6 plenary and award talks, and a very well-received mini course with lectures on the basics of TWT amplifiers, additive manufacturing for vacuum electronics, thermionic converters, as well as ultrafast and ultra-small scale electron emission. Despite the inherent challenges of a hybrid meeting, the 23rd IVEC, along with the mini course, was a huge success, with higher than typical attendance and outstanding technical content.

Prof. Yubin Gong of UESTC, the general chair of IVEC 2023, and his co-chairs, Prof. Yirong Wu of AIR-CAS, Prof. Detian Li of LIP-CAST, and Prof. Jinjun Feng from BVERI, are well ahead in the planning process for next year's IVEC. The hybrid conference will take place from 25-28 April 2023, with the in-person component held in Chengdu, China. Details about the conference can be found at https://ivec2023.org. Please visit the conference website for the latest information about this exciting upcoming meeting. We hope to see all of you in Chengdu or online for IVEC 2023.

The VETC has also been focused on the upcoming Special Issue in the IEEE Transactions on Electron Devices, entitled "From Mega to Nano: Beyond One Century of Vacuum Electronics." The submission deadline for the Special Issue is October 31, 2022 and publication is planned for June 2023. All are invited to submit manuscripts to this timely and relevant Special Issue.

Details about the Special Issue of TED, the 2023 IVEC, the John R. Pierce and VEYS awards, and much more can be found at the newly updated Committee website, https:// vacuumelectronics.org. We invite everyone to visit the website for all the latest news and information about the vibrant and exciting vacuum electronics community.

> Monica Blank Chair of EDS Vacuum Electronics Technical Committee

#### JOIN 2 OR MORE IEEE SOCIETIES AND SAVE 5%

As an IEEE Electron Devices Society member, you can take advantage of the Multiple Society Discount Program to connect across several IEEE Societies to expand your expert network and collaborate on the latest cutting-edge technical research, policy, and innovation at a discount when you become a

member or renew your membership of two or more participating IEEE Societies.

If you're already a member of two or more participating IEEE Societies, the discount will automatically be applied when you renew. If you've always been interested in a complementary IEEE Society, this program provides you with the opportunity to join at a discounted rate.

The IEEE Societies that complement the IEEE Electron Devices Society include IEEE Solid-State Circuits Society, IEEE Circuits and Systems Society, IEEE Photonics Society and IEEE Reliability Society.

**♦IEEE**

Multiple Society Discount Program

INTERACT, DEVELOP, INFLUENCE

#### **New Lower IEEE Dues for Undergraduate Students**

New lower student dues in developing nations and lowincome economies will make undergraduate student membership more affordable and will be automatically priced for eligible students in these countries. NO promotion code is needed, but also, no other discounts or promotions can be applied in combination with the new lower dues. In developing nations, undergraduate student dues will be US\$14. In low-income economies, dues will be US\$5.

View the list of eligible countries, https://www.ieee.org/membership/join/emember-countries.html.

Graduate student members in all countries will not see any change in their membership dues and will remain at US\$32 or US\$27, but they will still be ale to use the IEEE FUTURE50 discount.

Thousands of student members are owning their futures and preparing to be the best in their industries by using their IEEE network to collaborate, compete, and learn - be sure you're one of them! Save 50% on IEEE Student membership! Add IEEE Electron Devices Society (EDS) for only \$5.00 more!

#### **IEEE Day is 4 October 2022**

Connect with IEEE members thru the many global events: **ieeeday.org**

Join us in celebrating IEEE Day which commemorates the first time IEEE members gathered to share their technical ideas in 1884.

Join our IEEE Day Community http://bit.ly/IEEEDayCommunity

## Join IEEE and Save \$30

#### For New Professionals Only, Not for Student

**Membership.** Expand your network by becoming part of the world's largest technical community leveraging technology for a better tomorrow!

Join IEEE between 1 October and 18 October 2022 and receive US \$30 off your first year of membership!

Recruiter Name:

Recruiter Member #:

#### To join IEEE and receive the discount:

**1.** Join by 18 October to receive this special discount and get two months free: **ieee.org/join**

Use promotion code IEEEDAY2230

- **2.** Fill in the name and member number of the member who referred you (if applicable).