APRIL 2014 VOL. 21, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

#### TABLE OF CONTENTS

| Upcoming Technical Meetings                                                                              |

|----------------------------------------------------------------------------------------------------------|

| <ul> <li>2014 IEEE Symposium on VLSI Technology</li> </ul>                                               |

| <ul> <li>2014 IEEE Compound Semiconductor IC<br/>Symposium (CSICS)</li> </ul>                            |

| • 2014 IEEE International Memory Workshop (IMW)                                                          |

| <ul> <li>2014 IEEE International Symposium on Power<br/>Semiconductor Devices and ICs (ISPSD)</li> </ul> |

| Technical Briefs 6                                                                                       |

| <ul> <li>Semiconductors and Power Electronics in the<br/>21st Century</li> </ul>                         |

| <ul> <li>UCSB Researchers Take Carbon Nanotube<br/>Interconnects Closer to Reality</li> </ul>            |

| <ul> <li>2013 IEEE International Electron Devices<br/>Meeting—Summary</li> </ul>                         |

| • 2014 IEEE IRPS—Technical Program Highlights                                                            |

| Society News12                                                                                           |

| Message from Editor-in Chief                                                                             |

| <ul> <li>December 2013 EDS Board of Governors (BoG)<br/>Meetings</li> </ul>                              |

| <ul> <li>Announcement of Newly Elected Officers and BoG<br/>Members</li> </ul>                           |

| <ul> <li>Summary of Changes to the EDS Constitution<br/>and Bylaws</li> </ul>                            |

| <ul> <li>Report on the VLSITechnology and Circuits<br/>Committee Meeting</li> </ul>                      |

| <ul><li>IEEE Fellow and Senior Member News</li><li>2013 Award Winners</li></ul>                          |

| • 2014 Award Call for Nominations                                                                        |

| Young Professionals                                                                                      |

| Latest EDS Webinar — New Requirements for the CEC's Eligible Solar Electric Equipment     Quest EDS      |

| Chapter News                                                                                             |

| Regional News33                                                                                          |

|                                                                                                          |

# VLSI TECHNOLOGY

2014 IEEE SYMPOSIUM ON

Rainbow Tower, Hilton Hawaiian Village, Honolulu, Hawaii, USA

The 34th Annual IEEE Symposium on VLSITechnology will be held from June 9–12, 2014, at Hilton Hawaiian Village, Honolulu, Hawaii. This symposium, jointly sponsored by the IEEE Electron Devices Society and the Japan Society of Applied Physics, is the premier international conference on **VLSI** semiconductor technology.

The unique aspect of this conference is that it is held jointly with the Symposium on VLSI Circuits (June 10th–13th) to promote interactions between technologists and circuit/system designers. A single registration fee covers both events, and **special joint focus sessions** will offer unique learning opportunities for both Technology and Circuits attendees on "Design in Scaled Technologies," "Design Enablement," "Memory Technology & Design" and "3D (TSV) & Heterogeneous Integration."

Moreover, the 2014 Symposium on VLSI Technology features technology focus sessions on "Non-Volatile Embedded Memory" and "Interconnect: Local & Global," and research results spanning a broad spectrum of VLSI technology topics:

(continued on page 5)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

## ELECTRON DEVICES SOCIETY

#### President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### President-Elect

Samar Saha Ultrasolar Technology E-mail: samar@ieee.org

#### **Treasurer**

Ravi M. Todi Qualcomm Technologies, Inc. E-mail: rtodi@ieee.org

#### Secretary

Fernando Guarin IBM Microelectronics E-mail: guarinf@us.ibm.com

#### Jr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

#### Sr. Past President

Renuka P. Jindal University of Louisiana at Lafayette E-mail: r.jindal@ieee.org

## Vice President of Membership and Services

Mikael Ostling

KTH, Royal Institute of Technology E-mail: mostling@kth.se

## Vice President of Publications and Products

Bin Zhao Fairchild Semiconductor E-mail: bin.zhao@ieee.org

#### Vice-President of Regions/ Chapters

Xing Zhou

Nanyang Technological University E-mail: exzhou@ntu.edu.sg

## Vice President of Technical Committees & Meetings

Leda Lunardi North Carolina State University E-mail: leda lunardi@ncsu.edu

#### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

#### **Executive Director**

Christopher Jannuzzi IEEE Operations Center E-mail: c.jannuzzi@ieee.org

#### Membership Administrator

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| <u>2014</u>                                                                                                 | TERM                                                 | <u>2015</u>                                                                              | TERM                                          | <u>2016</u>                                                                                      | TERM                                          |

|-------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Z. Celik-Butler<br>M. Chan<br>S. Chung<br>S. Deleonibus<br>F. Guarin<br>T.L. Ren<br>S. Saha<br>E. Sangiorgi | (1)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2)<br>(1) | D. Camacho<br>S. S. Iyer<br>M. Meyyappan<br>A. Nathan<br>M. Shur<br>D. Verret<br>B. Zhao | (1)<br>(2)<br>(2)<br>(2)<br>(2)<br>(1)<br>(2) | A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) |

### NEWSLETTER EDITORIAL STAFF

#### **Editor-In-Chief**

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Fernando Guarin IBM Microelectronics E-mail: guarinf@us.ibm.com

## Central USA & Canada (Regions 4 & 7)

Peyman Servati University of British Columbia E-mail: peymans@ece.ubc.ca

## Southwestern & Western USA (Regions 5 & 6)

Adam M. Conway Lawrence Livermore Nat. Lab. E-mail: conway8@llnl.gov

#### Latin America (Region 9)

Francisco J. Garcia Sanchez University Simon Bolivar E-mail: fgarcia@ieee.org

## REGION 8 Eastern Europe & the former

Soviet Union

Tomislav Suligoj

University of Zagreb

University of Zagreb E-mail: tom@zemris.fer.hr

#### Scandinavia & Central Europe

Zygmunt Ciota Technical University of Lodz E-mail: ciota@dmcs.pl

#### UK, Middle East & Africa

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky

Abb Switzerland Ltd.

E-mail: vobecky@fel.cvut.cz

#### **REGION 10**

## Australia, New Zealand & South Asia M.K. Radhakrishnan

NanoRel E-mail: radhakrishnan@ieee.org

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Mansun J. Chan Hong Kong Univ. of Sc. & Tech. E-mail: mchan@ust.hk

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editor-in-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

#### **NEWSLETTER DEADLINES**

| ISSUE   | <u>Due Date</u> |

|---------|-----------------|

| January | October 1st     |

| April   | January 1st     |

| July    | April 1st       |

| October | July 1st        |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2014 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

## UPCOMING TECHNICAL MEETINGS

## 2014 IEEE COMPOUND SEMICONDUCTOR IC Symposium (CSICS)

We cordially invite you to the 2014 IEEE Compound Semiconductor IC Symposium (CSICS) being held October 19th-22nd at the Hyatt Regency La Jolla at Aventine located in San Diego, California USA. The Symposium has evolved to be the pre-eminent international forum for developments in compound semiconductor circuit and device technology. The scope of the Symposium encompasses devices and circuits, embracing GaAs, SiGe, InP, GaN, InSb and CMOS technology to provide a truly comprehensive conference. CSICS is the ideal forum for presenting the latest results in microwave/mm-wave, high-speed digital, analog, mixed mode, THz, power conversion, and optoelectronic integrated circuits.

The 2014 CSIC Symposium comprises of a full 3-day technical program, two short courses, a primer

course, and a technology exhibition. The technical program consists of approximately 60 high quality technical papers. Invited papers and 2-4 panel sessions on topics of current importance to the Compound Semiconductor

IC community are key components of the technical program. In addition, the Symposium will continue the tradition of including important "late breaking news" papers. The short courses on Sunday, October 19th provide the attendees the opportunity to learn from world-renowned instructors in their respective areas of expertise. The Sunday introductory-level primer course will provide attendees insight into

the design of the principal RF building blocks, namely PAs, LNAs, Mixers and Oscillators, emphasizing the specific background to understand and appreciate the technical program.

The technology exhibition will be held on

Monday and Tuesday, featuring informative and interesting displays with corporate representatives on hand. The list of exhibitors can be found in the CSICS advance program to be published in late June. To complement the Symposium, there are several social events including the Sunday Evening CSICS Opening Reception, the Monday CSICS Exhibition Opening Reception, and the Tuesday CSICS Exhibition Luncheon. Breakfasts and coffee breaks will be served on Monday, Tuesday, and Wednesday.

For registration and up-to-date information please visit the CSICS website at www.csics.org. Further questions may be addressed to the Symposium Chair: Douglas S. McPherson, Ph: +1 613-670-3371, Email: dmcphers@ciena.com

Paper Submission Deadline: May 2, 2014

> For 2014 IEEE CSICS Organizing Committee Brian Moser 2014 CSICS Publicity Chair RFMD, Greensboro, NC, USA

### 2014 IEEE INTERNATIONAL MEMORY WORKSHOP (IMW)

## THE SIXTH IEEE INTERNATIONAL MEMORY WORKSHOP WILL BE HELD AT THE REGENT TAIPEI, TAIWAN, MAY 18-21

In response to the growing global interest in memory technologies, NVSMW-Non Volatile Semiconductor Memory Workshop-and ICMTD—International Conference on Memory Technology and Design-were merged together in 2008 to incorporate the volatile and non-volatile memory aspects in one forum while maintaining the workshop experience. The workshop is sponsored by the IEEE Electron Devices Society and meets annually in May. In 2014, IMW goes back to Asia and will be held in Taipei, Taiwan.

The convergence of consumer, computer and communication electronic systems is leading to an exponential growth in need, mainly for code, computing and data storage. While in the past we could associate a memory technology to a specific market segment (e.g., RAM to computer, NOR Flash to mobile communication, NAND Flash to consumer SSD), today the new electronic systems stack different memory technologies and use microcontroller to facilitate interfacing and managing the overall memory. Moreover, novel memory technologies are entering in the market, providing opportunities for novel applications and challenges for the technology development. The characteristics of these complex memory systems in terms of density, performance, power consumption, packaging and interfacing become of greater interest. The capabilities provided by the new memory technologies, new concepts and material proposed today will drive the definition of these memory systems in the future. The IMW aims to answer this need, extending the scope from non-volatile memory, which had been successfully discussed in more than 30 years of NVSMW's history, to large memory technologies and design, which were the focus of ICMTD, in the view of systems. Innovation is our tradition: IMW widened its focus while maintaining the positive characteristics of a workshop.

IMW is a unique forum for both specialists in all aspects of microelectronic memory and novices wanting to gain a broader understanding of the field. The workshop is usually attended by a wide international community from North America, Europe, Japan and Asian countries. Attendees include industry leaders, researchers in academia and industry as well as end users of memory products. The number of attendees typically exceeds 250 in recent years, reflecting the growing interest in the workshop. Each year we receive over 80 paper submissions and accept about 35 for oral presentation which corresponds to about 40% acceptance rate. Principal topics for discussion are: device physics, silicon processing, product testing, new technologies including new structures and novel approaches, programmable logic, memory cell design, integrated circuits, solid state disks and memory cards, reliability and new applications. Following the tradition established in previous IMW editions, Sunday the 18th of May will be dedicated to a Short Course session. Moreover a poster session for several qualified papers is usually held after the panel discussion.

An important goal of IMW is to provide an informal environment to encourage discussions among participants and lively interactions. There will be morning and afternoon technical sessions, along with a lively evening panel discussion on a hot topic in memory field. Technical interaction among presenters and attendees is encouraged through question and answer sessions and allotting ample time after formal paper presentations for further in-depth discussions. Organized breaks, including snacks and the conference dinner and lunch are provided as opportunities to meet and exchange ideas with colleagues. The morning and afternoon technical sessions are organized in a manner of providing time for the informal exchange and to enjoy the beauty of the Taipei area. The hotel is conveniently situated in Taipei downtown and it is easily accessible from the international airport. Taipei is the gateway to visit Taiwan with high-speed train connections. For more information about the conference, please go and register at the website www.ewh. ieee.org/soc/eds/imw. I look forward to seeing you next May at IMW 2014 in Taipei.

> Agostino Pirovano 2014 IMW General Chair Micron Agrate Brianza (MB), Italy

## 2014 IEEE INTERNATIONAL SYMPOSIUM ON POWER SEMICONDUCTOR DEVICES AND ICS (ISPSD)

The International Symposium on Power Semiconductor Devices and ICs (ISPSD) brings together the world's foremost experts on power devices and power integrated circuit technologies and applications. It has become the premier international conference in this field, drawing an annual attendance of about 400 engineers, scientists, students, and professors.

In 2014, ISPSD will return to Hawaii for the first time in nearly 20 years. The conference will be held on the beautiful Big Island of Hawaii, which includes two active volcanoes, beautiful beaches, abundant hiking, snorkeling, and many other outdoor adventures.

ISPSD 2014 will open with an allday short-course lecture series on

June 15th with six exciting topics. This is followed by four full days of technical sessions (June 16th-19th). A total of 110 oral and poster technical papers will be presented. Sessions will run sequentially, with no parallel sessions, enabling participants to listen to, and to ask questions for, every presenter. Frequent breaks will be provided and several social events are planned (including a genuine Hawaiian Luau) to allow conference attendees to network and exchange ideas in an informal setting. In addition, exhibitors' booths will provide an opportunity for participants to learn about the equipment and services of companies that support the power electronics industry.

We have received a significant increase in paper submission this year. The organizing and technical program committees are working hard to ensure that this conference will be a success. The most important factors in that success will be the high-quality technical presentations and the participation of power device enthusiasts from all over the world. Registration is open at www.ispsd. org. Please register early, and help us to make ISPSD 2014 a valuable and memorable experience for all.

> Don Disnev 2014 ISPSD General Chair GlobalFoundries Santa Clara, CA, USA

### 2014 IEEE SYMPOSIUM ON VLSI TECHNOLOGY

(continued from page 1)

- Logic, Memory, RF, analog, I/O, high-voltage, imaging, MEMS, integrated sensors, and Systemon-Chip

- New materials, concepts and breakthroughs in VLSI processes and devices

- Interconnect scaling and Cu alternatives; chip-to-chip interconnects

- Heterogeneous integration of non-Si materials/substrates on Silicon

- Advanced lithography and high-density VLSI patterning technologies

- Beyond-CMOS functional devices

- Packaging technologies, Through-Silicon-Vias and 3D-system integration

- Advanced device analysis, theoretical understanding and modeling; operational fundamentals and reliability of the above devices

VLSI manufacturing concepts, technologies, and yield optimization

Additional highlights include:

- Plenary sessions: "Storage Architecture for the Data Center in 2020", "Technology Development for Printed LSIs Based on Organic Semiconductors" (Circuits), and "Customer Value Creation in the Information Explosion Era" (Technology)

- Rump sessions: "Who Gives Up On Scaling First?" (Circuits), and "450mm, EUV, III-V, 3D - All in 7 nm? Are You Serious?!" (Technology)

- Full-day short courses on "Advanced Data Converter & Mixed-Signal Design", "Advanced Energy-Efficient Digital Design" (Circuits), and "High Performance Mobile SoCs enabled by 10 nm SoCTechnology" (Technology)

Two satellite workshops will be held before the conference: "Silicon Nanoelectronics" (June 8th-9th) and "Spintronics" (June 9th).

We cordially invite you to attend the 2014 Symposium on VLSI Technology. For further information please visit the VLSI Symposia website: http://www.vlsisymposium.org.

> Symposium Chairman Klaus Schruefer (Germany) Intel Mobile Communications

> > Symposium Co-Chairman Toshiro Hiramoto (Japan) University of Tokyo

> > > Program Chairman Raj Jammy (USA) Intermolecular

Program Co-Chairman Satoshi Inaba (Korea) Toshiba Electronics Korea Corporation

## TECHNICAL BRIEFS

# SEMICONDUCTORS AND POWER ELECTRONICS IN THE 21ST CENTURY

Krishna Shenai

The information economy of the 20th century was largely built around the silicon chip technology that revolutionized the computing and communication

age. The same can be said about the emerging energy economy of the 21st century where silicon in particular and semiconductors in general, are expected to play a pivotal role in the generation, transmission, distribution, and consumption of electricity. Today, silicon is the "work-horse" for the \$250 billion power electronics industry world-wide, and enjoys more than \$25 billion annual market with a 30% CAGR. Since power electronics is the key enabler of the 21st century global energy economy, semiconductors are expected to play a pivotal role in shaping the emerging world.

Today, silicon power switching technology is predominantly used for conditioning of the electrical energy at the consumer end. This is largely due to the fact that singlechip silicon power devices are rated below 6.5 kilo volts and 150 amps because of material and packaging limitations. This scenario is expected to change soon as high-voltage power switching devices made from wide bandgap (WBG) semiconductors are slowly entering the commercial market. The WBG semiconductors, including silicon carbide (SiC) and gallium nitride (GaN), offer unprecedented increase in energy efficiency compared to silicon because of their superior electrical and thermal properties. Furthermore, smaller ca-

pacitances and higher temperature operation capability of WBG power switching devices lead to dramatic miniaturization of power electronic systems-a key economic driver. Single-chip WBG power switching devices capable of blocking more than 25 kilo volts will be commercially available in the near future. The high-voltage power switching characteristics of WBG semiconductors has the potential for transformative impact on the electricity transmission and distribution (T&D) infrastructure. For example, compact and efficient solid-state transformers may soon replace the humongous magnetic power transformers in today's electricity infrastructure, and the realization of flexible AC transmission and distribution (FACTS) concept may render the conventional AC electricity grid more robust and resilient to load variations.

Perhaps the greatest challenge of the 21st century energy economy pertains to low-cost and efficient electricity generation and utilization from clean distributed renewable energy generators (DREGs). Much of the United States has a mandate to generate least 25% electricity from green resources by 2025. Solar, wind and clean gas are touted to be the prime sources of clean energy. At the dawn of the 20th century, it is becoming apparent that solar cells made from silicon and compound semiconductors could produce much of the electricity generated from the sun. Many experts believe that solar photovoltaics (PV) may become the dominant source for renewable clean electricity generation in the near term. At the same time, semiconductors are also gaining popularity for harnessing electricity for ultra-low power electronics applications including portable wireless devices. The main challenge then comes down to efficient integration and utilization of electricity produced from renewable means. One approach is to feed back the electricity produced from the DREGs to the main utility AC grid; this would require solidstate power inverters. A more attractive and cost-effective alternative is to directly utilize the DC electricity produced from the DREGs since a majority of house-hold electrical loads are DC-powered. This is particularly interesting for the lighting application since it is slated to migrate from incandescent bulbs to solid-state technology within the next decade. One can envision a complete electrical system-from the source to the load-all built from semiconductors, as it would be the case for solar-powered light emitting diodes (LEDs). Solar-powered data centers are already being built. The opportunities are numerous for integrating renewable energy means in order to improve the standard of living of billions of people around the world, and especially those living in the developing and under-developed parts of the globe.

The potential impact of power electronics is even more dramatic on the environment. The ability to freely access fresh water and clean air may dictate the human endeavors in the 21st century. The growing concerns of global warming and ever increased consciousness for increased air and water pollution are demanding rapid electrification of the transportation industry. Power electronics

is the key enabler of hybrid and allelectric vehicles, from automobiles to ships and airplanes. Soon we may see gasoline charging stations replaced with battery charging stations, and the high-ways embedded with wireless battery chargers. The continuous infusion of power, computing, communication and sensing electronics is accelerating the development and deployment of intelligent systems in all walks of human life including transportation, housing and manufacturing.

The demands of the 21st century energy- and environment-conscious society open new opportunities

and challenges for power semiconductors and power electronics. The focus of electronics system design is already shifting from an allperformance-driven approach to a more energy-driven methodology. The semiconductor manufacturing is likewise drifting from traditional signal- and communication-driven to more power-switching and powermanagement centric. This is an exciting time for our society as we are destined to be the key benefactors of the emerging energy economy.

Krishna Shenai (F'01) earned his Ph.D. degree in electrical engineering from Stanford University in 1986. He is employed as a Principal Electrical Engineer within the Energy Systems Division at Argonne National Laboratory in Chicago, Illinois. He is a Senior Fellow at the Northwestern-Argonne Institute of Science and Engineering (NAISE) at Northwestern University, Evanston, Illinois and a Senior Fellow at the Computation Institute at the University of Chicago, Chicago, Illinois, Dr. Shenai is an Editor of IEEE Journal of the Electron Devices Society and is a member of EDS Technical Committees on Power Devices and Semiconductor Manufacturing.

## UCSB RESEARCHERS TAKE CARBON NANOTUBE INTERCONNECTS CLOSER TO REALITY

The semiconductor industry has been confronting an acute problem in the interconnect area. As IC feature sizes are scaled below 14 nm, copper wires exhibit significant "size effects" resulting in a sharp rise in their resistivity. This has adverse impact on IC performance and reliability in the form of higher communication costs due to increased interconnect delays and chip-level power dissipation, as well as due to reduced current carrying capacity of the copper wires. Carbon nanotubes (CNTs) have very high current carrying capability (at least two orders of magnitude higher than that of copper), long mean free path (on the order of µm), and high thermal conductivities (several times higher than that of copper), indicating that CNTs could be potentially employed as alternative materials for next-generation nanoscale interconnects. Such interconnects can

enhance the electrical performance as well as eliminate reliability concerns that plague nanoscale copper interconnects.

However, fabrication and characterization of long and horizontal CNT-bundles necessary for interconnect applications have remained an enigma. In a game-changing development, researchers at UCSB led by Prof. Kaustav Banerjee in collaboration with Dr. Alan Cassell at NASA Ames and Prof. Franz Kreupl

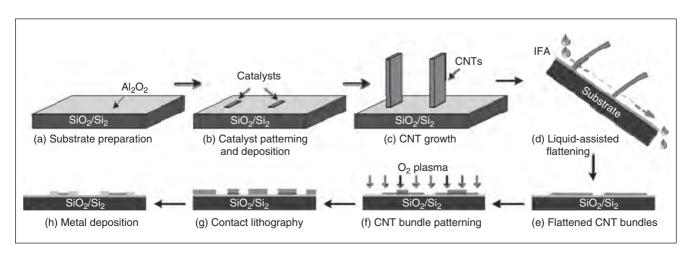

(a-h) Fabrication process flow of horizontal CNT-bundle interconnects.

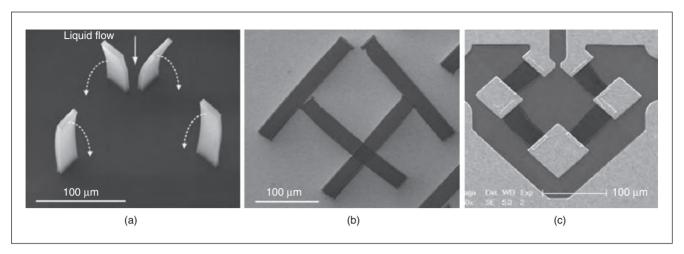

(a) Placement of vertical CNT-bundles for constructing Manhattan structures with liquid flow along the directions indicated by the solid yellow arrow. Broken yellow arrows indicate the orientation of flattening. (b) 2-D Manhattan structure obtained after flattening of the four vertical CNT-bundles in

(a). (c) Spiral inductor formed with metal contacts based on the Manhattan structure in (b).

at TU-Munich have demonstrated a novel process that, for the first time, enables fabrication of high-density, long (over 100 microns) and thick (up to microns) horizontally aligned CNT interconnects. This demonstration has thus overcome one of the biggest challenges facing the CNT interconnect technology and is a vital step for implementation of CNT based interconnects and passive devices in next-generation VLSI. The developed process not only yields horizontal CNT interconnects with the lowest reported resistivity, but also enables the first ever fabrication

of a CNT based on-chip spiral inductor. These results have been recently published in Electron Devices Society's flagship journal IEEE Transactions on Electron Devices by Hong Li et al., [1],[2].

#### **Link to Articles**

[1] H. Li, W. Liu, A. M. Cassell, F. Kreupl and K. Banerjee, "Low-Resistivity Long-Length Horizontal Carbon Nanotube Bundles for Interconnect Applications—Part I: Process Development," *IEEE Transactions* on Electron Devices, Vol. 60, No. 9, pp. 2862–2869, 2013. [2] H. Li, W. Liu, A. M. Cassell, F. Kreupl and K. Banerjee, "Low-Resistivity Long-Length Horizontal Carbon Nanotube Bundles for Interconnect Applications — Part II: Characterization," *IEEE Transactions on Electron Devices*, Vol. 60, No. 9, pp. 2870–2876, 2013.

> Samar Saha Ultrasolar Technology Santa Clara, CA, USA

M K Radhakrishnan NanoRel Bangalore, India

# 2013 IEEE INTERNATIONAL ELECTRON DEVICES MEETING—SUMMARY

Some 1,400 of the world's leading scientists and engineers in semi-conductor and related technologies attended EDS's premier annual technical conference last December in Washington, D.C., the 59th edition of the IEEE International Electron Devices Meeting.

Among the most noteworthy technologies discussed in more than 220 presentations given over five days of tutorial, short course and technical sessions were the following:

- FinFETs and fully depleted silicon-on-insulator (FD-SOI) devices, and which type of device represents the optimum approach for continued scaling

- non-silicon devices such as tunneling FETs (TFETs), which hold promise as a way to control transistor off-state leakage by getting

- around the sub-60 mV/decade steep substhreshold slope barrier

- various non-volatile memory technologies such as resistive memories (ReRAM or RRAM), which are attracting interest because of their potential to deliver faster write times and greater endurance than flash

- biomedical electronics, which are attracting widespread interest

because of the potential for lowcost DNA-sequencing on a chip In keeping with the spread of electronics to an increasing variety of applications, the 2013 IEDM offered attendees special focus sessions in the areas of BioMEMS, analog device and circuits, and advanced manufac-

turing technology.

In addition, the IEDM conference again offered 90-minute Saturday tutorial sessions on emerging topics. These are separate from the daylong short courses which delve more deeply into topics. Interest in the tutorials has grown very strongly, and 416 registrants attended tutorials in 2013 on atomic-scale modeling and simulation for nanoelectronics; interface properties for SiC and GaN MOS devices; low-dimensional systems for device applications in nanoelectronics; TFETs; 3D chip-stacking; and energy-harvesting for self-powered electronic systems.

Technical highlights from IEDM 2013 include:

#### FinFETs and FD-SOI

To scale down below the 20 nm node, leading-edge semiconductor manufacturers are looking at FinFETs and FD-SOI devices.

Taiwan Semiconductor Manufacturing Co. (TSMC) gave details about its upcoming 16 nm FinFET technology, which includes a 0.07 um<sup>2</sup> SRAM, copper/low-k interconnects, highk/metal-gate and other features for mobile system-on-a-chip (SoC) applications. The transistors achieved a short channel control with DIBL of  $<30 \,\mathrm{mV/V}$  and a  $\mathrm{Id}_{\mathrm{sat}}$  of 520/525 uA/um at 0.75V and  $I_{\rm off}$  of 30 pA/um for NMOS and PMOS.

Meanwhile, FD-SOI papers discussed results that included high performance, low leakage, ultra-low power, and excellent variability, reliability and scalability down to the 10 nm node (by means of thin SOI and thin BOX substrates). Performance boosters using high mobility materials such as thin strain Si, Ge, and III-V on-Insulator were also presented.

#### **TFETs**

TFETs use the quantum mechanical tunneling of electrons through an ultrathin energy barrier to provide high current at low voltage. They potentially could be used in applications where both high speed and low power are needed, such as smart sensor networks, implantable medical electronics and ultra-mobile computing. Interest in them is growing strongly-the devices were the subject of an IEDM Saturday tutorial session, a Sunday Short Course module, were part of an Evening Panel Session on emerging materials and device concepts, and were the subject of numerous papers.

One noteworthy paper was from Penn State University. It described a TFET geared for medical devices that could be implanted inside the human body. For implanted devices, generating too much power and heat can damage tissue, and draining the battery frequently would require frequent replacement surgery.

#### **ReRAM**

Many ReRAM papers were presented at the IEDM. A noteworthy paper from IMEC described a conductive bridging RAM (CBRAM) technology. It relies on the fact some amorphous materials with relatively large amounts of metal can behave as solid electrolytes. Under a voltage bias, metal ions can form a conductive filament, and the process can be reversed as needed, enabling the reading and writing of data. IMEC researchers described a 3D imaging approach that enabled them to "see" filament formation, a necessary step to optimizing it.

#### **Bio-medical Electronics**

Noteworthy biomedical electronics papers described novel ways to accomplish low-cost DNA-sequencing on a chip. Hitachi researchers described a way to identify the nucleotides making up the DNA molecule by means of a side-gated ultrathin FET containing a nanopore through which DNA strands pass. Channel current is modulated by the electrical charges each DNA nucleotide produces as it passes through the nanopore. A Kookmin University paper described a hybrid biosensor which, for the first time, integrates silicon nanowires and CMOS devices for DNA detection. It demonstrated extremely impressive and consistent sensitivity, expressed as a change in output voltage of 1.2 V per 0.4 change in pH level, and as a 1.2 V change per 200 fM of DNA. A paper by IBM described a CMOScompatible, 200-mm wafer-scale sub-20-nm nanochannel fabrication method that enables stretching, translocation and real-time fluorescence microscopy imaging of single DNA molecules.

#### **Plenary Talks**

As the conference began, three plenary speakers delivered thoughtprovoking views of future trends. Andrea C. Ferrari from the University of Cambridge spoke on, Graphene: Future Emerging Technology. He presented an unbiased story depicting the challenges and opportunities in graphene to be the disruptive device technology of the 21st century.

Meanwhile, a talk by Mitsumasa Koyanagi from Tohoku University on the topic, Heterogeneous 3D Integration: Technology Enabler Towards Future Super-Chips, delved into the details of realizing the Super Chip of the future, which will include heterogenous integration of compound semiconductor devices, photonic devices and spintronic devices using 3D integration.

Finally, Geoffrey Yeap of Qualcomm delivered an address titled, Smart Mobile SoC Driving the Semiconductor Industry: Technology Trend, Challenges and Opportunities. He highlighted the explosive growth in demand for smart mobile devices in the last decade, and described a judicious strategy of selecting technology nodes, transistor architectures, embedded memory type and

backend design rules to address the power, performance and cost requirement of future mobile SoCs.

#### **Luncheon Speaker**

The IEDM luncheon address was given by Eric Enderton of Nvidia Corp., on the topic Graphics and GPU Computing: Past, Present and Future. He described the development and growth of graphic processing unitbased (GPU-based) computing, with regard to both supercomputing and the evolution of fixed-function graphics pipelines. He gave an overview of architectural differences between GPUs and CPUs, discussed the evolution of graphics into a general-purpose computational problem, and argued that GPU-based computing because of its inherent parallelism is a better way to address many of today's computing needs than are more traditional single- or few-threaded CPUs.

#### **Entrepreneur's Lunch**

Based on the success of the initial Entrepreneur's Lunch at IEDM 2012 in San Francisco, the IEDM conference and EDS Women in Engineering again co-sponsored the event in 2013. The

event was moderated by Thuy Dao from Freescale Semiconductor, Chair of EDS Women in Engineering.

The speaker was Steve Nasiri, angel investor and mentor at Nasiri Ventures LLC. For 35 years Nasiri has been a serial Silicon Valley entrepreneur, most recently with InvenSense, which he founded in 2003 and where he served as President, CEO and Chairman until October, 2012, having taken the company public the prior year. Under Nasiri, the company pioneered and became the global market leader in motion-processing solutions for motion-based consumer electronics user interfaces.

Nasiri gave a brief talk on how he came to be an entrepreneur and described some of the main challenges. The remainder of the event was a Q&A session in which he answered numerous questions, ranging from how to approach a venture capitalist to the optimum make-up of a start-up's executive team.

## Short Courses and Evening Panels

All-day Sunday short courses and Tuesday evening panel sessions are among the most, well-attended events during any IEDM conference.

IEDM 2013 featured two short courses which ran in parallel: Challenges of 10 nm and 7 nm CMOS Technologies, organized by Aaron Thean from IMEC, and Beyond CMOS: Emerging Materials and Devices, organized by Thomas N. Theis of Semiconductor Research Corporation.

The evening panel sessions, designed to foster discussion and debate on important technical and industry issues, were Will Voltage Scaling in CMOS Technology Continue Beyond the 14 nm Generation?, moderated by Kevin Zhang of Intel Corporation, and IsThere Life Beyond Conventional CMOS? moderated by Jeff Welser of IBM.

Ken Rim 2013 IEDM Publicity Chair Qualcomm Inc. San Diego, CA, USA

Suman Datta 2013 IEDM Publicity Vice-Chair Penn State University University Park, PA, USA

## 2014 IEEE IRPS—TECHNICAL PROGRAM HIGHLIGHTS

JUNE 1-5, 2014 • HILTON WAIKOLOA VILLAGE • WAIKOLOA, HI, USA

The International Reliability Physics Symposium (IRPS) is the world's premier forum for leading-edge research addressing developments in the Reliability Physics of devices, materials, circuits, and products. IRPS is the conference where emerging Reliability Physics challenges and possible solutions to achieve realistic End-of-Life projections are first discussed. This year, the IRPS will be held at Hilton Waikoloa Village, Waikoloa, Hawaii, U.S.A. Scheduled for June 1-5, 2014, the IRPS will

commence with two full days of tutorials on June 1 and 2.

## HIGHLIGHTS OF THE TECHNICAL PROGRAM

The IRPS 2014Technical Program will consist of 118 platform presentations and 97 poster presentations. This year's symposium will provide a comprehensive look into the current research activities and thinking in semiconductor reliability and physics of failure. Some highlights of the technical program include:

BTI and HCI – Several presentations will address advances in bias-temperature-instability (BTI) and hot-carrier injection damage (HCI). Models for BTI have grown increasingly sophisticated and are now developed to account for the AC duty cycle dependence, although number of aspects remain the topic of lively controversy. The statistics of BTI in very small area transistors is drawing increased attention. Hot carrier damage has also seen increased

- interest. Both BTI and HCI are now the topics of new research on FETs fabricated with alternative materials such as III-Vs and Ge, which are being explored as potential Silicon replacements.

- **BEOL Reliability** Back end of line (BEOL) reliability includes the metallization and low-k dielectrics. As dimensional scaling continues to outpace voltage reduction, this increases the demands on the BEOL to carry higher current densities and support higher electric fields. Several papers highlight both process and design sensitivities for electromigration, stress migration, and low-k dielectric breakdown mechanisms. More accurate and sophisticated reliability models for these mechanisms to allow products to push the technology to the fullest advantage in performance while reducing chip area are presented in these sessions.

- Soft Error Emerging soft error effects, including muon-induced SRAM soft errors, thermal neutron-induced SRAM soft errors in a high-k/metal gate technology, neutron-induced soft errors in multi-level NOR FLASH and heavy ion-induced soft errors in Phase Change Memory are being presented. Several papers on mitigation methods including

- new flip-flop designs, a well doping approach, a novel transistor design, and application of bodybias will be presented. Characterization and simulation of soft errors in SRAM, flip-flops and logic gates is also addressed.

- Compound Devices This session attracted record submission for 2014, with the reliability of GaN power devices emerging as the key topic. The strong interest in this particular area is driven by the fact that almost all of the large silicon companies today have active programs in GaN power electronics. Several GaN topics will be extensively covered, including physical origin of traps, buffer or barrier, trapping effects on device reliability, such as those causing voltage instabilities and current collapse in D and E-Mode GaN devices, stress methodologies on these devices like hot-cold switching or shortlong switching.

TUTORIALS: IRPS 2014 will have four tutorial tracks:

- FEOL/transistor reliability

- MOL/BEOL reliability, including 3D, chip package interaction, ESD and latch-up

- Circuit and component reliability simulation, modeling and statistical techniques

Systems reliability, including consumer, automotive, avionics and network applications

YEAR IN REVIEW: An afternoon presentation by industry experts on recent advances in key areas of device reliability physics where three areas will be highlighted; reliability of various memory technologies, circuit aging and FinFET reliability.

WORKSHOPS and PANEL DISCUS-SION: There will be six workshops covering transistor reliability, NVM (NAND and ReRAM), soft errors, BEOL, circuit reliability and GaN power device reliability. The topic of the panel discussion is "Design for Variability, New Materials, 3D Structures: What role will these techniques play in addressing the reliability of future scaling?"

For more information, visit www. irps.org

Chris Henderson 2014 IRPS Technical Program Chair Semitracks

> Chris Connor 2014 IRSP Technical Program Vice-Chair Intel

> > Prasad Chaparala 2014 IRPS General Chair Alta Devices

#### IEEE ResumeLab is Now Available!

ResumeLab allows IEEE members to use customized templates to create resumes/CVs, letters related to the employment process, portfolios of past work, skills profiles, and video resumes. The product also provides members with the ability to conduct mock interviews. Finally, everything created in the product can be shared with colleagues, mentors, potential employers, the

public, or social media via publicly-available links.

For more information about the product visit <a href="www.ieee.org/resumelab">www.ieee.org/resumelab</a>.

## SOCIETY NEWS

### MESSAGE FROM EDITOR-IN CHIEF

M.K. Radhakrishnan

Dear Readers.

In line with our Society's mission statement—to foster professional growth of its members and to enhance visibility in the field—we

are initiating new sections and columns in our Newsletter. With this April issue of the Newsletter we are introducing one new Section "Technical Briefs". With the help of the Editorial teams of TED and EDL as well as our own Editorial team, it is envisaged to grow as a strong section in the Newsletter to disseminate condensed versions of latest research trends in the device area and a platform to discuss future trends. In the current issue we have three feature articles—IEDM briefs, recent trends in carbon nanotube interconnects, and semiconductors and power electronics in 21st century.

We have introduced a new Column from this issue "for Young Professionals". This column aims at our new and young members to provide some guidelines and useful stories and to hear their views. A very interesting article on working successfully in semiconductor industry by Doug Verret based on his earlier Webinar is included. Further, we are now starting to publish brief answers to the Quest EDS, which will be of immense use to the readers.

Again, the aim is to make the Newsletter a more useful magazine

for our Society members. I request all Chapters to provide reports of their social and humanitarian activities also. We may see such news in future issues, and through which Chapters start to know each other better.

However, the success of all these reposes on the feedback and input from our readers. As such, on behalf of the Editorial team and staff, I request your feedback and suggestions. You may note that an exclusive e-mail id is also provided for feedback and suggestions.

Please use: edsnewsletter@ieee.

M.K. Radhakrishnan Editor-in Chief, EDS Newsletter NanoRel, Bangalore, India e-mail: radhakrishnan@ieee.org

## DECEMBER 2013 EDS BOARD OF GOVERNORS (BoG) MEETINGS

EDS Secretary

The 2013 December EDS Board of Governors (BoG) meeting series was held in conjunction with the 2013 IEEE International Electron Devices Meeting (IEDM) in Washington, DC.

As reported in the January edition of the Newsletter, the 2014 society elections were held. The following members were elected to key positions:

Members at Large: Arturo Escobosa, Ru Huang, Leda Lunardi, Mikael Ostling, MK Radhakrishnan, Jacobus Swart, and Xing Zhou.

- Secretary: Fernando Guarin

- Treasurer: Ravi Todi

- President-Elect: Samar Saha

In addition, important Constitution and Bylaws changes were approved at the meeting. These changes will provide better consistency, transparency, and flexibility into EDS's structure and operations. A separate article will follow this report, detailing the recently approved changes. The updated EDS Constitution and Bylaws will also be posted in the News and Announcements section of the EDS website.

Several other important motions were passed, as summarized below:

Approved the proposed list of 2014 committee appointments.

- Approved Singapore as the 2015 mid-year meeting location.

- Approved the proposed list of 2014 Vice Presidents.

- Approved the list of 2015 repeat conferences.

EDS is blessed with a diverse and engaged volunteer corps representing all the world's regions. The December BoG meeting was especially lively, with over 20 volunteers presenting and more than 70 attendees in total. We offer our sincere thanks to you all. It was an outstanding gathering which served to finalize the society's work for 2013 and provided a framework and inspiration for our 2014 initiatives.

#### **Motions**

#### **President's Report**

1. To approve the proposed list of 2014 committee appointments. Motion passed unanimously.

#### **ExCom Update**

- 2. To approve Singapore as the 2015 mid-year meeting location. Motion passed unanimously.

- 3. To approve the proposed list of 2014 Vice Presidents. Motion passed unanimously.

#### Secretary's Report

4. To approve the June 2013 BoG meeting minutes. Motion passed unanimously.

#### **Meetings and Conferences** Report

- 5. To approve the list of 2015 repeat conferences. Motion passed unanimously.

- 6. To approve the Constitution and Bylaws amendments from the working group headed by S. Deleonibus. Motion passed,

- though additional changes may be brought forward at the June meeting with respect to the clauses on amending the Constitution and Bylaws. The EDS Secretary will oversee this effort.

- 7. To adjourn the meeting. Motion passed unanimously.

Fernando Guarin EDS Secretary IBM Microelectronics Hopewell Junction, NY, USA

## ANNOUNCEMENT OF NEWLY ELECTED OFFICERS AND **BOG M**EMBERS

The EDS officers and Board of Governors members-at-large elections were held on December 8, 2013 in Washington, DC. All voting members were present at this important event. I am pleased to present the results of this election and short bios of the upcoming team that will lead EDS in years to come.

#### **OFFICERS**

The following volunteers were elected as Officers beginning 1/1/2014:

#### **President-Elect**

Samar Saha received the Ph.D. in Physics from Gauhati University and MS in **Engineering Man**agement from Stanford Univer-

sity. Currently, he is a Technical Advisor at Ultrasolar Technology, Santa Clara and an Adjunct Professor in the Electrical Engineering (EE) Department at Santa Clara University. He has worked in various positions for National Semiconductor, LSI Logic, Texas Instruments, Philips Semiconductors, Silicon Storage Technology, Synopsys, DSM Solutions, Silterra, and SuVolta. He has also worked as a faculty member in the EE departments at Southern Illinois University, Carbondale; Auburn University; University of Nevada; Las Vegas; and the University of Colorado; Colorado Springs.

Samar is an elected member of the EDS BoG: Editor-In-Chief, Quest-EDS; and a member, IEEE TAB Periodicals Committee. His past IEEE services include Vice President, EDS Publications; Regions 5 & 6 Editor, EDS Newsletter; member, IEEE Conference Publications Committee; Chair, EDS Compact Modeling Committee; Chair, EDS SRC-NAW; guest editor, three Special Issues of IEEE T-ED; and Chair of the ED Santa Clara Valley Chapter.

#### Secretary

Fernando Guarin is a Senior Engineer/Scientist at the IBM Microelectronics Semiconductor Research Development Center SRDC in East

Fishkill, New York and an Adjunct Lecturer at SUNY New Paltz. He received his BSEE from the "Pontificia Universidad Javeriana", in Bogotá, Colombia, the M.S.E.E. degree from the

University of Arizona, and the Ph.D. in Electrical Engineering from Columbia University, New York. He has been actively working in microelectronic reliability for over 30 years.

From 1980 until 1988 he was a member of the Military and Aerospace Operations division of National Semiconductor Corporation. In 1988 he joined the IBM microelectronics division where he has worked in the reliability physics and modeling of Advanced Bipolar, CMOS and Silicon Germanium BiCMOS technologies. He is currently leading IBM's 14 nm technology qualification. Dr. Guarín is an IEEE Fellow, Distinguished Lecturer for the IEEE Electron Devices Society, a member of the IEEE's EDS Board of Governors and Education Committees.

#### **Treasurer**

Ravi Todi received his M.S. degree in Electrical and Mechanical Engineering from University of Central Florida in 2004 and 2005 respectively,

and his doctoral degree in Electrical Engineering in 2007. His graduate

research work was focused on gate stack engineering, with emphasis on binary metal alloys as gate electrode and on high mobility Ge channel devices. In 2007 he started working as Advisory Engineer/Scientist at Semiconductor Research and Development Center at IBM Microelectronics Division focusing on high performance eDRAM integration on 45 nm SOI logic platform. Starting in 2010 Ravi was appointed the lead Engineer for 22 nm SOI eDRAM development. For his many contributions to the success of eDRAM program at IBM, Ravi was awarded IBM's Outstanding Technical Achievement Award in 2011. Ravi joined Qualcomm as Staff Engineer responsible for 20 nm and 16/14 nm product developments. Ravi had authored or co-authored over 50 publications, has 5 issues US patents and over 20 pending disclosures.

#### **BOG MEMBERS-AT-LARGE**

A total of seven members were elected for a three-year term (2014-2016). Four of the seven electees are serving a second term, while the other three have joined the board for the first time. The backgrounds of the electees span a wide range of professional and technical interests. The following are the results of the election and brief biographies of the individuals elected.

#### **Second Term Electees**

Arturo Escobosa received a degree in Communications and Electronics Engineering from the National Polytechnic Institute,

Mexico, and a Masters diploma in Electrical Engineering from Cinvestav, Mexico. He was granted a Ph.D. degree from the AachenTechnical University, Germany in 1983, due to his work at the Institute of Semiconductor Electronics, in the field of ohmic contacts on GaAs MOCVD

epitaxial layers. Since 1983, he has been working as full professor at the Solid State Electronics Group of the Electrical Engineering Department of Cinvestav, México. His research interests include MOCVD Epitaxial Growth of III–V Compounds, Optical Characterization of Semiconductors and X-Ray diffraction for Crystal Characterization. He is Region 9 EDS SRC Vice-Chair since 2012.

Mikael Östling received his MSc and the Ph.D. degrees from Uppsala University, Sweden. He holds a position as professor in

solid state electronics at KTH, Royal Institute of Technology in Stockholm, Sweden. He is currently department head of Integrated Devices and Circuits and was the dean of the School of Information and Communication Technology, KTH, between 2004 and 2012. Östling was a senior visiting Fulbright Scholar at Stanford University, and a visiting professor with the University of Florida, Gainesville. In 2005 he co-founded the company TranSiC, acquired in full by Fairchild Semiconductor 2011. He was awarded the first ERC grant for advanced investigators. His research interests are nanoscaled Si and Ge device technologies and emerging 2D materials, as well as device technology for wide bandgap semiconductors for high power / high temperature applications. He has supervised 32 PhD theses work and co-authored about 500 scientific papers published in international journals and conferences. Mikael Östling is an editor of the IEEE Electron Device Letters and a Fellow of the IEEE.

MK Radhakrishnan received M.Sc in Solid State electronics from Sardar Patel University in 1975 and Ph.D from Cochin University in 1981. Currently he is Director of NanoRel

Technical Consultants Singapore.

During the past 30 years he worked with ST Microelectronics, Philips, ISRO, Institute of Microelec-

tronics and National University of Singapore. He was Technical Chair IEEE IPFA 1995-97, IPFA General Chair 1999, IEEE IEDST General Chair 2009 and Chairman IEEE Rel/CPMT/ED Singapore Chapter 2000-01. He is an EDS Distinguished Lecturer, Editor-in Chief of EDS Newsletter, SRC Vice-Chair from Region10 and Member of EDS Technical Committee on Electronic Materials. Radhakrishnan provides technical training in device analysis area to practicing engineers for more than two decades and doing research in the area of physical failures in devices including gate dielectrics. He is a Senior Member IEEE, Fellow IETE, Member ESD Association and Member EDFAS.

Xing Zhou received the B.E. from Tsinghua University, in 1983; M.S. and Ph.D. degrees in electrical engineering from the

University of Rochester, in 1987 and 1990, respectively. He is currently a tenured faculty in the School of Electrical and Electronic Engineering, Nanyang Technological University, Singapore. His past research interests include Monte Carlo simulation of photocarrier transport and ultrafast phenomena as well as mixed-mode circuit simulation and CAD tool development. His recent research mainly focuses on nanoscale CMOS compact modeling. He has more than 120 referred journal/conference publications, and given more than 100 distinguished lectures and invited talks at various industrial and academic institutions.

He is the founding chair for the Workshop on Compact Modeling in association with the Nanotech Conference since 2002. Dr. Zhou is an elected Member-at-Large of the EDS Board of Governors and Vice President of Regions/Chapters. He has been an EDS Distinguished Lecturer since 2000 and Editor for the Electron Device Letters since 2007.

#### **FIRST-TIME ELECTEES**

Ru Huang is currently the Professor, Director of Institute of Microelectronics and Deputy Dean of School of EECS, Peking University,

China. Her research interests include nano-scaled CMOS devices, nonvolatile memory devices and device reliability/variability analysis. Since 2000, she has been a leader of several State Key Research Projects in China. She has authored or coauthored four books and more than 250 papers, including more than 50 IEDM/VLSI and EDL/T-ED papers. She is the holder of more than 100 granted patents. She was the winner of Chang-Jiang Scholar Distinguished Professor, National Science Fund for Distinguished Young Scholars and many other awards in China, including National Award for Technological Invention. She is an Associate Editor-in-Chief of "Science in China" and an editor of IEEE T-ED. She was the General Co-Chair of 2012 ICSICT, 2013 ISLPED, TPC Co-chair of 2004 and 2008 ICSICT and committee members of many other international conferences and symposiums.

Leda Lunardi has been a professor since 2003 in Electrical and Computer Engineering Department at North Carolina State

University in Raleigh, North Caro-

lina. She received the Ph.D. degree in electrical engineering from Cornell University, Ithaca, New York. After graduation she worked for AT&T Bell Labs starting in Murray Hill, New Jersev and then AT&T Labs Research after the trivesture. She was with JDS Uniphase as a group leader and senior scientist before joining academia.

From 2005 to 2007 she served as program director for the electrical. communications and cyber systems (ECCS) division in the engineering directorate of the National Science Foundation (NSF) in Arlington, Virgina. Under her direction, she started the hybrid communication systems program sponsoring research in free space optics, terahertz components, RF and microwave devices and subsystems.

Her research is on traditional electronic and photonics devices and their applications on energy scavenging, or high speed integration. She has been devoted to increase the number of women and underrepresented minorities engineering and science careers. Presently she is the principal investigator of the NSF sponsored undergraduate REU-Site: Engineering the Grid, related to energy research.

For over two decades she has been a technical volunteer serving as member or chair on several IEEE executive and technical committee conferences, as well as national and international governments' ad-hoc committees for grants and projects reviews. Some of her present professional activities include member of the editorial board for IEEE Proceedings, editor for the IEEE Transactions of Electron Devices (Optoelectronics Devices), and treasurer for the IEEE Photonics Society Eastern Carolina Chapter.

At NC State, she was director of graduate programs of the ECE Department in 2007, one of the largest programs in the Southeast. From 2008-2011, she was in the leadership

team of the NSF-ERC Future Renewable Electric Energy Delivery and Management (FREEDM) Systems Center, as the education program director. She has served and chaired on several department, college and university committees. As Faculty Senate member, she is committed to represent her fellow faculty members.

Jacobus **Swart** received B. Engineer and Dr. Engineer Degrees in 1975 and 1981 respectively, from the Polytechnic School of the

University of São Paulo, Brazil. Afterwards he worked at the following institutions: K. U. Leuven, Belgium, 1982-83, as a pos-doc.; CTI, Campinas, 1984, as head of Process Engineering; LSI-University of São Paulo, 1985-88, as Assistant Professor; SID Microeletrônica, 1986; RTI, USA, 1991, as a Visiting Scientist; and UNICAMP, since 1988, as Full Professor. He served as director of the Center for Semiconductor Components, 1998-2005 and as Director of CTI, 2007-2011. He is currently IMEC representative in Brazil. He is ranked as fellow researcher, level 1A (highest), at CNPq and is a Fellow of IEEE and of the São Paulo State Academy of Science. He is currently the leader of a large research network in Brazil, called NAMITEC.

I welcome all electees and urge them to truly get engaged in the affairs of the Electron Devices Society. EDS is considered to be a volunteerled, volunteer-driven organization and we expect nothing less from all to continue this tradition.

Renuka Jindal EDS Nominations and Elections Chair University of Louisiana at Lafayette Lafayette, LA, USA

## SUMMARY OF CHANGES TO THE EDS CONSTITUTION AND BYLAWS

As reported in the January issue of the Newsletter, on December 8, 2013, the EDS Board of Governors (BoG) approved changes to the EDS Constitution and Bylaws. These amendments were then approved in February, 2014 by the Chair of the IEEE Technical Activities Board (TAB). The changes will take effect 30 days following their publication in this copy of the Newsletter (distributed to all EDS members), unless objections are received from at least 5% of the EDS membership. The following is a high-level summary of the changes:

#### Constitution

Article V. Sections 1-7: The changes here create the EDS Forum, separate from the BoG. Basically, the Forum handles all issues relating to society business except Constitution and Bylaws changes and election of officers and members-at-large. In short, the BoG handles items formerly reserved for what was called "Fullvoting members" and the Forum handles everything else: approving the budget, member dues, pages counts for publications, ratifying committee appointments, approving motions, conference and meeting approvals... etc.

**Article V. Section 9:** Make committee appointments 2 years, not three years.

Article V. Section 10: These are the ExCom changes per then President-elect Albert Wang's Ad Hoc and approved by BoG via email vote in 2013. The changes consolidate the VP positions of Awards, Technical Activities, and Education into other VP roles.

**Article VII. Section 4:** Fixed the quorum number for both the BoG and the Forum to be a majority of the voting members of each respective body.

#### **Bylaws**

Section 3.4 (was 3.8): Added that BoG must vote to remove a member from its ranks. Also, we have added that in order to be removed, two-thirds vote of the BoG with quorum present is required.

**Section 3.5 (was 3.9):** Added "or other society governing documents" (such as committee charters) as taking precedent over Robert's Rules.

Section 5.3, 5.5, and 5.6, 7.3: Clarified that the Nomination and Elections committee's role is to verify that candidates are qualified. They cannot remove candidates from the slate.

**Section 5.6**: A new 5.6 was added, granting permission to pilot general elections.

Section 7.1: Changed the requirement for running for an Officer

position to require a candidate has served as either a member of ExCom for one year or as an elected member-at-large for one year.

**Section 9.1:** Defined EIC terms as per the guidance of then Publications VP Samar Saha's ad-hoc committee.

Section 13: What we have done here is clearly define the standing committees that exist and to require that each draft a charter outlining their roles, responsibilities, and operating polices to be approved by the Forum. What was previously in the Bylaws about standing committees was incomplete both in terms the committees themselves and how they function. These changes list the committees and provide a means of defining how each is structured and operates, but does so outside of the Bylaws... which is generally where such things should be defined.

These are a summary of the major changes to our Governing Documents. A detailed listing of all the changes made is available by contacting me at c.jannuzzi@ieee.org.

The complete EDS Constitution and Bylaws are available on the EDS website.

Christopher Jannuzzi EDS Executive Director

## REPORT ON THE VLSI TECHNOLOGY AND CIRCUITS COMMITTEE MEETING

The VLSI Technology and Circuits Committee Meeting was held on December 7th, at the site of the 2013 IEDM in Washington, DC.

Some key discussion points were:

- 1. Invite more members from Korea, Taiwan, India and Hong Kong

- Proposal for T-ED special issue scheduled to be published in 2015: "Variation aware technology and circuits design for <14 nm"</li>

- Create three new sub-committees: Publication, Conferences/ Workshops, and Publicity. All

committee members should join at least one of the sub-committees.

Role of each subcommittee:

a. Publication: propose topics, special issues for journal, book, and review papers

- b. Conferences/Workshops: input topics, invited talks, panel sessions, and candidates of committee members

- c. Publicity: promote our activities in EDS Newsletter, website and other media

Seiichiro Kawamura Publicity Chair JST/CRDS, Tokyo, Japan

Shu Ikeda VLSITechnology and Circuits Committee Chair, Tei Technology Austin, TX, USA

The VLSI Technology and Circuits Committee Meeting Attendees

## 23 EDS MEMBERS ELECTED TO THE IEEE GRADE OF FELLOW

#### **EFFECTIVE 1 JANUARY 2014**

Leda Lunardi EDS Fellows Chair

Seiichi Aritome, SK Hynix Inc., Icheon-si, South Korea for contributions to flash memory technologies

Phaedon Avouris, IBM Research Corporation, Yorktown Heights, NY, USA

for contributions to carbon electronics and photonics

Richard Brown, University of Utah, Salt Lake City, UT, USA for contributions to microsystem design

Babu Chalamala, MEMC Electronic Materials, Inc., St. Peters, MO, USA for contributions to the development of advanced materials and device technologies for vacuum microelectronics and field emission displays

Jing Kevin Chen, Hong Kong University of Science and Technology, Kowloon, Hong Kong

for contributions to compound semiconductor heterojunction transistor technologies

Donald Disney, Avogy, Inc., Cupertino, CA, USA

for contributions to power integrated circuits and energy efficiency applications

Ichiro Fujimori, Broadcom Corporation, Irvine, CA, USA

for contributions to oversampled data converters and gigabit wireline transceivers

Bruce Gurney, HGST, a subsidiary of Western Digital, San Jose, CA, USA for contributions to spin valve Giant Magnetoresistance sensors for magnetic recording systems

Kazunari Ishimaru, Memory Division, Toshiba Corporation, Yokohama, Japan

for contributions to static random access memory and complementary metal-oxide semiconductor devices

Byoungho Lee, Seoul National University, Seoul, South Korea for contributions to diffractive optics and three-dimensional display technologies

Kwyro Lee, Korea Advanced Institute of Science and Tech., Daejeon, South Korea

for management and R&D leadership in semiconductor technology

Zachary Lemnios, IBM Corporation, Yorktown Heights, NY, USA for leadership in advanced technologies of defense security systems

Philip Mok, Hong Kong Univ. of Science & Technology, Hong Kong, China for contributions to the design of analog power-management integrated circuits

Taiichi Otsuji, Tohoku University, Sendai, Japan

for contributions to plasmonic semiconductor integrated device technology for terahertz sensing

**Daniel Radack**, Institute of Defense Analyses, Kensington, MD, USA for leadership in microwave and millimeter-wave integrated circuit technologies and packaging techniques

**Jean-Pierre Raskin,** Universit Catholique de Louvain (UCL), Louvain-la-Neuve, Belgium

for contributions to the characterization of silicon-on-insulator RF MOS-FETs and MEMS devices

William Redman-White, University of Southampton, Hampshire, UK for contributions to chip design aspects of telecommunications systems and RFIC design

Robert Reed, Vanderbilt University, Nashville, TN, USA

for contributions to understanding the effects of single-event particle radiation on integrated circuits

**Mircea Stan,** University of Virginia, Charlottesville, VA, USA

for contributions to power- and temperature-aware design of VLSI circuits and systems

**Jacobus Swart**, State University of Campinas—UNICAMP, Campinas, Brazil

for contributions to microelectronics education in Brazil

**Jan Van Houdt, IMEC**, Leuven, Belgium for contributions to flash memory devices

**Ya-Hong Xie,** University of California, Los Angeles, CA, USA for contributions to strained-silicon materials and devices

**Rui Yang,** University of Oklahoma, Norman, OK, USA

for contributions to the mid-infrared interband cascade laser and related optoelectronic devices

> Leda Lunardi EDS Fellows Chair North Carolina State University Raleigh, NC, USA

#### New Fellows Directory

New to the Fellow Web Site is the redesigned Fellows Directory. It is the most comprehensive online search and networking tool avail-

able to members. If you need to complete an IEEE Fellow Nomination, gather information for a region, section, or society, it's now easy to accomplish.

The information in the directory can be accessed by six categories:

alphabetical by last name, year elevated, gender, IEEE region, IEEE society, and deceased. Within these categories, members can search, sort, or run a filter. For example, a report can be compiled on all Fellows within a specific region elevated in a particu-

lar year. The directory allows members to view the profiles of Fellows plus the ability to network with the Fellows. If you are not an IEEE member,

you will have limited access to certain information.

Check it out today. The directory works on handheld devices and computers. To access the directory, go to www.ieee.org/fellows, then click the Fellow Directory icon.

## Applauding 50 Years of Fellows

In 2014, IEEE will mark its 50th Fellow Class. It represents decades of honoring IEEE Fellows whose extraordinary accomplishments have changed the world.

The IEEE grade of Fellow was born in 1964 out of the merge of the American Institute of Electrical Engineers (AIEE) and the Institute of Radio Engineers (IRE). The emphasis on the elevation was and still is reserved for select IEEE members who have contributed importantly to the advancement of engineering, science, and technology, bringing

the realization of significant value to society.

Only one-tenth of one percent of the total voting membership can be elevated in any one year. Over the last fifty years, IEEE has elevated roughly 10,000 members to this honor. This is a very small percentage compared to the total membership. Unquestionably, Fellows are the crown jewels of the organization. One can only imagine what the next fifty years will bring, and the new technology that will be developed, discovered, or taught, and what new

IEEE Fellows will be recognized for their achievements.

Throughout the year, various celebrations will take place to honor those who have achieved this distinction. If you know an IEEE Fellow, congratulate him/her again for receiving this honor. You can recognize them personally, or you can acknowledge them publicly at region meetings, society meetings, section meetings, and/or conferences.

Rosann Marosy Fellow Activities Manager IEEE Member and Geographic Activities

## CONGRATULATIONS TO THE 40 EDS MEMBERS RECENTLY ELECTED TO IEEE SENIOR MEMBER GRADE!

| Yasushi Akasaka  | Dean Gans      | Cheryl Liss      |                 |

|------------------|----------------|------------------|-----------------|

| Travis Anderson  | Steven Gross   | Yang Liu         |                 |

| Amr Bayoumi      | David Grunlach | Kenneth Mays     |                 |

| M S Bhat         | Hyunsang Hwang | Thomas McKay     |                 |

| Andrea Cester    | Marek Hytha    | Kirsten Moselund | Dapeng Wang     |

| Baoxing Chen     | Douglas Katzer | Anand Murthy     | Jian-Ping Wang  |

| Hsien-Chin Chiu  | Irena Knezevic | Horst Rogalla    | Yifeng Wu       |

| Chris Connor     | Franz Kreupl   | Frank Ryan       | Huaqiang Wu     |

| Felice Crupi     | Qiliang Li     | Andrie Scholten  | AlisterYoung    |

| Peter Deane      | Chung-Hsun Lin | Charles Surya    | Hsiao Wen Zan   |

| Daniel Edelstein | Ming-Chieh Lin | Pouya Valizadeh  | Shengdong Zhang |

If you have been in professional practice for 10 years, you may be eligible for Senior Membership, the highest grade of membership for which an individual can apply. New senior members receive a wood and bronze plague and a credit certificate for up to US \$25 for a new IEEE society membership. Upon request a letter will be sent to employers, recognizing this new status.

Please remember to designate the Electron **Devices Society as your nominating entity!**

For more information on senior member status, visit: http://www.ieee.org/membership\_services/membership/ senior/index.html

To apply for senior member status, fill out the on-line application: https://www.ieee.org/membership services/ membership/senior/application/index.html. You will need to Sign-in with your IEEE account.

### 2013 AWARD WINNERS

### 2013 EDS J.J. EBERS AWARD WINNER

The 2013 J.J. Ebers Award, the prestigious Electron Devices Society award for outstanding technical contributions to electron devices, was presented to Dr. Nobukazu Teranishi of the University of Hyogo and Shizuoka University, at the IEEE International Electron Devices Meeting in Washington, DC, on December 9, 2013. This award recognizes Nobukazu Teranishi "For development of the Pinned Photodiode concept widely used in Image Sensors."

Nobukazu Teranishi was born in Kobe, Japan in 1953. He received the B.S. and M.S. degrees in physics from University of Tokyo, 1976 and 1978, respectively.

Dr. Nobukazu Teranishi receiving the J.J. Ebers Award from EDS President, Paul Yu at the 2013 IEDM

He developed image sensors and cameras at NEC Corporation from 1978 to 2000 and at Panasonic Corporation from 2000 to 2013. He is

now professor of University of Hyogo and Shizuoka University, where he develops photon counting image sensor, imagers for various wavelengths; (visible, infrared, X-ray), and new functions for image sensors.

He invented pinned photodiode (PPD) for image sensors with no image lag, low noise and low dark current in 1980. The PPD CCD has been in mass production since the mid 1980's because of its superior performance. In the late 1990's, PPD was introduced into CMOS image sensors. Then, their performance became competitive to CCD's. The high performance of PPD drove the pixel size

shrinkage, and realized higher resolution. Now, almost all CCD's and CMOS image sensors utilize the PPD. The PPD is most innovative technology for both CCD's and CMOS image sensors. The market has spread into every corner of the globe. As a result, 1.3 billion image sensors were produced in 2010.

He has authored and co-authored 80 papers and holds 46 Japanese patents and 21 US patents. His leadership at academic societies and industry and his PPD invention have been honored by government organizations as well as societies around the globe. He won the Prize of the President of

KEIDANREN of National Invention Awards in 1994, Commendation by Minister of State for Science and Technology in 1997, Niwa-Takayanagi Award from the Institute of Image Information and Television Engineers in 2000 and 2013, Progress Medal and Hon. Fellowship from Royal Photographic Society in 2010, Progress Medal from Photographic Society of America in 2011. His group won the Emmy Award in 1991 by the broadcast-use CCD camera development.

He is a fellow member of the Institute of Image Information and Television Engineers of Japan, where he served as a chair of the paper editor committee and a chair of the Information Sensing Committee. He is also a Fellow of IEEE, where he served as a general chair for 1999 and 2005 IEEE Workshop on Charge-Coupled Devices & Advanced Image Sensors. He serves as President of International Image Sensors Society.

He and his wife, Makiko, have two sons and two lovely granddaughters. They like traveling and hot springs.

> Jayant Baliga EDS J.J. Ebers Award Chair North Carolina State University Raleigh, NC, USA