APRIL 2016 VOL. 23, NO. 2 ISSN: 1074 1879

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

### TABLE OF CONTENTS

| TECHNICAL BRIEFS                                                                                                                                                                                                                                 |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Too Hot to Handle: Self-Heating of Transistors</li> </ul>                                                                                                                                                                               |

| UPCOMING TECHNICAL MEETINGS 7                                                                                                                                                                                                                    |

| 2016 IEEE International Reliability Physics     Symposium (IRPS)     2016 IEEE International VLSI Symposium (VLSI)                                                                                                                               |

| 2016 IEEE Compound Semiconductor Integrated Circuit Conference (CSICS)     2016 IEEE International Semiconductor Conference (CAS)                                                                                                                |

| 2016 IEEE International Electron Devices Meeting (IEDM)                                                                                                                                                                                          |

| SOCIETY NEWS                                                                                                                                                                                                                                     |

| <ul> <li>Message from EDS President Elect</li> <li>Message from the Editor-in-Chief</li> </ul>                                                                                                                                                   |

| Technical Committee Reports                                                                                                                                                                                                                      |

| EDS VLSITechnology and Circuits Committee     Awards & Recognition                                                                                                                                                                               |

| • EDS Member and IEEE Fellow Receives Australia's Highest Honor                                                                                                                                                                                  |

| <ul> <li>2016 IEEE Robert Bosch Micro and Nano Electro Mechanica<br/>Systems Award Winner</li> </ul>                                                                                                                                             |

| <ul> <li>2016 IEEE Robert Bosch Award Call for Nominations</li> <li>2015 EDS J.J. Ebers Award Winner</li> </ul>                                                                                                                                  |

| 2016 EDS J.J. Ebers Award Call for Nominations                                                                                                                                                                                                   |

| 2015 EDS Education Award Winner                                                                                                                                                                                                                  |

| <ul> <li>EDS Members Recently Elected to IEEE Senior<br/>Member Grade</li> </ul>                                                                                                                                                                 |

| <ul> <li>2016 EDS Education Award Call for Nominations</li> <li>2015 EDS Early Career Award Winner</li> </ul>                                                                                                                                    |

| 2016 EDS Early Career Award Willier     2016 EDS Early Career Award Call for Nominations                                                                                                                                                         |

| Congratulations to the Newly Elected IEEE Electron     Devices Society Fellows                                                                                                                                                                   |

| <ul> <li>Status Report from the 2015 EDS Masters and Ph.D.</li> <li>Student Fellowship Recipients</li> </ul>                                                                                                                                     |

| Nominations Due for 2016 EDS Ph.D. Student     Fellowship                                                                                                                                                                                        |

| Nominations Due for 2016 EDS Masters Student<br>Fellowship                                                                                                                                                                                       |

| YOUNG PROFESSIONALS 28                                                                                                                                                                                                                           |

| <ul> <li>Reflections from Young Professionals</li> <li>EDS Education Programs</li> <li>QuestEDS</li> </ul>                                                                                                                                       |

| CHAPTER NEWS                                                                                                                                                                                                                                     |

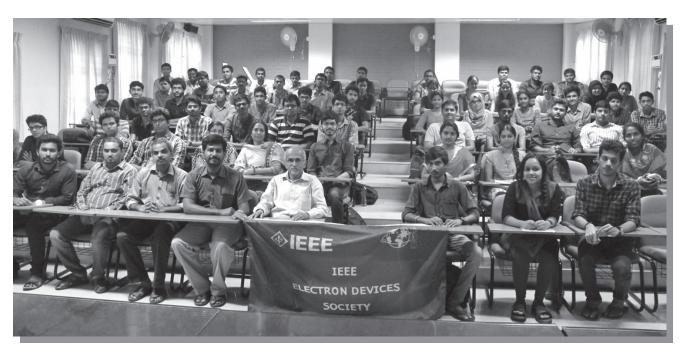

| <ul> <li>MQ, DL and Conference Reports</li> <li>IEEE EDS Mini Colloquium in Bangkok, Thailand</li> <li>ED Poland Chapter Plans IEEE EDS<br/>Mini-Colloquium on GaN HEMTTechnology</li> <li>IEEE EDS DL at NIT Calicut Student Chapter</li> </ul> |

| REGIONAL NEWS                                                                                                                                                                                                                                    |

| EDS MEETINGS CALENDAR                                                                                                                                                                                                                            |

| TRIBUTE TO ANDY GROVE 55                                                                                                                                                                                                                         |

| EDS MISSION, VISION AND FIELDS OF INTEREST 56                                                                                                                                                                                                    |

## TECHNICAL BRIEFS

## TOO HOT TO HANDLE:

Self-heating as an Emerging Performance and Reliability

Concern in Modern Surround Gate Transistors

#### MUHAMMAD A. ALAM

PURDUE UNIVERSITY

#### **Abstract**

By early 2000s, many researchers would begin their talks with an iconic cartoon that superimposed the increasing power dissipation of an IC and that of a rocket nozzle and the Sun. The message was difficult to ignore: the voltage must be scaled to keep power-dissipation at bay. Fast forward to 2015 – the tyranny of short channel effects at the sub 32 nm nodes has led to the development of FINFET and ETSOI technologies, with gate-all-around III-V transistors on the horizon. The short channel effects are controlled, but at the expense of additional self-heating of the system. Stacks of materials (many poor thermal conductors) now surround the very hot channel to make the bad situation worse. In this article, I explain how self-heating redefines and conflates the traditional notions of performance and reliability of ultrathin transistors and frontend and backend issues of modern ICs.

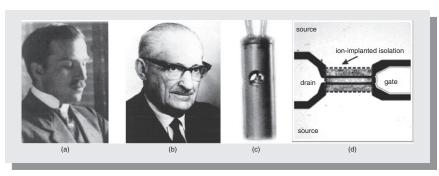

## 1. A Short History of Self-heating: Three Revolutions, Catalyzed by Self-heating

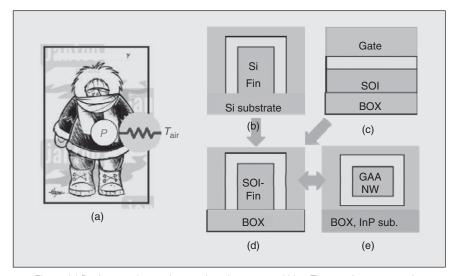

It would be unwise to put on parka in a hot summer day: since  $T - T_{\rm air} = P \times R_{\rm th}$ , even for the same body heat (P), the thermal resistance  $(R_{\rm th})$  of the parka would make self-heating  $(R_{\rm th})$  unbearable. Lately, in desperate pursuit of transistor scaling, we may be surrounding the transistors with similarly poor  $R_{\rm th}$  (see Fig. 1): left unchecked, the self-heating will hurt performance and reliability of the transistors.

Self-heating (SH) spelled the end of first two waves of the electronics revolution (vacuum tubes and bipolar transistors), and one day would do the same for MOSFET, forewarned the experts in 1990s. Unless the exponential rise in *P* is stemmed, the power of

(continued on page 3)

### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

## ELECTRON DEVICES SOCIETY

#### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### **President-Elect**

Fernando Guarin GlobalFoundries E-mail: fernando.guarin@ieee.org

#### **Treasurer**

Subramanian S. Iyer IBM Microelectronics E-mail: iyer@ieee.org

#### Secretary

Simon Deleonibus CEA-LETI E-mail: simon.deleonibus.1992@ ieee.org

#### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Sr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

## Vice President of Membership and Services

Tian-Ling Ren Tsinghua University E-mail: rentl@mail.tsinghua.edu.cn

\_-mail: remisemail:tsingma.eau.cm

## Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: hmomose@ynu.ac.jp

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel E-mail: radhakrishnan@ieee.org

## Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

#### Membership Administrator

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| <u>2016</u>                                                                                      | TERM                                          | <u>2017</u>                                                                                             | TERM                                                 | <u>2018</u>                                                                                         | TERM                                          |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) | Z. Celik-Butler<br>S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose<br>T.L. Ren | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) | N. Bhat<br>D. Camacho Montejo<br>S. Deleonibus<br>M. leong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) |

## NEWSLETTER EDITORIAL STAFF

#### Editor-In-Chief

M.K. Radhakrishnan NanoRel E-mail: radhakrishnan@ieee.org

#### **REGIONS 1-6, 7 & 9**

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

## Central USA & Canada (Regions 4 & 7)

Karim S. Karim University of Waterloo E-mail: kkarim@uwaterloo.ca

## Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

## REGION 8 Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### UK, Middle East & Africa

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

## REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia

E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editor-in-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

#### **NEWSLETTER DEADLINES**

January October 1st

April January 1st

July April 1st

October July 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2016 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

## TOO HOT TO HANDLE

(continued from page 1)

rocket nozzles (1 kW/cm²) will pale in comparison to hotspots in a CPU (per unit area). The community listened; engineers learned to work with lower voltages, tailor voltages and throttle clockspeed on the fly, redesigned critical paths, turned off inactive regions (dark silicon), and learned to spread the work around in multi cores. The result would impress even a casual observer: following a 100fold increase since 1985, P/Area has plateaued to ~100 W/cm<sup>2</sup> since 2005!

We could celebrate, except that the celebration would be premature!

As transistors scaled, the principles of Dennard scaling was supposed to keep the short channel effect (SCE) at bay. Unfortunately, by the early 2000s, it became clear that planar transistors would not do, the industry would have to adopt variants of surround gate technologies to scale to the ultimate limit. Thanks to ingenious processing (e.g., multiple patterning [1], ALD deposited oxides and gate-metal (WN) [2]), surround gate transistors emerged in quick succession (e.g., FinFET, omega-FET, DG-SOI, ET-SOI, Nanowire-FET, and so on, see Fig. 1). Little did we know that the poor thermal conductivity of the oxides and the ubiquity of interfaces, would increase  $R_{th}$ , and eventually lead to a Faustian bargain - increased SCE vs. increased SH, your choice!

### 2. Electrical and Optical Measurements Quantify Self-heating

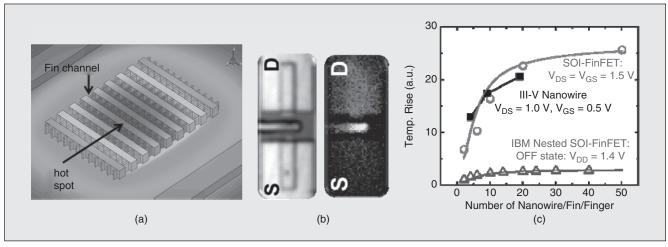

The simulation results in Fig. 2a show three aspects of SH in a SOI-FinFET [3, 4]: 1) significant temperature rise, 2) nonuniform temperature distribution among the NWs, and 3)  $R_{th}$  defined the complex material stack surrounding the transistor. In practice, the channel is hidden from direct view, therefore a set of indirect measurements must be stitched

Fig. 1: (a) Putting a parka on the transistor is not a good idea. The transistor geometries, (b) FINFET, (c) SOI-FET, (d) SOI-FinFET, and (e) GAA NW-FET, have increasingly larger R... Even if P is reduced, the performance and reliability could be a concern.

together to quantify these three aspects of SH.

The electrical characterization of SH may involve (i) monitoring the gate [4] or substrate currents [5], or (ii) inserting local probes (a poly-resistor in the gate, or a test transistor nearby) [6,7], or (iii) measuring the frequency-dependent AC conductance of the self-heated channel [3]. These techniques provide only the Fin-averaged temperature; the calibrations are also tricky, and the measures are often qualitative. The optical/IR measurements offer direct (but somewhat diffused) observation of self-heating; in particular, the newly introduced thermo-reflectance measurement resolves the Fin-specific surface heating (see Fig. 2b), albeit convolved over the emission from neighboring images [3] The electrical and optical measurement interpreted by self-consistent numerical modeling provides a wealth of information for surround gate technologies [8,9], as follows.

### 3. Self-heating vs. transistor geometry

By 2010, when researchers began to quantify SH using a combination of electrical and optical methods, everyone was surprised by its magnitude, the peak location, the time constants, and correlations. Intel [7], TSMC [6], and Samsung [5] focused on FINFETs with a combination of computational modeling, embedded thermal monitors, and statistical analysis of on-current and threshold voltage. The signature of self-heating on drain-current was obvious (4-5 times higher than comparable bulk MOSFETs [5], but the reduced P due to AC cycling, and the reduced  $R_{\rm th}$ due to direct connection to the substrate keep self-heating below 30C. The Backend EM reliability of the local interconnects is affected [6], but rerouting helps.

Unfortunately, these optimistic results do not extend to more advanced designs, namely, III-V Gate-All-Around devices or SOI-FinFET, as shown in Fig. 1 [3, 4]. Here, AC conductance and TR imaging offer nontrivial insights: SH increases  $I_{nn}$  in a contact-resistance limited device [3, Shin], but deceases I<sub>on</sub> in devices limited by channel transport. Without an easy escape to the substrate,  $T_{\text{max}}$  increase to  $\sim 50 - 80 \ C$  due to

Fig. 2 Self-heating depends on transistor configuration and FIN-number: (a) Numerical simulation of SOI-FinFET demonstrates significant self-heating in transistors (Courtesy: S. Koswatta, IBM) (b) TR-imaging of a 19-NW III-V GAA transistor directly measures SH and locates it within the channel, (c) For various surround gate topologies, temperature rises almost linearly until N ~ 10.

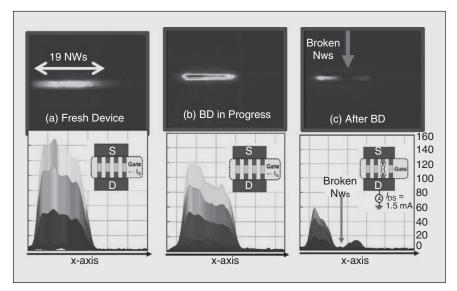

Fig. 3 Dielectric breakdown in GAA-FET requires generalization of classical TDDB concepts. (a) Initially, the middle channel is the most heated, as expected, see Fig. 2. (b) The dramatic increase in heating signals incipient failure. (c) A broken FIN does not break the transistor, but partitions the total current in fewer FINs: the increased current accelerates subsequent failure.

thermal cross talk (see Fig. 2c, and Ref. 4,7,9), and the time-constants span multiple time-scales (ns to  $\mu$ s to ms), as the heat first equilibrates within the channel, then diffuse to the contacts, and eventually escape through the substrate. The memory of SH from the cycles past may shift the threshold voltage and introduce an additional run-time spatio-temporal variability, analogous to the floating body effect for SOI transistors. In this context, a SH friendly

via-design, pre-silicon optimization, and post-Silicon validation [5] can help.

Interestingly (and counterintuitively), the thermal images reported by Shin et al. from Purdue [3] locates the peak of temperature within the channel, see Fig. 2b. Based on classical modeling, many believed that the shorter channel transistors would also be cooler (and more reliable), because the quasi-ballistic electrons

would dissipate their energy in the drain, kept at  $T_{\rm D}=300$  C. In practice, oxides surround source-drain extensions and the significant thermal resistance to the ground increases  $T_{\rm D}>>300$  C: this pair of effects pushes the hot spot back into the channel. The increasing SH within the channel, even within a short channel transistors, must be addressed in transistor redesign.

## 4. Self-heating degrades reliability, the degradation is predictable

Self-heating reduces device lifetime, but more importantly, complicates lifetime projection. Consider, for example, the physics of gate dielectric breakdown (TDDB). Since 1992, three parameters – voltage acceleration, activation energy, and Weibull area/percentile scaling have been sufficient to predict dielectric lifetime [10]. The voltage and temperature differed among various parts of an IC, but was generally uniform over a single transistor.

No longer.

In a 19-Fin device (see Fig. 3a), the central Fin is hotter and therefore degrades faster than its neighbors (Fig. 3b). Once the central FIN fails, the isolation of the neighbors reduces  $R_{\rm th}$ , but the redistribution

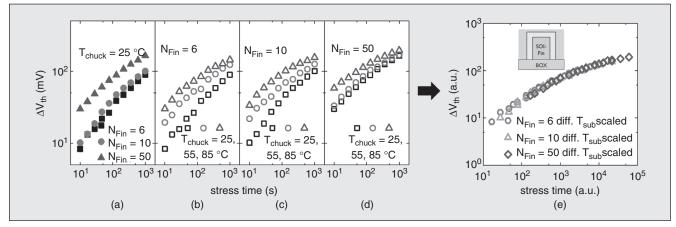

Fig. 4: HCl degradation of SOI-FinFET technologies. (a-d) SH increases with Fin number, and so does the HCl degradation. (e) And yet, the degradation can be scaled to an universal curve, suggesting an opportunity to determine the voltage and temperature acceleration factors for arbitrary number of Fins.

of  $I_{on}$  of the failed FIN among the existing NWs would increase P, with unpredictable effect on Finspecific temperature, and subsequent breakdown. The fundamental physics of TDDB (defect generation terminated by percolation) does not change, but self-heated transistors would need a new formulation and qualification methodology for lifetime prediction.

Often, the reformulation need not be complicated. For example, HCI for FinFET is still correlated to  $I_{sub'}$  as a theormometer of the channel electrons  $T_c$ , [5], and can be used to predict/optimize HCI performance. For gate-all-around devices,  $T_c$  is unavailable, but an equally compelling alternative exists, as follows. We know that HCI of planar transistors depend on  $V_{\rm p}$ , and the time evolution threshold voltage, can be scaled to a universal curve, which in turn allows lifetime prediction based on the a few short-duration stresses [12,13,14]. The scaling concept relies on the idea that  $V_{\scriptscriptstyle D}$  determines SH, which in turn dictates the rate of bond dissociation. Although the origin of SH in surround gate transistors is more complex, the basic physics is the same; it is hardly surprising that the scaling principle holds, see Fig. 4.

### 5. Self-heating correlates performance and reliability

Consider an ET-SOI technology with three different body thicknesses. The thinnest channel offers the best SCE, but its extreme SH reduces I<sub>an</sub> and degrades HCI lifetime. The opposite is true for the thickest transistor. Therefore, SCE and HCI reliability would be optimized at an intermediate thickness [13]. Similar consideration apply to FinFETs; tightly spaced FINs may reduce  $I_{on}$  (and P) per Fin, yet the SH may degrade the overall  $I_{aa}$ and reliability. A somewhat relaxed spacing (fewer fins/per width) may end up improving both performance and reliability of the technology.

Second, SH couples variability and reliability in interesting ways. Among the NWs of a transistor, the one with lowest  $V_{th}$  has higher overdrive ( $V_D$  –  $V_{+}$ ), more self-heating, and faster degradation. This in turn reduces process variability by bringing the threshold voltages together [3].

Finally, all transistor topologies show that the AC-SH is always lower than the DC-SH such that the AClifetime increases with frequency. This is because, although the average temperature is frequency independent, the maximum temperature (which dictates reliability) is not. The reduction in  $T_{\text{max}}$  improves reliability [14].

### 6. Looking ahead: Newer switches, architectures, and brain to the rescue

In the long run, SH should encourage a fundamental rethinking of P and  $R_{th}$ . Device physicists hope to reduce Peither by changing the channel material (Si vs. Ge vs. III-V) or by introducing transistors with steeper subthreshold slope (e.g., NC-FET, tunnel-FET), which operate at lower  $V_{\rm p}$ . The much maligned MOSFET rescued bipolar IC; can the NC-FET or tunnel-FET, similarly rescue MOSFETs, to launch the fourth wave of microelectronics? Similarly, circuit and system designers hope that non-boolean computing paradigms (neuromorphic computing, approximate computing, etc.) will save the day, at least for specialized applications.

In addition to device/system redesign, others propose to focus on reducing  $R_{th}$ : instead of cooling by macroscopic fins and fans, it is better to cool at the source by microscopic techniques involving liquid- or two-phase evaporative cooling [15]. In this regard, the brain provides a paradigm and inspiration. The blood vessels (the interconnect of the brain) deliver power and remove waste heat so effectively that brain maintains its temperature within a fraction of a degree [15,17]. The essence of this exquisite control is the 3D intermeshing

of computing and heat removal, so as to obviate the one-dimensional heat diffusion limit [18]. An electrothermal co-design inspired by the topology and computing paradigm of the brain may eventually be the most effective approach to control of SH in future generation IC's appropriate for the mobile world.

#### **REFERENCES**

- [1] D. Hisamoto et al. "FinFET-a self-aligned double-gate MOSFET scalable to 20 nm." Electron Devices, IEEE Transactions on 47.12 (2000): 2320–2325.

- [2] J.J. Gu et al. "20–80 nm Channel length InGaAs gate-all-around nanowire MOSFETs with EOT= 1.2 nm and lowest SS= 63 mV/dec." Electron Devices Meeting (IEDM), 2012 IEEE International. IEEE, 2012.

- [3] S. Shin et al. "Origin and implications of hot carrier degradation of Gate-all-around nanowire III-V MOS-FETs." In Reliability Physics Symposium, Proc. of IRPS 4A-3, 2014.

- [4] S. O. Koswatta et al. "Off-state self-heating, micro-hot-spots, and stress-induced devices considerations in scaled technologies," IEDM Technical Digest, 20.2.1, p. 539, 2015.

- [5] S. W. Pae et al. Considering Physical Mechanisms and Geometry Dependencies in 14 nm FINFET," IEDMTech. Digest, 20.6.1, p. 557, 2015.

- [6] C. W. Chang et al. Thermal Behavior of Self-Heating Effect in FinFET Devices Acting on Back-end Interconnects", Proc. of IRPS, 2F6.1 2015.

- [7] C. Prasad et al. "Self-heat reliability considerations on Intel's 22 nm Tri-Gate technology", Proc. of IRPS, 2013.

- [8] D. Jang et al. "Self-heating on bulk FinFET from 14 nm to 7 nm node," IEDM Technical Digest, 2015.

- [9] M. Wahab, S. Shin, M. Alam, "3D Modeling of Spatio-temporal Heat-transport in III-V Gate-all-around Transistors Allows Accurate Estimation and Optimization of Nanowire Temperature. Electron Devices, IEEE Transactions on, 62(11), 3595–3604, 2015.

- [10] M. A. Alam et al., "The statistical distribution of percolation resistance as a probe into the mechanics of ultra-thin oxide breakdown" IEDM Tech Digest, 529–532, 2000. Alam, M. A., Smith, R. K., Weir, B. E., & Silverman, P. J. (2002). Thin dielectric films: Uncorrelated breakdown of integrated circuits. Nature, 420(6914), 378–378.

- [11] B. E. Weir et al. "Gate oxide reliability projection to the sub-2 nm regime." Semiconductor Science and Technology 15(5), 455, 2000.

- [12] D. Varghese et al. "OFF-state degradation in drain-extended NMOS transistors: Interface damage and correlation to dielectric breakdown." IEEE TED, 54(10), 2669–2678, 2007.

- [13] S. Shin et al. "Origin and implications of hot carrier degradation of Gate-all-around nanowire III-V MOSFETs." Proc. of IRPS, 2014.

- [14] H. Jiang, S. Shin, and M.A. Alam, "Characterization of Selfheating Leads to Universal Scaling of HCI Degradation of Multi-FIN SOI FinFETs," Proc. of IRPS, 2016.

- [15] P. Patel, "Four New Ways to Chill Chips", IEEE Spectrum, p. 12, Dec. 2015.

- [16] A. L. Sukstanskill and D. A. Yablonskiy, "Theoretical model of

- temperature regulation in the brain during changes in the functional activity", PNAS, 12144–12149, 103(32), 2006.

- [17] H. Wang et al., "Brain temperature and its fundamental properties: a review for the clinical neuroscientists," Frontiers of Neuroscience, vol. 8, Oct. 2014.

- [18] P. Nair and M. Alam, "Diffusion Limits of Biosensors", Applied Physics Letters, 88, 233120, 2006.

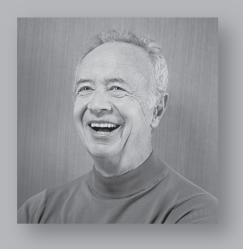

About the author: Professor Alam teaches at Purdue University, where his research focuses on classical and novel semiconductor devices. After

a decade at Bell Laboratories (Murray Hill, NJ) where he made fundamental contributions to IC reliability and optoelectronic ICs, he returned to Purdue University in 2004, where he is now the Jai N. Gupta professor of Electrical Engineering. Today, he works a broad range of topics of emerging electronics, including biosensors, solar cells, and flexible electronics. He has published over 200 papers and discussed his results at many International conferences. He is a fellow of IEEE, APS, and AAAS. His awards include 2006 IEEE Kiyo Tomiyasu Medal for contributions to device technology for communication systems and the 2015 SRC Technical Award for fundamental contributions to reliability physics. Prof. Alam enjoys teaching - more than 100,000 students have learned some aspect of semiconductor physics from his webenabled courses.

## UPCOMING TECHNICAL MEETINGS

# THINGS ARE HEATING UP AT THE 2016 IEEE INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM (IRPS)

APRIL 17–21, 2016

PASADENA CONVENTION CENTER

PASADENA, CA, USA

The International Reliability Physics Symposium (IRPS) is the world's premier forum for leading-edge research addressing developments in the Reliability Physics of devices, materials, circuits, and products. IRPS is the conference where emerging Reliability Physics challenges and possible solutions to achieve realistic End-of-Life projections are first discussed.

For 54 years, IRPS has been the premiere conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and other parts of the world, IRPS seeks to promote the reliability of semiconductor devices, integrated circuits, and microelectronic assemblies through an improved understanding of both the physics of failure as well as the application environment. No other meeting presents as much leading work in so many different areas of reliability of electronic devices, encompassing both silicon and non-silicon devices, process technology, packaging, circuits and systems reliability, optoelectronics, photovoltaics, and MEMS. IRPS 2016 will offer evening panel debates and workshops, invited plenary talks, and an outstanding technical program.

Interconnect and transistor wearout are accelerated by an elevated temperature, and **self-heating** is exacerbated in the most advanced CMOS technologies. IRPS 2016 will feature two invited talks on this criti-

Pasadena's city hall and downtown overview

cally important topic. Prof. Jonathan Malen of Carnegie Mellon University will give an invited talk on Nanoscale HeatTransport in Advanced Semiconductor Devices, and Dr. Baozhen Li of IBM will give an invited talk on Thermal Engineering Challenges for Interconnects in Advanced Processes.

Unsurprisingly, among the reqular submissions to the conference, there included several works that focus on self-heating effects. Two groups of researchers — one from Samsung and the other from Purdue University — will present papers that describe the temperature-accelerated HCI effects in FinFET devices. A group of researchers from Xilinx will present a paper that details a comprehensive circuit reliability simulation tool that includes thermal coupling effects and minimizes overall product risk due to transistor aging and electromigration.

ESD-induced failures often are thermally-precipitated. A researcher

from Intel will present a paper describing a model for ESD-induced heating in interconnect structures.

Wide bandgap (WBG) semiconductors are preferred for high-power applications due to their ability to safely operate at elevated temperatures. At the 2016 IRPS, there will be an entire session devoted to the reliability of WBG semiconductor devices.

The technical program for the 2016 IRPS also includes invited talks on Soft Error in Supercomputers, Product-level Reliability of GaN devices, and Reliability Trojans.

The Convention Center is located in Pasadena's downtown which is best known as the host of the annual Tournament of Roses Parade and Rose Bowl football game. The City also boasts numerous cultural amenities, fine restaurants and top retailers. All this helps Pasadena live up to the true meaning of its name — the Crown of the Valley.

IRPS consists of three days (Tues-Thurs, April 19–21) of plenary and parallel technical sessions presenting original, state-of-the-art work.

Other opportunities at the symposium include:

- Two-Day **Tutorial Program** (Sunday-Monday April 17-18). The IRPS tutorial program is a comprehensive two-day event designed to help both the new engineer and experienced researcher. The tutorial program contains both beginner and expert tracks, and is broken down into parallel tracks dealing with Technology, Component and System reliability challenges, allowing the attendees to participate in tutorials relevant to their work with a minimum of conflicts between subject areas. Among the topics, we are emphasizing this year: **Self-heating effects** on FIN-FET transistors, interaction of component faults and system security, circuit aging effects, Systems reliability comprehending complex applications and selfhealing designs, and Chip-Package interactions in 2.5D and 3D packaging.

- Year in Review Session (Monday April 18). These seminars provide a summary of the most significant developments in the reliability community over the past year. This serves as a convenient, single source of information for attendees to keep current with the recent reliability literature. Industry experts serve as the "tour guide" and save you time by collecting and summarizing this information to bring you up to date in a particular area as efficiently as possible.

- Evening Poster Session. The poster session will provide an additional opportunity for authors to present their original research.

The setting is informal and allows for easy discussion between authors and other attendees.

- Evening Session Workshops.

These workshops enhance the symposium by providing the attendees an opportunity to meet in informal groups to discuss key reliability physics topics with the guidance of experienced moderators. Some of the workshop topics are directly coupled to the technical program to provide a venue for more discussion on the topic.

- Vendor Exhibits. Held in parallel with the technical sessions, the equipment demonstrations provide a forum for manufacturers of state-of-the-art laboratory equipment to present their products. Attendees are encouraged to visit the manufacturers' booths for information and demonstrations.

- IRPS Paper Awards. IRPS bestows awards for Best Paper, Outstanding Paper, Best Poster and Best Student Talk. The Best Paper author is typically invited to present the paper at ESREF in October.

For registration and other information, visit the IRPS 2016 home page at http://www.irps.org/ .

The IRPS committee members look forward to seeing you in April.

Vincent Huard, Publicity Chair STMicroelectronics

Yen-Hao Shih, Publicity Co-Chair — Asia Macronix

> Chris Henderson, General Chair Semitracks Inc.

## 2016 IEEE SYMPOSIUM ON VLSI TECHNOLOGY

The 36th Annual Symposium on VLSI Technology will be held from June 13–16, 2015, at the Hilton Hawaiian Village, Honolulu, Hawaii. This symposium is jointly sponsored by the Japan Society of Applied Physics (JSAP) and the IEEE Electron Devices Society (EDS) in cooperation with the IEEE Solid-State Circuits Society.

VLSI Symposium is a premiere international conference on semiconductor technology defining the pace, the progress and evolution of the microelectronics industry. A unique advantage of this conference is that it is held jointly with the Symposium on VLSI Circuits (June 14–17) at the same location. A single registration covers both symposia. The overlap in the symposia schedules and location offers a platform for interactions between technologists, circuit designers & system architects.

The conference theme this year is "Inflections for a Smart Society."

Symposium scope includes advances, new concepts and breakthroughs in VLSI technology including:

- IoT Systems and Technologies including heterogeneous integration; ultra low power technologies; sensors, display, connectivity; power management; digital/analog, micro-controllers & application processors.

- Stand-Alone and Embedded Memories technology and

reliability for DRAM, SRAM, Non-Volatile, Emerging Memories.

- CMOS Technology, Micro-processors and SoCs including scaling, VLSI manufacturing concepts, and yield optimization.

- RF / Analog / Digital Technologies for mixed-signal SoC; RF front end; analog, mixed-signal, I/O, high-voltage, imaging, MEMS, integrated sensors.

- **Process and Material Technologies** including advanced transistor process and architecture, modeling and reliability; alternate channel; advanced lithography, high-density patterning; SOI and III-V technologies; photonics; local interconnects and Cu/optical interconnects scaling.

- Packaging Technologies and System-in-Package (SiP) including through-silicon-vias (TSVs) and 3D-system integration.

- Photonics Technology and Beyond CMOS Devices

The Symposium on VLSITechnology continues to focus strongly on design/technology co-optimization. In 2016, the conference will offer joint Technology and Circuits focus sessions comprising invited and contributed papers in the following areas:

- Design in scaled technologies: scaling of digital, memory, analog & mixed-signal circuits in advanced CMOS processes

- Design enablement: design for manufacturing, process-design co-optimization, on-die monitoring of variability and reliability

- **Embedded memory technology** and design: SRAM, DRAM, Flash, PCRAM, RRAM, MRAM, etc.

- 3D & heterogeneous integration: power and thermal management, inter-chip communication, system in package (SiP) architectures and applications

- **Smart power**

- Analog/RF integration & design / technology co-optimization in CMOS.

In addition, two technology focus sessions will address:

- System and Embedded memory

- Local, Global and Chip-Chip Interconnects.

The joint evening panel discussion of June 14 will be on the "More Moore, More than Moore or Mo(o)re Slowly". A topic that underlines the soul searching taking place in our industry. While scaling continues, the IC industry faces an inflection that is building on heterogeneous integration of leading-edge and mature technologies driving "smart" system level applications. The technology panel on the same day asks the question on "How Moore's Law, Industry Consolidation and System Trends will shape the Memory Roadmap." Both panels should capture the interest of technologists, designers, business managers and analysts alike.

Every year the Symposium offers professional development opportunities, with a one-day short course on June 13 on "Inflections in VLSI Technology - Cloud and Beyond" including:

- High performance computing

- Future interconnects photonics

- Memory for cloud computing communication

- 3D SOC and 2D hetero-integration

- Power management and devices

- Ultra low power computing

- Non-volatile spin logic and memory

- Neurocomputing

- Sensors: MEMS and bio

- Energy consideration and storage All topics are discussed by leading experts from academia and industry.

In addition, two satellite workshops will be held before the conference: the "IEEE Silicon Nanoelectronics Workshop" and the "Spintronics Workshop" on June 12-13, 2016.

After a successful experience in 2015, the Symposium on VLSI Technology will organize an executive panel on June 15 on "Semi Business beyond Scaling" with leading industry executives to discuss inflections in microelectronics business and future industry drivers that go beyond traditional scaling. The Symposia are recognized for their spirit of international collaboration and informal atmosphere, promoting discussion and debate on new ideas and technology directions.

For further information, complete conference, author, and registration information, please visit the Symposium website at http://www.vlsisymposium.org or contact the following conference secretariats:

(America & Europe) Widerkehr and Associates 19803 Laurel Valley Place Montgomery Village, MD 20886 USA

Tel: +1 301 527 0900 ext. 2 Fax: +1 301 527 0994 E-mail: vlsi@vlsisymposium.org

Secretariat for VLSI Symposia

Secretariat for VLSI Symposia (Japan & Asia) c/o ICS Convention Design, Inc. Chiyoda Bldg. 1-5-18 Sarugakucho

Chiyoda-ku, Tokyo 101-8449, Japan Tel: +81 3 3219 3541 Fax: +81 3 3219 3626 E-mail: vlsisymp@ics-inc.or.jp

We cordially invite you to attend the 2016 Symposium on VLSI Technology to learn about recent state-of-theart advancements in IC technology and to take advantage of enriching technical interactions.

> Symposium Chair: Raj Jammy (USA) Intermolecular

Symposium Co-Chair: Satoshi Inaba (Japan) Toshiba Electronics Korea

> Program Chair: Mukesh Khare (USA) **IBM**

Program Co-Chair: Meishoku Masahara (Japan) **AIST**

## 2016 IEEE COMPOUND SEMICONDUCTOR IC Symposium

OCTOBER 23RD-26TH, IN AUSTIN, TEXAS

PAPER SUBMISSION DEADLINE: APRIL 22, 016

We cordially invite you to the 2016 IEEE Compound Semiconductor IC Symposium (CSICS) being held October 23rd-26th at the Doubletree by Hilton Hotel located in Austin, Texas, USA. Since its inception in 1978, the Symposium has become a pre-eminent international forum for developments in compound semiconductor circuit and device technology. The scope of the Symposium encompasses devices and circuits, embracing GaAs, SiGe, InP, GaN, InSb, and CMOS technology to provide a truly comprehensive conference. CSICS is the ideal forum for presenting the latest results in microwave/mm-wave, high-speed digital, analog, mixed mode, THz, power conversion, and optoelectronic and Silicon Photonics integrated circuits.

The 2016 CSIC Symposium is comprised of a full 3-day technical program, two short courses, a primer course, and a technology exhibition. The technical program includes approximately 60 high quality technical papers. Invited papers and panel sessions on topics of current importance to the Compound Semiconductor IC

community greatly enrich the technical program. In addition, the Symposium will continue the tradition of including important "late breaking news" papers. The short courses on Sunday, October 23rd provide the attendees the opportunity to learn from world-renowned instructors in their respective areas of expertise. The Sunday introductory-level primer course will provide attendees insight into the design of principal RF and high speed IC building blocks, emphasizing the specific background

needed to understand and appreciate the technical program.

The technology exhibition will be held on Monday and Tuesday, featuring informative and interesting displays with corporate representatives on hand. The list of exhibitors can be found in the CSICS advance program to be published in late June. To complement the Symposium, there are several social events including the Sunday Evening CSICS Opening Reception, the Monday CSICS Exhibition Opening Reception, and the Tuesday CSICS Exhibition Luncheon. Breakfasts and coffee breaks will be served on Monday, Tuesday, and Wednesday.

For registration and up-to-date information, please visit the CSICS website at www.csics.org. Further questions may be addressed to the Symposium Chair: Chip Moyer, HRL Laboratories, Phone: 1-310-487-3290, E-mail: hpmoyer@hrl.com.

We hope you can attend, 2016 IEEE CSICS Organizing Committee

> Thé Linh Nguyen 2016 CSICS Publicity Chair Finisar Corporation

## 2016 IEEE International Semiconductor Conference (CAS)

The 39th International Semiconductor Conference (CAS 2016) will be held in Sinaia (Romania), October 10–12, 2016. The conference is focused on developments in micro-and nanotechnologies. For the 2016 edition, papers are expected in the following domains:

- Nanoscience and Nanoengineering

- Micro- and Nanophotonics, and Optoelectronics

- Microwave and Millimeter Wave Circuits and Systems

- · Microsensors and Microsystems

- Modelling

- Semiconductor Devices

- Integrated Circuits

- Physics of Materials

The CAS conference was originally launched in 1978. Until 1996 it was organized as the *Annual Semiconductor Conference* (in Romanian – Conferinta Anuala de Semiconductoare – CAS). Since 1991 it has become available to the international scientific

community and has changed its name accordingly to *International Semiconductor Conference*, still keeping the acronym (CAS). In 1995, the conference became an IEEE event, sponsored by the IEEE Electron Devices Society. Since 1997, it has been organized by the National Institute for Research and Development in Microtechnologies (IMT Bucharest).

IMT Bucharest is supervised by the Romanian Ministry of Education and

Scientific Research. It is the first institute with this profile in Eastern Europe and the main actor in microtechnologies in Romania. IMT mission consists of research and development in micro-, nano-, biotechnologies, education and training, knowledge dissemination and technology transfer. Between 2003 and 2015, IMT was involved in approximately 45 European projects (FP6, FP7 and related).

The CAS Conference agenda includes plenary sessions with invited papers and regular sessions. The regular papers are selected for both oral and poster sessions. A Student Paper Session is also organized and the Best Student Paper Award is given every year by the IEEE ED Romania Section Chapter. The invited papers and accepted papers will be published in CAS 2016 Proceedings (an IEEE publication). All accepted and presented papers will appear in the IEEE Xplore data base.

The CAS2016 event is a milestone for the members of the IEEE ED Romania Chapter. Thanks to the efforts of the EDS team, our chapter attracted ten new members in 2016. The chapter growth is stimulated by the annual CAS forum, where our EDS members find a prolific scientific environment. For a call for papers and further information regarding the CAS2016 conference, please visit the CAS website http://www.imt.ro/cas/.

For additional information contact us at e-mail address cas@imt.ro.

Prof. Dan Dascalu (dan.dascalu@imt.ro) CAS General Chairman Member of the Romanian Academy IEEE EDS Senior Member IMT Bucharest, Romania

> Cristian Ravariu (cristian.ravariu@gmail.com) IEEE ED Romania Section Chapter Chair Polytechnic University of Bucharest, Romania

~Editor, Daniel Tomaszewski

## THE 62ND ANNUAL IEEE INTERNATIONAL ELECTRON DEVICES MEETING (IEDM)

**DECEMBER 5-7, 2016**

HILTON SAN FRANCISCO UNION SQUARE HOTEL

IEDM is the world's pre-eminent forum for technological breakthroughs in the areas of semiconductor and electronic device technology, manufacturing, design, physics, and modeling. The world's leading scientists and engineers will gather for a technical program of more than 220 presentations, along with panel sessions, tutorials, short courses, and other events spotlighting more leading work in more areas of the field than any other conference.

New in 2016: To provide faster dissemination of the conference's cutting-edge results, the abstract submission deadline has been moved to August 10th for submission of four-page, camera-ready abstracts. Accepted papers will be published as-is in the proceedings.

Papers in the following areas are encouraged:

- Circuit and Device Interaction

- · Characterization, Reliability and Yield

- Compound Semiconductor and High Speed Devices

- Memory Technology

- Modeling and Simulation

- Nano Device Technology

- · Optoelectronics, Displays, and Imagers

- Power Devices

- Process and Manufacturing Technology

- · Sensors, MEMS and BioMEMS

For more information, visit the IEDM website: www.ieee-iedm.org

## SOCIETY NEWS

## NEWLY ELECTED EDS OFFICERS AND BOG

### ANNOUNCEMENT OF **NEWLY ELECTED OFFICERS** & BoG MEMBERS

Paul Yu **EDS Nominations** and Elections Chair

In 2015, EDS continued the pilot program and had one of the seven BoG Member-at-Large seats elected via the entire EDS membership. The remaining six seats and officer positions were

voted on by our BoG during the election, which took place on December 6, 2015, at the Washington Hilton in Washington, DC. The following are the results of the election and brief biographies of the individuals elected.

#### **OFFICERS**

The following individuals were elected as officers for a two-year term beginning January 1, 2016:

#### President-Elect

Fernando Guarín is a Distinguished Member of Technical Staff at Global Foundries in East Fishkill, New York, and Adjunct Lecturer at SUNY New

Paltz. He retired from IBM's SRDC after 27 years as Senior Member of Technical Staff. He earned his BSEE from the "Pontificia Universidad Javeriana", in Bogotá, Colombia, the M.S.E.E. degree from the University of Arizona, and the Ph.D. in Electrical Engineering from Columbia University, New York. He has been actively working in microelectronic reliability for over 35 years.

From 1980 until 1988 he worked in the Military and Aerospace Operations division of National Semiconductor Corporation. In 1988 he joined IBM's microelectronics division where he worked in the reliability physics and modeling of Advanced Bipolar, CMOS and Silicon Germanium BiCMOS technologies.

Dr. Guarín is an IEEE Fellow and Distinguished Lecturer for the IEEE Electron Devices Society, where he has served in many capacities including; member of the IEEE's EDS Board of Governors, Chair of the EDS Education Committee, and Secretary for EDS. He is the President-Elect 2016-2017.

#### Secretary

Simon Deleonibus, retired from CEA-LETI on January 1, 2016, as Chief Scientist after 30 years of Research on Micro Nanoelectronics Devices Architectures.

He was with Thomson Semiconductors (1981-1986) where he developed and transferred to production advanced microelectronics devices. He gained his PhD in Applied Physics from Paris University (1982).

He is Visiting Professor at Tokyo Institute of Technology (Tokyo, Japan) since 2014, Visiting Professor at National Chiao Tung University (Hsinchu, Taiwan) since 2015. He was distinguished CEA Research Director (2002), IEEE Distinguished Lecturer (2004), Fellow of the IEEE (2006), Fellow of the Electrochemical Society (2015).

Simon was awarded the titles of Chevalier de l'Ordre National du Merite (2004) and Chevalier de l'Ordre des Palmes Academiques (2011), the

2005 Grand Prix de l'Academie des Technologies.

He is member of the ITRS (1998), the European Research Council Panel (2007), the Nanosciences Foundation Board of Trustees (2007).

He was Associate Editor of IEEE Transactions on Electron Devices (2008-2014) and a member of the IEEE Electron Devices Society Board of Governors (January 2009 - December 2014) and re-elected (2016-2018). He is currently Secretary (2016-2017) and Region 8 SRC Chair (2015-2016) of the IEEE Electron Devices Society.

#### Treasurer

Subramanian S. Iver (Subu) is Distinguished Chancellor's Professor in the Electrical Engineering Department at the University οf

California - Los Angeles, where he is director of the Center for Heterogeneous Integration and Performance Scaling (CHIPS). He obtained his B.Tech. from IIT-Bombay, and Ph.D. from UCLA and joined IBM, where he was appointed IBM Fellow and was till recently Director of the Systems Scaling Technology Department. His key technical contributions have been the development of the world's first SiGe base HBT, Salicide, eFuses, eDRAM, 45 nm technology used at IBM and IBM's development partners and 3-Dimensional Integration. He cofounded SiBond LLC to develop SOI substrates. He has published over 250 papers and holds over 70 patents. He has received several outstanding technical achievements and corporate awards at IBM. He is an IEEE Fellow and a Distinguished Lecturer of the IEEE EDS. He is a Distinguished Alumnus of IIT Bombay and received the IEEE Daniel Noble Medal in 2012.

#### **BoG MEMBERS-AT-LARGE** Second Term Electees:

**Daniel Mauricio** Camacho received his BSEE for Pontificia Universidad Javeriana, in Bogota, Colombia, in 2007, and his Masters degree

from Southern Methodist University in Dallas, Texas in 2009. In 2008, he was awarded the IEEE EDS Masters Student Fellowship for his research work. He joined Intel in 2010, where he has been since then. His area of expertise is design of high-performance analog and mixed signal circuits. He has been a member of the EDS Board of Governors since 2013, he is also the current chairman of the EDS Young Professionals Committee.

Doug Verret was a high school teacher of math and physics from 1969-1974 and an instructor, then Assistant Professor of Physics and Pre-engineer-

ing from 1974-1979 at Xavier University, New Orleans, Louisiana. He joined Texas Instruments Inc. in 1979.

He has held several positions at Texas Instruments, the most recent of which was Program Manager for Flash EEPROM Development in which role his team developed micro-controller products with embedded flash for the automotive, safety and IOT markets. Prior to that, he was Program Manager in charge of developing technology for FPGA products. He has sixteen US patents covering such diverse technologies as Cu interconnects, deep trench isolation, polysilicon emitters, advanced bipolar devices and BiCMOS technology.

He was MOS Devices and Technology editor for the IEEE Transactions on Electron Devices 1994-2000 and Editor-in-Chief 2000-2011. He received the Electron Devices Society 2012 Distinguished Service Award.

#### First-Time Electees:

Navakanta Bhat received his Ph.D. in Electrical Engineering from Stanford University, in 1996. Then he worked at Motorola's Advanced

Products R&D Lab in Austin, Texas until 1999. He is currently a Professor at the Indian Institute of Science (IISc), Bangalore. His current research is on Nanoelectronics and Sensors. He has more than 200 publications and 20 patents. He was instrumental in creating the National Nanofabrication Centre (NNfC) at IISc, benchmarked against the best university facilities in the world. He is the recipient of IBM Faculty award and Outstanding Research Investigator award (Govt. of India). He is a Fellow of INAE. He was the Editor of IEEE Transactions on Electron Devices, during 2013-2016. He is a member of the National Innovation Council in Nanoelectronics. He is the founder and promoter of a startup called "PathShodh Healthcare," which builds point-ofcare diagnostics for diabetes and its complications.

Simon Deleonibus retired from CEA-LETI on January 1, 2016, as Chief Scientist after 30 years of Research on Micro Nanoelectronics Devices Architectures.

He was with Thomson Semiconductors (1981-1986) where he developed and transferred to production advanced microelectronics devices. He gained his PhD in Applied Physics from Paris University (1982).

He is Visiting Professor at Tokyo Institute of Technology (Tokyo, Japan) since 2014, Visiting Professor at National Chiao Tung University(Hsinchu, Taiwan) since 2015. He was distinguished CEA Research Director (2002), IEEE Distinguished Lecturer (2004), Fellow of the IEEE (2006), Fellow of the Electrochemical Society (2015).

Simon was awarded the titles of Chevalier de l'Ordre National du Merite (2004) and Chevalier de l'Ordre des Palmes Academiques (2011), the 2005 Grand Prix de l'Academie des Technologies.

He is member of the ITRS (1998), the European Research Council Panel (2007), the Nanosciences Foundation Board of Trustees (2007).

He was Associate Editor of IEEE Transactions on Electron Devices (2008-2014) and a member of the IEEE Electron Devices Society Board of Governors (January 2009 December 2014) and re-elected (2016-2018). He is currently Secretary (2016-2017) and Region 8 SRC Chair (2015-2016) of the IEEE Electron Devices Society.

Meikei leong is currently Chief Technology Officer at Hong Kong Applied Science and Technology Research Institute (ASTRI). Prior to

this, he has held various engineer and leadership positions in Taiwan Semiconductor Manufacturing Company (TSMC) and IBM Research. He holds a PhD degree in Electrical and Computer Engineering from University of Massachusetts, Amherst and an MBA degree from the MIT Sloan Fellows Program at MIT School of Management.

Dr. leong was General Chairman of the IEEE International Electron Devices Meeting (IEDM). He has served as an editor for the IEEE Transaction on Electron Devices since 2010 and as chair of the IEEE EDS Education Award Committee since 2013. He has published more than one hundred papers in referred journals and conference proceedings and more than eighty patents. He is an IEEE Fellow in recognition of his leadership and contributions to Complementary Metal-Oxide-Semiconductor (CMOS) Device Technology.

Murty Polavarapu is a semiconductor industry consultant in Oakton, Virginia, USA. He has recently retired from BAE Systems follow-

ing a long career in developing advanced memory and logic products for defense and aerospace markets. His experience also includes introduction of advanced DRAM and Flash memory products into commercial manufacturing at Toshiba and Micron. He holds Masters degrees in Physics from India, Electrical Engineering from Howard University and Technology Management from the University of Pennsylvania. He has been an active IEEE volunteer at EDS, Nanotechnology Council, IEEE-USA and Member and Geographic Activities. Polavarapu also served as a United States Peace Corps volunteer teacher in rural Fiji on a leave of absence. He has been recognized with IEEE Regional Activities Achievement Award, Dominion Semiconductor President's Award and IBM Outstanding Technical Achievement Award. He has been awarded eleven US patents.

Ravi Todi received his M.S. degree in Electrical and Mechanical Engineering from University of Central Florida in 2004 and 2005 respectively,

and his doctoral degree in Electrical Engineering in 2007. His graduate research work was focused on gate stack engineering, with emphasis on binary metal alloys as gate electrode and on high mobility Ge channel devices. In 2007, he started working as Advisory Engineer/Scientist at Semiconductor Research and Development Center at IBM Microelectronics Division focusing on high performance eDRAM integration on 45 nm SOI logic platform. Starting in 2010, Ravi was appointed the lead Engineer for

22 nm SOI eDRAM development. For his many contributions to the success of eDRAM program at IBM, Ravi was awarded IBM's Outstanding Technical Achievement Award in 2011, Ravi Joined Qualcomm in 2012, responsible for 20 nm and 16/14 nm product developments. Currently Ravi is Director of Product Management at GLOBALFOUNDRIES. He is a Distinguished Lecturer for the IEEE Electron Devices Society and serves as Editor for IEEE Transactions on Electron Devices. Ravi had authored or coauthored over 50 publications, has over 10 issued US patents and over 25 pending disclosures. He has also served as an Officer/Treasurer for four vears (2012-15) for EDS.

I welcome all electees and urge them to get fully engaged in the affairs of the Electron Devices Society. EDS is considered to be a volunteerled, volunteer-driven organization and we expect nothing less from all to continue this tradition.

Paul Yu EDS Nominations and Elections Chair University of California, San Diego La Jolla, CA, USA

## Message from EDS President Elect

Fernando Guarin President Elect (2016-2017)

Dear Readers and EDS Members,

It is a true honor and privilege to write to you as the EDS President Elect 2016–2017. I am grateful for the trust the voting members have

placed in me and vow to make every effort to continue the fine example set by those who have preceded me in the EDS Presidency. The Electron Devices Society embodies a proud history of tangible contributions that have transformed society, changing the world in which we live. It is difficult to think of any other technical society that has had such a deep impact on the world. EDS has profoundly changed our ability to communicate, transport, heal, trade, power, compute, sense, control, display information and miniaturize, to name but a few of the applications enabled by advances in electron based devices. This transformation was made possible by

the hard work, talent, ingenuity, publications, inventions, educational activities and solid technical foundation of our members. It is the job of the president to enable the continuation of the following outstanding contributions; fostering the dissemination of high quality technical information, bringing a cohesive force that represents the interest of our members throughout the world, providing added value to our members and thus continuing to promote excellence in the field of electron devices for the benefit of humanity.

#### My vision for the IEEE Electron **Devices Society**

Continue to work hard to increase EDS's leadership and relevance of our core areas:

- Publications

- Conferences

- Education

- Membership

- Awards and Chapters

I believe in increasing EDS's leadership and relevance, with measures that include:

- Strengthening our ties to academia - with better service to student's needs.

- · Strengthening EDS ties to industry - to keep EDS technical areas relevant and enable our society to better serve our members in industry.

- Undertaking and supporting more high visibility projects, especially humanitarian and Smart Planet projects that visibly demonstrate EDS's commitment to its mission.

- The technology world is changing quickly. Internet magazines, social media, and Open Access publishing are allowing other players to provide significant value to technical professionals - which lessen the IEEE's EDS perceived value. We need to strengthen our publications and conferences while striving to create and provide more value for our EDS members.

- I support enhancing the networking and collaboration opportu-

nities for members through use of social media and web based tools, thus demonstrating that EDS can successfully provide value in this space.

I am passionate about the success of EDS and will do may best as EDS President-Elect to increase EDS membership, enable the professional growth of our members, provide increased value to all our members in education, recognizing achievements while living up to IEEE's motto of Advancing Technology for Humanity.

> Fernando Guarin President Elect (2016-2017) Global Foundries East Fishkill, New York, USA

## Message from Editor-IN-Chief

M.K. Radhakrishnan Editor-in-Chief

Dear EDS Members and Readers,

One of the challenging issues with electron devices is the heating. The technical article in this issue of the Newsletter discusses the

self-heating aspects of surround gate transistors, especially in view of reliability and performance. This is the third invited article in the area of device reliability in our Technical article series. The first was "Reliability trends in Nano-scale CMOS" followed by "ESD during times of change" and now "Too hot to Handle". We would like to hear the views of readers about these and we request your suggestions for future topics. The idea

behind publishing such technical articles by experts which are so digestible to any reader is to make everyone aware of the developments as well as challenges in the field.

Election to the newly arising positions in the Board of Governors was held during the December 2015 BoG meeting. An introduction of newly elected members is given in this issue. Also, we are announcing the details of various awards won by our members both within IEEE as well as elsewhere. A notable one is Australia's highest National Honor received by our active volunteer Prof. C. Jagadish of Australian National University and is featured in this issue. In the Young Professionals section we feature an interview with the EDS 2015 Early Career Award winner.

As I have repeatedly mentioned in this column, the feedback from readers is very much missing. The entire Newsletter team including editors and all support team members would like to hear from the readers. It is not difficult to make a comment. as the Newsletter is now available in electronic version and accessible to everyone.

Again, we all are looking for readers' views, comments, criticisms as well as suggestions, which only can make this Newsletter robust. And I request all the readers to write the feedback to edsnewsletter@ieee.org OR to me radhakrishnan@ieee.org.

> MK Radhakrishnan Editor-in-Chief, EDS Newsletter e-mail: radhakrishnan@ieee.org

## TECHNICAL COMMITTEE REPORTS

## EDS VLSI TECHNOLOGY AND CIRCUITS COMMITTEE

On December 5, 2015, the VLSI Technology and Circuits Committee met in Washington, D.C., USA, during the 2015 IEEE International Electron Devices Meeting (IEDM) on December 7–9.

The VLSI Technology and Circuits Technical Committee was formed in 1998 under the leadership of Professor Charles G. Sodini (MIT), followed by Dr. H.-S. Philip Wong (IBM), Werner Weber (Infineon), Dr. James A. Hutchby (SRC), and Dr. Bin Zhao (Freescale Semiconductor). Since its formation, the VLSI Committee has made it their mission to identify new technical trends, help foster new technical concepts, and serve the emerging needs of the Electron Devices and Solid-State Circuits communities in VLSI. The committee members include many well recognized technical experts representing a very wide spectrum of technical expertise in VLSI devices, technology, and circuits.

The objective of the VLSI Technology and Circuits Committee is to identify new and relevant areas of interest to the Electron Devices and Solid-State Circuits communities.

Based on the nature of the areas, the committee recommends any or all of the following:

- Initiate topical workshops of current interest (attached to existing conferences or incorporated in new ones)

- 2. Special issues for major publications (e.g., T-ED)

- Panel session topics, Invited talks and Special sessions for major conferences

The following topics were discussed during the December 5, 2015 meeting:

- 1. Membership

- a. The committee's current twenty eight geographically diverse members include:

- i. North America ten members

- ii. South America one member

- iii. Europe five members

- iv. Africa one member

- v. Asia eleven members

- b. Candidates for committee members starting in January of 2016 were discussed and agreed upon awaiting further approval.

The committee now has representatives from Asia, North/South America, Africa and Europe.

- Sub-Committees Roles and responsibilities of the following subcommittees were discussed:

- a. Publication Chair: Steve Chang

- b. Conferences/Workshops Chair:Kaz Ishimaru

- c. Publicity Chair: Seiichiro Kawamura

Discussion was made to make a proposal on a special issue of T-ED on next generation of devices to replace 3-D Tri-Gate transistors and Novel Memories.

Please contact Dr. Kaz Ishimaru (kazu.ishimaru@toshiba.co.jp), conferences/workshops subcommittee chair, or Dr. Shu Ikeda (shu.ikeda@tei-solutions.com), committee chair, for further information.

Reza Arghavani EDS VLSITC Committee Member Lam Research Corporation Fremont, CA, USA

Standing from left to right – Hitoshi Wakabayashi, Min Yang, Mansun Chan, Steve S. Chung, Simon Deleonibus, Seiichiro Kawamura, Shuji Ikeda, Kazunari Ishimaru, Reza Arghavani, Jacobus Swart, Hiroshi Iwai.

## EDS MEMBER AND IEEE FELLOW RECEIVES AUSTRALIA'S HIGHEST HONOR

Chennupati Jagadish

Professor Chennupati Jagadish, of Australian National University, has been awarded Australia's highest honor for his service to physics and engineering in the 2016 Australia Day Honors. Profes-

sor Jagadish was appointed a Companion of the Order of Australia (AC) for eminent service to physics and engineering, particularly in the field of nanotechnology, to education as a leading academic, researcher, author and mentor, and through executive roles with national and international scientific advisory institutions. Jagadish said he was humbled, honored and grateful for this honor. "This is a wonderful recognition for 25 plus years of work with my research group at the ANU," said Jagadish, who works on semiconductor optoelectronics and nanotechnology.

With his research in nanotechnology, he is helping to develop a new class of lasers with applications in telecommunications and new lightweight solar cells with increased efficiency. Most interesting is the research on neuromorphic cells - artificial, trainable neurons - or "brain on a chip."

On receiving the honor, Jagadish said "I feel very, very humbled to receive this honor and I owe it to the teachers in my school days in rural India, who made such a huge difference to my life." Jagadish and his wife Vidya

started the Chennupati and Vidya Jagadish endowment at the Australian National University to support visiting students and researchers from developing nations to visit ANU for 3-4 months, to carry out research in the Research School of Physics and Engineering.

Jagadish, a professor of physics at the Australian National University, is also the vice-president of the Australian Academy of Science and founded the Australian Nanotechnology Network, which has more than 1,400 members. He is a dedicated EDS volunteer and an IEEE Fellow.

> M.K. Radhakrishnan Editor-in-Chief, EDS Newsletter

## 2016 IEEE EDS ROBERT BOSCH MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD WINNER

The 2016 IEEE EDS Robert Bosch Micro and Nano Electro Mechanical Systems Award, was presented to Professor Henry Baltes, ETH Zurich, Zurich, Switzerland, at the MEMS2016 Conference in Shanghai, China, on January 26, 2016. This prestigious award recognizes and honors advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices.

For contributions to the exploration and development of CMOS-MEMS, to production using IC foundries and MEMS post-processing, and for inspirational leadership in the worldwide MEMS community

Henry Baltes is Professor Emeritus of ETH Zurich affiliated with Micro- and Nanosystems at the Department of

Mechanical Process Engineering. He was Professor of Physical Electronics at ETH Zurich and Director of the Physical Electronics Labo-

ratory from 1988 to 2006. In 2004-05 he was in charge of starting the new Department of Biosystems Science and Engineering (D-BSSE) of ETH Zurich located at Basel. He is a Member of the Swiss Academy of Technical Sciences and a co-founder of the sensor manufacturer SENSIRION.

He received the Koerber European Science Award, the Wilhelm Exner Medal of the Austrian Trade Association, and the Swiss Technology Award. He holds honorary doctoral degrees of the Universities of Waterloo (Canada), Bologna (Italy), Freiburg (Germany), and University College London (UK).

From 1983 to 1988 he held the Henry Marshall Tory Chair in Electrical Engineering at the University of Alberta, Edmonton, Canada. He was acting President of the Alberta Microelectronic Centre and a co-founder and Director of LSI Logic Corporation of Canada. From 1973 to 1982 he worked for a Swiss company and taught at EPF Lausanne. He received the degree of Doctor of Science of ETH Zurich in Physics in 1971.

He served as Co-Chair of the 14th IEEE International Conference on MEMS, held at Interlaken in 2001. He was elected Fellow of the IEEE in 2003 for contributions to the development and commercialization of CMOS based MEMS and won the IEEE Donald G. Fink Prize Paper Award 2005. He served on the Editorial

Board of the Proceedings of the IEEE in 2004–09. He also served on IEEE IEDM, IEEE Sensors, and Transducers conference committees.

Richard Muller EDS Bosch Award Chair University of California, Berkeley Berkeley, CA, USA

## **IEEE ROBERT BOSCH** MICRO AND NANO ELECTRO MECHANICAL SYSTEMS AWARD

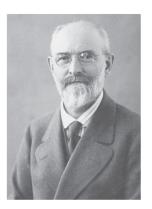

## Robert Bosch (1861-1942) Inventor, Entrepreneur, Founder of Robert Bosch GmbH

The Robert Bosch Micro and Nano Electro Mechanical Systems Award, was established by the IEEE Electron Devices Society in 2014 to recognize and honor advances in the invention, design, and/or fabrication of micro- or nano-electromechanical systems and/or devices. The contributions to be honored by this award should be innovative and useful for practical applications.

This award is sponsored by the IEEE Electron Devices Society with financial support from Robert Bosch LLC. It is intended that the award will be presented annually to an individual or to as many as three individuals whose achievements and contributions are judged to meet the selection criteria for the award. The award will be presented at an IEEE conference of the winner's choice. It is not necessary for the recipient(s) to be a member(s) of IEEE.

The recipient will receive a US\$10,000 honorarium (which includes up to \$3,000 of travel expenses for international travel and \$1,500 of travel expenses for domestic travel), a bronze medal, and a certificate. In the event that more than one awardee is selected, the cash honorarium will be equally divided among the recipients. Each recipient will receive a bronze medal and a certificate.

Please visit the EDS website for more information on this award: http://eds.ieee.org/robert-boschmicro-and-nano-electro-mechanical-systems-award.html.

Nominations for the 2017 award should be made using our online nomination form (available on the EDS webpage noted above), and submitted before midnight (EST) on October 2<sup>nd</sup>. Letters of recommendation must be sent directly to l.riello@ieee.org according to the same schedule.

## 2015 EDS J. J. EBERS AWARD WINNER

The 2015 J. J. Ebers Award, the prestigious Electron Devices Society award for outstanding technical contributions to electron devices, was presented to Dr. Jack Yuan-Chen Sun of TSMC, HsinChu, Taiwan, at the IEEE International Electron Devices Meeting in Washington, DC, on December 7, 2015. This award recognizes Dr. Sun "For sustained leadership and technical contributions to energy efficient foundry CMOS technologies."

Dr. Jack Yuan-Chen Sun received BSEE degree from National Taiwan University and MS and Ph.D. from the University of Illinois. He held research and management positions at IBM T. J. Watson Research Center between 1983 and 1997. He joined TSMC R&D in 1997 as Director of Advanced Module Technology, and

Dr. Jack Yuan-Chen Sun receiving the J. J. Ebers Award at the 2015 IEDM

then Senior Director of Logic Technology. He became Vice President of R&D in 2006 and Chief Technology Officer at TSMC in 2009.

He made key contributions to the successful energy efficient CMOS logic SOC platforms with highest routed gate density and computation throughput for the foundry/ fabless industry atTSMC. He advocated a holistic energy efficient 3D × 3D system scaling concept. Throughout his career, he and his co-workers pioneered and set many world records in CMOS, bipolar, and BiCMOS.

Dr. Sun received a number of technical and management awards from IBM, TSMC, professional societies, and government. He was awarded a TSMC Medal of Honor in 2011. He is an IEEE Fellow for his contributions to CMOS technology. He has authored and co-authored over 200 papers and conference presentations, 12 US patents, and several ROC patents.

> Jayant Baliga EDS J.J. Ebers Award Chair North Carolina State University Raleigh, NC, USA