JANUARY 2016 VOL. 23, NO. 1 ISSN: 1074 1879

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

### TABLE OF CONTENTS

| •Trends in Device Research – IEDM 2015 Highlights |

|---------------------------------------------------|

| UPCOMING TECHNICAL MEETINGS                       |

| SOCIETY NEWS                                      |

| YOUNG PROFESSIONALS                               |

| CHAPTER NEWS                                      |

| REGIONAL NEWS 40                                  |

# **PIEEE**

EDS MEETINGS CALENDAR......50

# TECHNICAL BRIEFS

# TRENDS IN DEVICE RESEARCH - IEDM 2015 HIGHLIGHTS

Advanced research trends in devices and their application are always reported at IEDM annually. Scientists and technologists at all levels from industry as well as academia always assemble at IEDM and sharpen their ears to hear the new results and innovations from laboratories around the world. The IEEE EDS Newsletter captures some of the key presentations at IEDM 2015 and is summarized here. These include novel devices using both silicon and hetero structures for various applications including sensing, imaging and Internet of Things (IoT). Full texts of the IEDM papers are available at the IEDM Technical Digest in IEEEXplore (ieeexplore. ieee.org/)

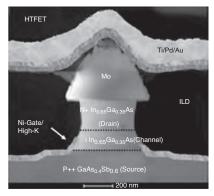

Difficulty seeing nanoscale transistor features? Well, a Penn State researcher has said goodbye to microscopes and hello to atom probe tomography. Tunneling field-effect transistors (TFETs) are promising for ultra-low-power applications, but improvements in their performance and reliability are needed. Critical to TFET performance when they are made from combinations of III-V materials is the need for abrupt and uniform interfaces among the dissimilar materials. Variability at these interfaces, or heterojunctions, reduces device performance and it is difficult to characterize heterojunctions with precision in nanometer-scale devices, but a Penn State team used atom probe tomography and time-of-flight spectroscopy to do so. First they cooled TFET samples to 50° Kelvin. Then, they rapidly heated the heterojunction under study with laser pulses to evaporate layers of atoms from it, one layer at a time. They captured the atoms from each layer in an electric field, and then performed spectroscopic analysis to identify the individual atoms, which constituted each layer. From all this data they built a 3D map of the heterojunction, with a resolution of 2.4 nm. Then, they rested. The study was reported in Paper 14.2, Tunnel Junction Abruptness, Source Random Dopant Fluctuation and PBTI Induced

(continued on page 3)

## YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

# ELECTRON DEVICES SOCIETY

### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

### **President-Elect**

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

#### Treasurer

Subramanian S. Iyer IBM Microelectronics E-mail: iyer@ieee.org

### Secretary

Simon Deleonibus CEA-LETI

E-mail: simon.deleonibus@cea.fr

### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

### Sr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

# Vice President of Membership and Services

Tian-Ling Ren Tsinghua University

E-mail: rentl@mail.tsinghua.edu.cn

# Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: hmomose@ynu.ac.jp

### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

# Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

### **Executive Director**

Christopher Jannuzzi IEEE Operations Center E-mail: c.jannuzzi@ieee.org

### Membership Administrator

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2016                                                                                             | Term                                          | <u>2017</u>                                                                                 | Term                                          | 2018                                                                                                | TERM                                          |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) | Z. Celik-Butler<br>S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | N. Bhat<br>D. Camacho Montejo<br>S. Deleonibus<br>M. leong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) |

|                                                                                                  |                                               | T.L. Ren                                                                                    | (2)                                           |                                                                                                     |                                               |

# NEWSLETTER EDITORIAL STAFF

### **Editor-In-Chief**

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

### REGIONS 1-6, 7 & 9

Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

# Central USA & Canada (Regions 4 & 7)

Karim S. Karim University of Waterloo E-mail: kkarim@uwaterloo.ca

# Southwestern & Western USA (Regions 5 & 6)

Adam M. Conway Lawrence Livermore Nat. Lab. E-mail: conway8@llnl.gov

### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

### **REGION 8**

### Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

### Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### UK, Middle East & Africa

Jonathan Terry

The University of Edinburgh E-mail: jonterry@ieee.org

### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

### REGION 10

# Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia

E-mail: susi@ukm.edu.my

### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

### **East Asia**

Mansun J. Chan Hong Kong Univ. of Sc. & Tech. E-mail: mchan@ust.hk

### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editorin-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

### Newsletter Deadlines

| <u>ISSUE</u> | Due Date    |

|--------------|-------------|

| January      | October 1st |

| April        | January 1st |

| July         | April 1st   |

| October      | July 1st    |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

**Copyright** © **2016 by IEEE:** Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

# Trends in Device Research - IEDM 2015 Highlights

(continued from page 1)

Variability Analysis of GaAs0.4Sb0.6/ In0.65Ga0.35As Heterojunction Tunnel FETs; R. Pandey et al, Pennsylvania State University.

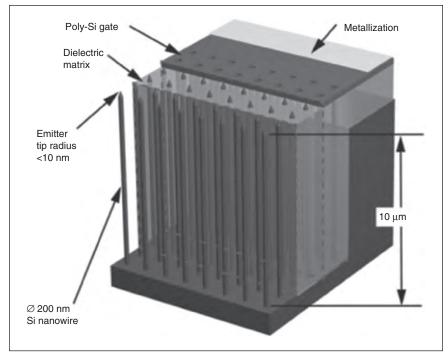

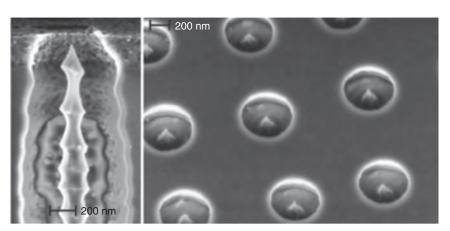

Vacuum tubes are making a comeback but in a very tiny way. Tiny electron guns (or nanoscale cold cathodes) were built from arrays of nanowire field emitters (tip diameters as low as 6 nm) that can be integrated on silicon. This means that good times are back since vacuum electronics were synonymous with high power and efficiency but now they are available without compromising the benefits of solid state (i.e. high gain and low noise). The research team from MIT demonstrated emitter arrays as large as 1000 × 1000 (Paper 33.1, High Performance and Reliable Silicon Field Emission Arrays Enabled by Silicon Nanowire Current Limiters; Stephen Guerrera et al, MIT).

The study demonstrated a current density of >100 A/cm<sup>2</sup>, more than a hundredfold greater than any other field-emission cathode operated in continuous wave mode. The devices also exhibited long lifetimes and low-voltage operation. So, new strides in technology can be taken into making miniature RF amplifiers

and smaller sources of terahertz, infrared and X-ray radiation.

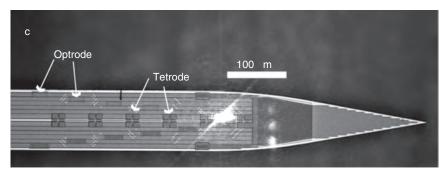

Mind-blowing technology also finally debuted at IEDM 2015. Optogeneticsis the study of neurons using visible light to stimulate their constituent proteins. The neural cells aren't damaged by optical stimulation, as they can be when electrically stimulated.

A team led by IMEC proposed an implantable neural probe with the highest reported density of optrodes (light emitters) and electrodes (to record the responses of the neurons

Schematic of the device structure (Ref: S Guerrera, et al., IEDM 2015 paper 33.1)

Transmission electron microscopic image of the cross-section of a fabricated heterojunction TFET with a HfO<sub>2</sub>-ZrO<sub>2</sub> bilayer gate dielectric.

(Ref: R. Pandey, et al., IEDM 2015, paper 14.2)

SEM cross-sectional image of silicon nanowire current limiter with gate oxide removed (left), and emitters with 1 um spacing and gate aperture of 350 nm. (Ref: S Guerrera, et al., IEDM 2015 paper 33.1)

Image of the high-density multi-optrode-electrode probe with a light output activated (Ref: L Hoffman, et al., IEDM 2015, paper 29.5)

once they are stimulated). (Paper 29.5, High Density Optrode-Electrode Neural Probe Using SixNy Photonics for In Vivo Optogenetics; Luis Hoffman et al, Imec/KU Leuven). Higher density leads to better spatial resolution and also enables smaller probes that are less likely to damage tissue. To build the probe, the researchers integrated two different CMOS processes (silicon nitride photonics and TiN electrodes). They packaged the circuitry, implanted it in a mouse brain (oh.. it is not yet in human) and successfully demonstrated that it could both drive and record neural activity.

Remember when cameras went from plain black and white images to color? Well, now imagine cameras that can capture color and near-infrared (NIR) light. Medical diagnostics in particular, need the ability to capture all of these wavelengths with one compact device, which would make it easier and less time-consuming to examine different parts of the body.

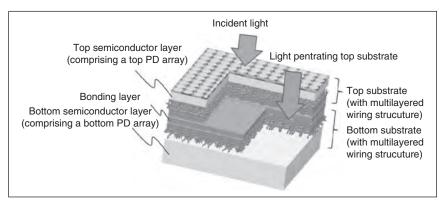

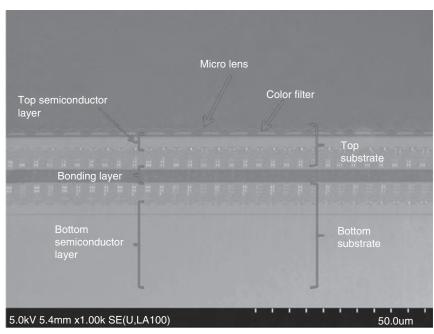

Clinicians would like these cameras to identify and pinpoint pathological lesions. The technical challenge is trying to detect color and NIR on the same chip because the optimizations are orthogonal. At IEDM 2015 in the Displays and Imaging track, researchers at Olympus demonstrated 3D wafer-stacking technology to integrate two separate CMOS imagers into one device, each optimized for either RGB or NIR through a balance of active silicon thickness and pixel size. (Paper 30.1, Multi-Storied Photodiode CMOS Image Sensor for Multiband Imaging with 3D Technology; Y. Takemoto et al, Olympus) The top imager is optimized for visible detection with an array of small pixels and a thinned 3  $\mu$ m active silicon layer. NIR signals pass through it to reach the bottom imager, which is optimized for NIR detection with an array of larger pixels and thick active silicon. The researchers claim there is no degradation in color

reproduction, sensitivity or resolution, features that are critical for end applications in the medical field. This should be a boon to physicians trying to make accurate and complete diagnoses.

3D circuits can be made either by stacking separate chips and connecting them through TSVs, or by stacking and bonding wafers where the individual die may be connected with TSVs or other interconnects, or by the use of monolithic 3D integration. In monolithic 3D, devices in adjacent layers are intimately and directly connected, thereby eliminating the need for TSVs which have relatively narrow I/O bandwidth. However, each layer in a 3D device must be annealed to remove stresses in its crystalline silicon structure, and to activate dopants which have been previously implanted. These annealing temperatures are often in excess of 1000C, which can lead to device damage. The current paper by Tsung-Ta Wu et al., NTHU, Taiwan overcomes this issue by using a CO2 far-infrared laser at 400C to selectively pulse-anneal source-drain regions of the silicon. (Paper 25.4, Low-Cost and TSV-free Monolithic 3D-IC with Heterogeneous Integration of Logic, Memory and Sensor Analogy Circuitry for Internet of Things; Tsung-Ta Wu et al, National Nano Device Laboratories/National Tsing Hua University). Using this technique, they built a sub-40 nm monolithic IC containing a variety of heterogeneous functions including logic, SRAM, RRAM, sense and logic amplifiers, and gas sensors. The researchers reported no device degradation using this localized annealing method, which they say makes the technique suitable for low-power, low-cost, small-footprint, and heterogeneously integrated devices.

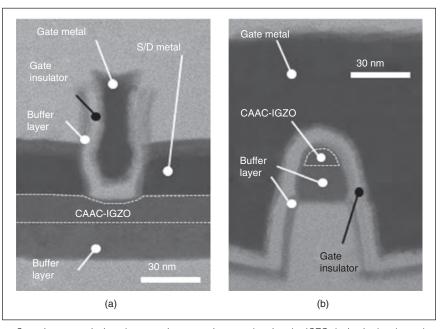

Internet of Things (IoT) applications require high frequency ultra-low power devices and circuits. 20 nm gate-all-around MOSFETs with incredibly low off-state currents of < 0.1 pA with cutoff frequencies exceeding 10 GHz

Schematic of Multi-storied photodiode CMOS imager (Ref: Y. Takemoto et al., IEDM 2015, Paper 30.1)

has been demonstrated by Daisuke Matsubayashi et al from Semiconductor Energy Laboratory Co. Japan. (Paper 6.5, 20-nm-node Trench-Gate-Self-Aligned Crystalline In-Ga-Zn-Oxide FET with High Frequency and Low Off-State Current; Daisuke Matsubayashi et al, Semiconductor Energy Laboratory Co., LTD). Indiumgallium-zinc-oxide (IGZO) thin film transistors built using a self-aligned process that eliminated overlaps from the gate to the source and drain, rendering the channel immune from short-channel effects that otherwise would degrade performance.

It is reported that the device integrated in a DRAM memory cell to demonstrate extremely low offcurrent, allowed for data retention of >10 days at 125°C.

Everyone wants a circuit they can bend to their will but although mechanically flexible circuits have the potential to enable revolutions in wearables and biomedical applications, the technology so far has not hit the mark. One reason is higher performance materials like single crystal silicon like to be processed at high temperatures, which is at odds with lower temperature flexible materials. A team led by France's Institutd'Electronique de Microélectronique et de Nanotechnologie proposed the ultimate thinning and transfer-bonding process in the Flexible Electronics session at IEDM 2015. (Paper 15.7, Application-Oriented Performance of RF CMOS Technologies on Flexible Substrates; Justine Philippe et al, IEMN/STMicroelectronics/CEA LETI Minatec). They demonstrated that even radio-frequency CMOS silicon circuits can be put onto substrates like polyimide plastic or stainless steel. They first thinned silicon SOI wafers to 30  $\mu$ m by completely removing the backside and transferred the SOI circuits to plastic using a laminating process. The researchers claim their technique can enable ultramechanical flexibility, better heat dissipation and even transparent circuits.

Performance benefits of III-V channels for low-power logic device ap-

Cross-section image (SEM) of the device (Ref: Y. Takemoto et al., IEDM 2015, Paper 30.1)

Scanning transmission electron microscope images showing the IGZO device in the channel length direction (a) and in the channel width direction (b). (Ref: D Matsubayashi, et al., IEDM 2015, paper 6.5)

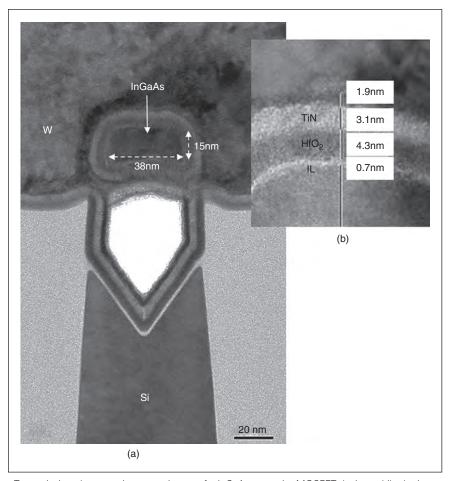

plications have been demonstrated by the complete integration of these channels in devices made on silicon wafers. In the paper by Waldron et al., from IMEC discussed gate-allaround, high-performance InGaAs nanowire MOSFETs built on 300 mm silicon wafers. (Paper 31.1, Gate-All-

Around InGaAs Nanowire FETS with Peak Transconductance of 2200 μS/μm at 50 nm Lg Using a Replacement Fin RMG Flow; N. Waldron et al, Imec/ ASM). High transconductance (g\_ = 2200) of the device indicates that despite having a lattice-mismatched substrate, the InGaAs channel

Transmission electron microscope image of a InGaAs nanowire MOSFET device, while the inset shows the gate stack.

(Ref: N Waldron, et al., IEDM 2015, paper 31.1)

material maintains its high carrier velocity.

3D NAND architectures with gateall-around (GAA) devices arranged in a vertical channel structure exhibits excellent device performance. However, these devices are highly sensitive to variations in their critical dimensions (CD), and it is difficult to maintain precise dimensional control of these structures at the required high aspect ratios. Macronix researchers described an alternate 3D NAND architecture that mitigates this issue by creating a 2D-like structure in the vertical direction. (Paper 3.2, A Novel Double-Density, Single-Gate Vertical Channel (SGVC) 3D NAND Flash That Is Tolerant to Deep Vertical Etching CD Variation and Possesses Robust Read-disturb Immunity, Hang-Ting Lue, Macronix).

The structure is a single-gate, flatcell thin film transistor (TFT) with an ultra-thin body named single-gate vertical channel (SGVC). The design is not as sensitive to CD variation and is reported to have more than four times the memory density of GAA vertical channels at the same scaling node.

Future flash memories may be stackable devices with polysilicon channels running vertically through them. However, grain boundary defects in polysilicon's crystal structure could decrease electrical conductivity by scattering and trapping electrons. A clear understanding of the actual conduction paths in these channels would enable more accurate predictions of how the devices will operate. In the IMEC paper by Robin Degraeve, et al., a new atomistic 3D model of grain boundaries taking into account the specific regions of enhanced scattering in the polysilicon and specific charge defects which can cause local barriers and depletion areas is presented. (Paper 5.6, Statistical Poly-Si grain boundary model with discrete charging defects and its 2D and 3D implementation for vertical 3D NAND channels; Robin Degraeve et al, Imec). This model gives statistical insight into the properties of scaled poly-Si channel devices (particularly vertical NAND devices), and their yield and reliability limitations.

(This article is prepared by the Editorial team of EDS Newsletter – Karim S. Karim, Mukta G. Farooq and M. K. Radhakrishnan. The data used for the article has been provided by the IEDM Technical Chair)

# UPCOMING TECHNICAL MEETINGS

# 43rd IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE PREVIEW

It is my distinct pleasure to invite you to be a part of the 43rd IEEE Photovoltaic Specialists Conference, June 5-10, 2016, which I am proud to host at the Oregon Convention Center in Portland, Oregon. This year's conference promises to uphold PVSC's tradition as a premier international conference on the science and technology of photovoltaics by providing an interactive forum for researchers, students, scientists, engineers, technology and business leaders from industry, academia, government in an environment conducive to strengthening collaborations and sharing knowledge across the field of photovoltaics. This year we are joining forces with the American Solar Energy Society to provide an even more varied and diverse meeting with a strong focus on systems and applications in addition to our traditional areas.

From PV discovery to deployment, our vision is to share state-of-the-art research results to hasten the widespread availability of solar electricity. The PVSC technical program covers the full spectrum of basic photovoltaic science, novel PV materials, device and module architectures, device and system performances, novel characterization techniques, component and system deployment and reliabil-

ity. The 43rd PVSC will host keynote addresses, plenary talks, oral-presentation sessions and poster sessions in all technical areas, which are designed to provide each PV specialist ample opportunity to delve deeper into select topics or to expand their horizons into new PV-related areas. To complement our technical program, PVSC-43 also expects to offer full day short courses and half day tutorials covering a wide range of topics by leading experts, and will host a dynamic Exhibition for companies and research labs to showcase their latest products and innovations ranging from characterization to manufacturing.

Portland is a beautiful city and a home for outstanding science and technology. It is easily accessible from Europe and East Asia by air with direct flights to Tokyo, Ontario, Keflavik Iceland, Frankfurt, and Amsterdam, among others. Portland is the home to many notable local organizations such as the Oregon Museum of Science and Industry (OMSI), and is the home of Intel's research center, Solar World, Solo-Power, and many others. Portland is also known for excellent food with a wide variety of outstanding restaurants and food trucks, and gardens. We expect the rose garden to be at the peak of its beauty in June when the conference is there. The region is well known for outdoor activities including hiking, birding, wind surfing, cycling, and many others.

Please join us in continuing the PVSC's tradition as the preeminent conference dedicated to the science and technology of photovoltaics! On behalf of all of the volunteers who comprise the PVSC Organizing, Cherry, and International Committees, I look forward to personally welcoming you in Portland for the 43rd IEEE PVSC!

Angus Rockett 2016 PVSC General Conference Chair

# 2016 IEEE INTERNATIONAL VACUUM ELECTRONICS CONFERENCE (IVEC)

We are pleased to announce that the Seventeenth International Vacuum Electronics Conference (IVEC2016) will be held in Monterey, California, USA, on April 19-21, 2016. The meeting will be held at the Marriott Conference Center only steps away from Fisherman's Wharf in downtown Monterey. Visitors from around the world come to Monterey to experience its natural coastal beauty, visit the renowned Monterey Bay Aquarium, and experience its rich historic past memorialized in the novels of John Steinbeck.

Sunset over California Coast, Photo Credit: istock.com

With sponsorship from the IEEE Electron Devices Society (EDS), the conference will provide a forum for scientists and engineers from around the globe to present the latest developments in vacuum electronics at frequencies ranging from UHF to Terahertz frequency bands, as well as their applications.

IVEC was originally created in 2000 by merging the US Power Tube Conference and the European Space Agency TWTA Workshop. Now a fully international conference, IVEC is held every other year in the US, and in Europe and Asia alternately every fourth year. After a successful and enjoyable IVEC2015 in Beijing, China, IVEC will return to Monterey in 2016. You can learn more about IVEC by visiting VacuumElectronics.org, the EDS Vacuum Electronics Technical Committee website.

IVEC2016 will last three days with one plenary session on the first half day, followed by approximately 25 technical oral and poster sessions planned for the remaining two and a half days. The plenary talks will provide insights into the history, the broad spectrum of fundamental physics, the scientific issues, and the technological applications driving the current directions in vacuum electronics research. Technical presentations will range from the fundamental physics of electron emission and modulated electron beams to the design and operation of devices at UHF to THz frequencies, theory and computational tool development, active and passive components, systems, and supporting technologies.

System developers will find that IVEC provides a unique snapshot of the current state-of-the-art in vacuum electron devices. These devices continue to provide unmatched power and performance for advanced electromagnetic systems, particularly in the challenging frequency regimes of millimeter-wave and THz electronics.

The John R. Pierce Award for Excellence in Vacuum Electronics and a Student Paper Award will also be presented at the conference. As in past conferences, the meeting and social events will provide unique opportunities to renew or establish new friendships with colleagues, interact with customers and end-users, and meet students and academic researchers.

The conference website is the best source of information about IVEC2016 including Technical Subject Categories, Paper Submission, Registration, Accommodations, and other important dates and events. Please visit http://ivec2016.org for more details and the latest news about the conference. To inquire about exhibitor space or conference support, please contact A. Waldron at awaldron@pcm411.com. We look forward to seeing you in Monterey.

David R. Whaley 2016 IVEC General Chair L-3 Communications San Carlos, CA, USA

# 2016 IEEE INTERNATIONAL MEMORY WORKSHOP (IMW)

THE 8th IEEE International Memory Workshop will be Held at the Paris Marriott Rive Gauche Hotel,

Paris, France, May 15—18

In response to the growing global interest in memory technologies, the NVSMW – Non Volatile Semiconductor Memory Workshop – and ICMTD – International Conference on Memory Technology and Design – were merged together in 2008 to incor-

porate the volatile and non-volatile memory aspects in one forum while maintaining the workshop experience. The workshop is sponsored by the IEEE Electron Devices Society and meets annually in May. In 2016, IMW will take place in Paris, France.

The convergence of consumer, computer and communication electronic systems is leading to an exponential growth in need, mainly for code, computing and data storage. While in the past we could associate a memory technology to a specific

market segment (e.g., RAM to computer, NOR Flash to mobile communication, NAND Flash to consumer SSD), today the new electronic systems stack different memory technologies and use microcontroller to facilitate interfacing and managing the overall memory. Moreover, novel memory technologies are entering in the market, providing opportunities for novel applications and challenges for the technology development. The characteristics of these complex memory systems in terms of density, performance, power consumption, packaging and interfacing become of greater interest. The capabilities provided by the new memory technologies, new concepts and material proposed today will drive the definition of these memory systems in the future. The IMW aims to answer this need, extending the scope from non-volatile memory, which had been successfully discussed in more than 30 years of NVSMW's history, to large memory technologies and design, which were the focus of ICMTD, in the view of systems. Innovation is our tradition: IMW widened its focus while maintaining the positive characteristics of a workshop.

IMW is a unique forum for both specialists in all aspects of microelectronic memory and novices wanting to gain a broader understanding of the field. The workshop is usually attended by a wide international community from North America, Europe, Japan and Asian countries. Attendees include industry leaders, researchers in academia and industry as well as end users of memory products. The number of attendees typically exceeds 250 in recent years, reflecting the growing interest in the workshop. Each year we receive over 80 paper submissions and accept about 35 for oral presentation which corresponds to about 40% acceptance rate. Principal topics for discussion are: device physics, silicon processing, product testing, new technologies including new structures and novel approaches, programmable logic, memory cell design, integrated circuits, solid state disks and memory cards, reliability and new applications. Following the tradition established in previous IMW editions, Sunday, May 15th will be dedicated to a Short Course session. Moreover a poster session for qualified papers is usually held after the panel discussion.

An important goal of IMW is to provide an informal environment to encourage discussions and interactions among participants. There will be morning and afternoon technical sessions, along with a lively evening panel discussion on a hot topic in memory field. Technical interaction among presenters and attendees is encouraged through question and answer sessions and allotting ample time after formal paper presentations for further in-depth discussions. Organized breaks, including snacks and the conference dinner and lunch are provided as opportunities to meet and exchange ideas with colleagues. The morning and afternoon technical sessions are organized in a manner of providing time for the informal exchange and to enjoy the beauty of Paris area. The hotel is conveniently situated in Paris downtown, close to public transportations (subway, train) and it is easily accessible from the international airport (30-45 min). For more information about the conference, please go and register at the website www.ewh.ieee.org/soc/eds/imw.

Looking forward to seeing you next May at IMW 2016 in Paris.

Jing Li 2016 IMW General Chair University of Wisconsin-Madison

# 2016 IEEE INTERNATIONAL RELIABILITY PHYSICS SYMPOSIUM (IRPS)

The IEEE International Reliability Physics Symposium (IRPS) is the world's premier forum for leadingedge research addressing developments in the Reliability Physics of devices, materials, circuits, and products. IRPS is the conference where emerging Reliability Physics challenges and possible solutions to achieve realistic End-of-Life projections are first discussed. This year, the IRPS will be held at the Hilton Pasadena in Pasadena, California, USA, April 19-21, 2016. The IRPS will commence with

PASADENA CONVENTION & VISITORS BUREAU, JAMIE

two full days of tutorials and yearin-review on Sunday, April 17th and Monday, April 18th.

The IRPS draws presentations and attendees from industry, academia and governmental agencies worldwide. No other meeting presents as much leading work in so many different areas of reliability of electronic devices, encompassing silicon device, non-silicon device, process technology, nanotechnology, optoelectronics, photovoltaic, MEMS technology, circuits and systems reliability including packaging.

For the IRPS 2016, we are emphasizing **Self-heating effects** on transistors and circuit aging. We are also emphasizing **Systems reliability** comprehending complex applications including Chip-Package interactions and packaging. Finally, we are strongly promoting all reliability works on **Photovoltaics**.

For 54 years, IRPS has been the premiere conference for engineers and scientists to present new and original work in the area of microelectronics reliability. Drawing participants from the United States, Europe, Asia, and all other parts of the world, IRPS seeks to understand the reliability of semiconductor devices, integrated circuits, and microelectronic assemblies through an improved understanding of both the physics of failure as well as the application environment, IRPS 2016 will offer a full slate of tutorials, evening panel debates and workshops, invited plenary talks in addition to an outstanding technical program.

The hotel is located in Pasadena's downtown which is best known as the host of the annual Tournament of

Roses Parade and Rose Bowl football game. The City also boasts numerous cultural amenities, fine restaurants and top retailers. All this helps Pasadena live up to the true meaning of its name—the Crown of the Valley.

IRPS consists of three days (Tues–Thurs, April 19–21) of plenary and parallel technical sessions presenting original, state-of-the-art work.

Other opportunities at the symposium include:

- Two-Day Tutorial Program (Sunday–Monday April 17–18). The IRPS tutorial program is a comprehensive two-day event designed to help both the new engineer and experienced researcher. The tutorial program contains both beginner and expert tracks, and is broken down into topic areas that allow the attendee to participate in tutorials relevant to their work with a minimum of conflicts between subject areas.

- Year in Review Session (Monday April 18). These seminars provide a summary of the most significant developments in the reliability community over the past year. This serves as a convenient, single source of information for attendees to keep current with the recent reliability literature. Industry experts serve as the "tour guide" and save you time by collecting and summarizing this information to bring you up to date in a particular area as efficiently as possible.

- Evening Poster Session. The poster session will provide an additional opportunity for authors to present their original research.

- The setting is informal and allows for easy discussion between authors and other attendees.

- P Evening Session Workshops.

These workshops enhance the symposium by providing the attendees an opportunity to meet in informal groups to discuss key reliability physics topics with the guidance of experienced moderators. Some of the workshop topics are directly coupled to the technical program to provide a venue for more discussion on the topic.

- Vendor Exhibits. Held in parallel with the technical sessions, the equipment demonstrations provide a forum for manufacturers of state-of-the-art laboratory equipment to present their products. Attendees are encouraged to visit the manufacturers' booths for information and demonstrations.

- IRPS Paper Awards. IRPS bestows awards for Best Paper, Outstanding Paper, Best Poster and Best Student Talk. The Best Paper author is typically invited to present the paper at ESREF in October.

For registration and other information, visit the IRPS 2016 home page at http://www.irps.org/. The IRPS committee members look forward to seeing you in April.

Vincent Huard 2016 IRPS Publicity Chair STMicroelectronics

Chris Henderson 2016 IRPS General Chair Semitracks, Inc.

# SOCIETY NEWS

## EDS BOARD OF GOVERNORS MEETING HIGHLIGHTS

In keeping with our long-standing tradition, the EDS Board of Governors once again convened in advance of our flagship conference IEDM to hold the year-end EDS governance meeting series.

The meeting series and the IEDM were held at the Hilton Washington, DC. The Washington Hilton has been the IEDM's East Coast home for many decades but this year marks the final East Coast IEDM for the foreseeable future. After this year, we will host this event in San Francisco each year, as opposed to alternating with Washington, DC.

Beginning on Saturday morning, the weekend kicked-off with spirted committee meetings for each of the society's crucial functional areas: newsletter, publications, conferences and technical activities, education, and regions and chapters. Led by the VPs and chairs of our standing committees, the groups, comprised of not just committee members, but also interested EDS members, reviewed the year's operations and finalized plans for 2016.

Highlights from the committee meetings include:

- Newsletter. The committee stressed the need for growth in participation from chapters in Regions 1-8 and to find ways to better engage and recognize new members in the newsletter. Congratulations to Newsletter Editor-in-Chief MK Radhakrishnan, for his outstanding service to the Society.

- Publications. A pillar of EDS since its inception, EDS's publications continue to thrive. The committee met to address issues relating to Open Access, conference publishing, and ways to maintain the integrity of our publications, while improving the diversity of authors

EDS Officers for 2016-2017 (left to right): Subramanian lyer, Treasurer; Samar Saha, President; Simon Deleonibus, Secretary; and Fernando Guarin, President Elect

and readers as well as our speed to publication.

- Joint Membership, Education, and Chapters. A large group of volunteers gathered for spirited debate about how we can better attract and retain students and young professionals, as well as continuing to be relevant with established member base.

- Conferences and Technical Activities. Another critical area for the Society, this Conferences and Technical Activities committee met to review the 2015 conferences, discuss plans for extending our partnership with SEMICON West, and strategize how to establish a

bigger conference presence in Region 10.

Saturday culminated with the working dinner meeting of the EDS Executive Committee (ExCom) to provide a venue for the society's senior volunteer leadership to discuss and refine the strategic vision of the society.

The main EDS Governance meeting took place on Sunday, starting early in the morning and running through the late afternoon. The day was marked by impassioned dialogue and debate about the future of EDS both from a technical and operational perspective. New markets need to be explored, new challenges need to be bested, and EDS is taking bold steps to ensure its continued relevance and success in the future. And to lead the Society into that bright, promising future, we are pleased to announce the results of the 2016 Officer and Member-at-Large election.

As you may recall, last year we began a pilot program to have 1 Memberat-Large (MaL) selected by the general membership of the Society. This year several thousand EDS members took part in the general election, voting for **Doug Verret**.

The remaining six MaL seats were selected by the sitting Board of Governors. The winners in that election were Navakanta Bhat, Daniel Camacho, Simon Deleonibus, Meikei leong, Murty Polavarapu, and RaviTodi.

The EDS officer elections were also held. The incoming Secretary of the Society is **Simon Deleonibus**. The incoming Treasurer is **Subu lyer**. And last, but certainly not least, the 2016–2017 President Elect is **Fernando Guarin**. Information and biographies

of the newly elected officers will appear in the next issue of the EDS Newsletter (April 2016).

Our thanks to all those who took part in the election. We are very fortunate to be blessed with so many talented, dedicated volunteers. In closing, let us congratulate our election winners and wish them great success in their new elected positions.

> Christopher Jannuzzi EDS Executive Director

# Message from Outgoing President of EDS

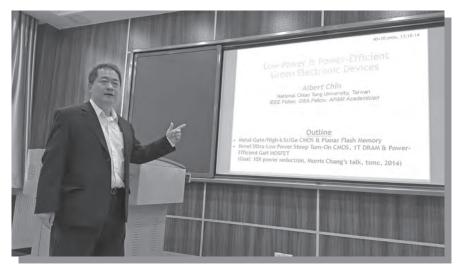

Albert Wang EDS President 2014–2015

Dear Fellow EDS Members.

The Message that you are reading is the fourth and last President's Message for my two-year term as EDS President. Writing the message in a

high-speed train leaving Beijing at a speed of 350 km/hour and watching the flashing scenes through the window, I am quickly recapping what have happened within the EDS community in the past two years. Instead of giving a usual summary of the "achievements" during my term, I would rather talk a little about the challenges that EDS is facing in this Message.

The main challenge is about operations and finance transparency at both IEEE and EDS levels. As I reported before, EDS is one of the five societies initiated the big effort of pushing for IEEE finance transparency and plays a leading role on the ad hoc Fin-Trans committee in the past two years. We presented the EDS financial data several times at the TAB meetings to argue for finance transparency at IEEE level. With the

joint efforts, progresses were made and IEEE finance team is opening its finance nutshell, though slowly and with limited contents, to societies for analysis. Are there anything interesting revealed? You bet! For example, the data revealed that a society paid IEEE about \$4200 per article in 2015 for published paper and the tax paid to IEEE for its Corporate IT costs increased 25% from 2014 to 2015. What a surprise, or not?! It at least speaks out loudly that it makes sense to keep IEEE finance transparency to the volunteers. Being on the EDS leadership team for many years, I know that local chapters have had difficult times in asking for a few hundred dollars to support some well-planned member activities. Good finance transparency helps volunteer leadership to manage society budget and serve the volunteers better. Keep in mind that volunteers work for FREE and IEEE is a not-for-profit organization.

Of course, operations transparency at EDS level is also needed. During my term, we identified one key area to improve for EDS operations transparency, which is to establish a clear written journal editor-in-chief (EiC) selection procedures that did not exist. Thanks to the great efforts of the Publications and Products

Committee (PPC), led by the VP Pubs, as well as contributions from many other volunteers, we are making solid progresses in reforming the way that we selected EiCs for our journals. In the first phase, a transparent temporary EiC selection procedure was used to select the new EiCs for TED and EDL. Both new EiCs are in place to run the Transactions on Electron Devices and the Electron Device Letters. Currently, the PPC is working to finalize the formal EiC Selection Procedures documentation, which shall be completed soon. I consider this being a major achievement in my term that resolved a decadeslong problem in EDS operations. In terms of EDS operations, I fully believe that the best way to ensure smooth and transparent operations is to establish a solid "infrastructure" guided by clear-written documentation, hence, everyone can follow the written policies in conducting EDS business. This shall ensure smooth operations of EDS without suffering possible single-event disruption and any individual influences. We have made progresses in this regard. For example, the Charters were drafted for all standing committees. We shall continue this effort in order to ensure long-term health of EDS.

Another truly major challenge is the membership development, which has been a big problem to IEEE as a whole too. While EDS has worked very hard to maintain our around-10000 member pool, what will be the way to grow our community? Unlike the transparency problem that we know how to resolve, there are no "good" solutions to the membership development challenge, at least, not to me. I am calling for any ideas and suggestions from our members. I believe that the key to membership development, or put it in a different word, the survival of EDS and IEEE, depends completely on if our members and potential members will be happy with the society. We ought to keep in mind that IEEE and EDS are volunteerdriven organizations for volunteers only. Should this key point being ignored, there would be no way to survive, not even thinking of growth and prosperity. For this reason, keep IEEE and EDS operations and finance transparency is of vital importance.

Being forward-looking and adaptive is yet another challenge to EDS future. We are living in a fast-changing era where everything moving extremely fast, technically and socially. The traditional mind-sets will not work anymore. We already saw many used-to-be-untouchable giant companies collapsed in seconds in recent years. IEEE and EDS cannot be any exemption. For example, should we adapt the open access (OA) publication model? Maybe nobody knows for sure for now yet, however, we shall not miss the train. Indeed, our JEDS journal is facing tremendous challenge now. However, JEDS may eventually help EDS to survive the OA future. We ought to be brave in doing new experiments in order to ensure our future. Similarly, many traditionally strong conferences, mainly in North America, are facing problems now due to many emerging challenges. For example, the decades-long party of CMOS scaling down is fast approaching its end, non-traditional and non-electronic devices are emerging, internet-of-things technologies are quickly shaping up, semiconductor industry is shifting to Region 10, etc. We have to admit that EDS made some mistakes before that resulted in losing the due ownership of several emerging device domains to others, such as, MEMS, sensors, nano technologies, to name a few. By nature, those are all devices that certainly belong to EDS. Unfortunately, EDS is only playing a side role in many of these emerging device areas now. We cannot afford making any similar mistakes anymore. We have to be more open-minded and absolutely adaptive in order to survive, grow and prosper in this fast-changing era.

Dear colleagues, I really enjoyed being with all of you for years, not just during my Presidency. I certainly appreciate all of your efforts in making EDS being today. I also want to thank my ExCom team (Renuka Jindal, Paul Yu, Samar Saha, Bin Zhao, Leda Lunadi, Mikael Ostling, Xing Zhou, Ravi Todi and Fernando Guarin) for working with me in the past two years to run the society. My special thanks go to our staff team in the Executive Office who worked hard to maintain EDS operations. While I outline some challenges above, I fully believe that challenge also means opportunity. With 10000 members around the globe, the future of EDS shall be bright! Please keep in mind that EDS is a volunteer society and it exists for only one reason: for volunteers!

> Sincerely, Albert Wang EDS President on his way out

# Message from Incoming President of EDS

Samar Saha EDS President 2016-2017

Dear Fellow Electron Devices Society Members:

I am extremely honored and pleased to assume the duties as President of IEEE Electron Devices Society (EDS). EDS has always led by ex-

traordinary visionary leaders in the past. I take this opportunity to thank the past leadership for making EDS one of the best societies of IEEE. I will continue building EDS on the foundation of the past to meet the challenges of the future.

EDS is, truly, an international society with more than 10,000 members and 190 chapters worldwide. Over the past six decades, EDS has been promoting the advancement of the professional standing of its members and has been enhancing the quality of life for humanity through its members' contributions in R & D, manufacturing, and application of electronic and ionic devices. Our Society is an all-volunteer society, driven to excellence by its leadership, with the active participation of all our worldwide members. EDS has always been, clearly, one of the premier societies of IEEE and is by far the best of all professional associations operating in the global device technology arena. So, we are in a very good position. However, as device technology is approaching to a challenging regime, we cannot sit back and relax on our past.

In the years ahead, business will not be as usual. Now, things can change much faster than ever due to Internet. There are ongoing trends in publication business, organization of conferences and exhibitions, content distributions, knowledge access, education, membership models of technical societies, strategic or temporal partnering with other societies or groups, field of standards, and in the knowledge management that may or will affect EDS's operations. In my view, the current areas of focus of our society: (1) membership; (2) publications; (3) conference management; (4) chapters; (5) educational activities; (6) sponsored awards; (7) EDS Mission Fund, and so on are well defined. And, we are in good standing with our definition of *near-future* directions and engagements. However, we must develop strategy for outreach program to benefit our Society and define our future directions for smart electronic systems such as devices for smart-cars including selfdriving or driver-less cars, smart-city infrastructure, Internet of Things, and so on. Therefore, my plan is to continue with our current activities and execution processes, and develop a suitable outreach program and define the future directions of our Society. I will discuss some of these programs below and some in due course of time of our engagement.

- Membership Growth: Our Society membership continues to be around 10,000 for a while. In spite of maintaining this overall number, the membership in some geographical regions continues to decline. I intend to develop strategies for membership drive through our Subcommittee for Regions & Chapters volunteers.

- Publications Excellence: It is

of paramount importance that

we consistently work not only

to keep but also to expand our

worldwide leading position with

- respect to publications by always operating at the forefront and by keeping the quality of published papers as high as possible. In this respect, I plan to develop EDS Open Access (OA) strategies to make our newly launched the *Journal of Electron Devices Society* (J-EDS) one of the top-tiered topical OA publications in IEEE and competing OA publications on device technology through our Publications and Products volunteers.

- Conference Management: Similar to our publications, it is extremely important to expand our worldwide leading position with respect to device conferences. In this context, I intend to drive the Asia Electron Devices Meeting and set a realistic schedule for the inaugural conference in Asia. Conference income is the major component of the Society's income. I intend to develop management policies and procedures that will assure the integrity of the income stream and the continued success of our conferences.

- Chapter Growth: Chapters are vital to the overall success of EDS and growth of our Society's membership. We must provide the necessary assistance to our chapters to actively engage in EDS programs. Also, it is extremely critical to plan the growth and development of EDS Student Chapter. Today's academic institutions hold the engineering professionals of tomorrow. I intend to continue to be heavily focused on developing programs to benefit today's students and help them prepare for entry into the industry or academia with an objective to strategically add Student Chapters from many of the academic institutions worldwide.

- Educational Program: Our Society has earned praise from 2015

Five-year Society Review Committee for our stellar educational programs including Masters Student

- and PhD Student Fellowships, Distinguished Lectures (DLs), Mini-Colloquia (MQ), Webinar, and so on. Our thanks go out to all involved, distinguished lecturer and volunteers, in making these programs a high-value benefit for our members. Our topical areas for DLs, MQ, and Webinars provide opportunities to our members for networking and learning from fellow members and recognized experts in the field. In addition to continuing the existing programs, I intend to explore the feasibility of introducing a *Tutorial* Program with leading experts in the field as Tutors.

- Outreach Program: I plan to actively pursue EDS Outreach Program. Being involved in industry as well as in academia, I am aware of most students' thought processes and their views on engineering and technology. Also, being associated with volunteers around the globe, I know that the attitudes of people from different geographical regions are different. So, I plan to engage outreach programs: Outreach to Youth, Outreach to Industry, and Outreach to other Societies. We need to evaluate which strategic or temporal alliances or kind of partnerships will help us to better reach our goals. The EDS Field of Interest Statement overlaps with the societies that spawned out of EDS. I think by working with the Overlapping Societies we can form a mutually profitable relationship that will increase the membership of EDS and partner Societies while increasing the service and benefits to the members of all the Societies involved

- Future Directions: In my view, EDS must get involve in Future Direction programs. The impact of electronic devices from the component level to system level is more than ever. This is, especially, true for emerging application areas such as automotive industry,

industrial automation, life sciences, security, logistics, mobility, energy saving, social networking, and environmental protection where high growth rates are evident. In all these areas, electron devices are crucial to the competitiveness of companies and entire industry sectors, as these technologies provide pertinent key enabling functionalities and are thus, a driving force behind numerous product innovation activities. In particular, device technologies play a key role in nearly all areas of computers, communications, and social media. Further, the semiconductor industry will continue to evolve in providing smart-electronic devices enabling solutions for smart-cars, smart-homes, smart-city infrastructure, Internet of Things, and so on. The smart city infrastructure for driverless cars requires smart electronic system along with software codes to communicate cars and urban traffic system for the safety of drivers and pedestrians and maintaining echo systems. The emerging trends will greatly influence the future of our technical field of interest and therefore, to the broad spectrum and the territory of our Society. This offers EDS opportunity to outreach automobile industry to define device specifications and set standards for smart electronic devices and products and outreach city governance to set strategies for smart-city infrastructure. Thus, I intend to engage in

Future Direction programs through our Technical Committees and volunteers to organize conferences, Webinar, MQ, and DLs, publish Special Issues, and so on.

These are all very worthy goals; so, I urge all EDS members to publicize the benefits our Society offers and help achieving our goals. The most important step to achieve our goals is to empower our Executive Committee (ExCom), Board of Governors (BoGs), Technical Committees, and the Membership to involve in the activities of the Society. As mentioned, EDS is an allvolunteer society and thus, the selfless dedication of our volunteers is of utmost importance for the well-being of our Society. Our volunteers organize our conferences, workshops, DLs, MQ, Tutorials, and Education programs; they lead our publications and review submitted papers; and they serve on our Local Chapters, Technical Committees, BoGs, and ExCom. So, I encourage all our members to get involved at any level - attending events, volunteering to help with specific activities or joining one of our 14 Technical Committees. Personally, I have been involved with EDS for over 25 years. The knowledge I gained and the life-long friends I met along the way have made EDS membership a tremendous experience for me, both personally and professionally. It has always been a pleasure for me to work with my volunteering colleagues towards the well-being

of the global electron devices community. So again, get involved and bring along anyone else you know, new to the field, or experienced technologist or researcher, and see what EDS can do for you - you will be glad you did! Together we can continue to make EDS a great Society for all our members. And, I am humbled for the opportunity to lead the way.

Finally, I congratulate the newly elected members of BoGs and Officers and, newly appointed ExCom members and Technical Committee Chairs and Members. The Excellence of our Society has been achieved through the hard work and dedication of our previous Officers, ExCom, BoGs, Technical committees, and our Chapter volunteers. So, my sincere thanks to all those involved. I look forward to working with our new BoGs, ExCom, and Technical Committees to further the great work done to make EDS one of the premiere societies in IEEE. Without the hard work and dedication of these individuals, our membership would not be able to enjoy and benefit from all the activities and resources our Society has to offer. Our Society is here to serve you. If you have ideas for improving EDS, I would love to hear from you. Please do not hesitate to contact me.

> Samar Saha EDS President Prospicient Devices Milpitas, CA, USA

# Message from Editor-IN-Chief

M K Radhakrishnan Editor-in Chief

Dear Readers and EDS members.

Wish you all a Happy New Year 2016.

This issue of the Newsletter has few significant features and the major one is the recap of the IEDM 2015 held from December 7-10, 2015 in Washington, DC. This is the first time EDS Newsletter is giving a technical summary of some of the key presentations at IEDM. With this article as the major technical one in the Technical Briefs section, we are intending to provide an abridged version of some of the key papers depicting the trends in device technology and its applications. IEDM being the major technical event of IEEE and Electron Devices Society and the Newsletter is the medium for the society to communicate with its members at large, the Editorial team considers such an article is the best platform for our readers to know about the trends and happenings in the field. However, due to various limitations we could capture the gist of some of the key papers from few sessions only.

A summary of the deliberations in the Society's Board of Governors meeting held on December 6, 2015 is given in this issue. Also, the yearly BoG election results are reflected and a write up about the newly elected BoG members will appear in April issue.

In the Chapter News section, we have the Chapter of the year award winners being listed. Also, these winners are asked to provide their mode of operation as a successful chapter. The winner from R10 is featured here and rest will be appearing in April.

A recent survey about the Chapter's visibility in Newsletter shows not much variation in the Chapter's reporting for many years. Among the present 190 EDS Chapters spread over all the Regions, only less than 40 percent of the Chapters are found sending articles and reports to Newsletter, even after repeated requests from Regional Editors. As the Editorial team, we would like to hear the reasons for this inactive approach by our Chapters and if we need to do anything specific, please communicate.

However, as EiC, I would like to congratulate two chapters – ED Kansai Chapter and ED Japan Chapter – for regular reporting of activities in every issue of Newsletter for the last 5 years. Kudos to both Kansai and Japan Chapters.

Again, it is our readers' comments, criticisms and suggestions that make this Newsletter strong, and I request all the readers to write their feedback to edsnewsletter@ieee.org OR to me radhakrishnan@ieee.org

MK Radhakrishnan Editor-in Chief, EDS Newsletter e-mail : radhakrishnan@ieee.org

## **EDS CELEBRATED MEMBERS**

The EDS Celebrated Member was established in 2010 by the IEEE Electron Devices Society. It is intended to recognize and honor legendary individuals in the field of electron devices.

"For fundamental contributions to the field of electron devices for the benefit of humanity"

Dr. Jayant Baliga Celebrated Member

Dr. Jayant Baliga is an internationally renowned scientist, author of 19 books and over 550 publications, with 120 U.S. patents to his name. Among his inventions, the Insulated Gate Bipolar

Transistor (IGBT) is extensively used around the globe for compact fluorescent lamps, air-conditioning, home appliance controls, robotics, electriccars/bullet-trains, and compact defibrillators projected by the AMA to save 100,000 lives a year. The energy efficiency improvements derived from IGBTs have saved world-wide consumers more than \$ 24 Trillion

while reducing carbon dioxide emissions by over 100 Trillion pounds during the last 25 years. Dr. Baliga led the development of the IGBT at GE from 1980–1985 resulting in its widespread applications within the company. GE announced the first commercially available IGBT product in July 1983 based up on his design.

In the early 1970s, Dr. Baliga pioneered the growth of semiconductor films by Metal-Organic-Chemical-Vapor-Deposition (MOCVD) with Professor Ghandhi at Rensselaer Polytechnic Institute. In 1979, he developed a theoretical analysis resulting in the Baliga's Figure of Merit (BFOM) which relates the resistance within power rectifiers and FETs to the basic semiconductor properties. He predicted that the performance of Schottky power rectifiers and power MOSFETs could be enhanced by several orders of magnitude by replacing silicon with gallium arsenide and silicon carbide. Under his direction, the first GaAs power devices were demonstrated at GE in the 1980s followed by the first high performance SiC high voltage rectifiers and MOSFETs at NCSU in the 1990s. Wide band gap semiconductors are now the basis for a new generation of power devices in the 21st Century.

Dr. Baliga is also a serial entrepreneur having founded four successful companies in North Carolina with venture capital financing. His inventions, commercialized by these companies, include: the TMBS rectifiers used in solar cell panels and power supplies; the RF super-linear power MOSFETs used in cellular base-station power amplifiers; the SSCFET/JBSFET chip set for voltage regulator modules used to power microprocessors and graphics chips in personal computers, laptops, and servers; and the GD-MOSFETs used in power supplies for data-centers and in automotive electronics.

President Obama presented the National Medal of Technology and Innovation, the highest honor conferred by the United States to an Engineer, to Dr. Baliga in 2011. He received the North Carolina Award for Science, the highest honor given by the state to a civilian, from Governor Purdue in 2012. In 2015, he received

the Global Energy Prize in Saint Petersburg, Russian Federation for the invention, development, and commercialization of the IGBT. He will be inducted into the National Inventors Hall of Fame in 2016 for invention of the IGBT.

Prof. Baliga is a Life Fellow. His IEEE awards include: the 1991 Newell Award, the highest recognition from the Power Electronics Society; the 1993 Morris E. Liebman Award for his contributions to emerging Smart Power Technology; the 1998 J.J. Ebers Award, the highest recognition from the Electron Devices Society; the 1999 Lamme Medal from the Board of Governors: and the highest IEEE award, the IEEE Medal of Honor in 2014.

"For fundamental contributions to the field of electron devices for the benefit of humanity"

Dr. Robert H. Dennard Celebrated Member

Dr. Robert H. Dennard has been an industry leader in the development of microelectronics in a career that has spanned 57 years. He is responsible for two major milestones in the

progress of the industry, the invention of DRAM (Dynamic Random Access Memory) and the development of scaling principles for miniaturization of MOS (Metal Oxide Semiconductor) transistors and their associated integrated circuits.

Dr. Robert Dennard received the B.S. and M.S. degrees in electrical engineering from Southern Methodist University, Dallas, TX, in 1954 and 1956 respectively, and the Ph.D. degree from Carnegie Institute of Technology (now Carnegie Mellon University), Pittsburgh, PA in 1958. He then joined IBM Research Division where his early experience included the study of new digital devices and circuits for logic and memory applications, and the development of advanced data communication techniques. Since 1963 he has been at the IBM Thomas J. Watson Research Center, Yorktown Heights, NY, where he has been involved in microelectronics research and development from the early days onward. His primary work has been in MOS transistors and integrated digital circuits using them. In 1966 he invented the one-transistor dynamic RAM memory cell used in most all computers today. He was also an advocate for word and bit line redundancy for DRAM yield improvement. It was first used in the IBM 64Kbit DRAM and became a standard technique in the DRAM industry since then.

With coworkers he developed the concept of MOS transistor scaling in 1972, which is often cited as a guiding principle for microelectronics. In 1973 he became manager of a research group which developed advanced design concepts for 1-micron NMOS silicon gate technology. This included collaboration with Dr. H.N. Yu in demonstration of an exploratory 8Kbit DRAM chip with dimensions scaled to 1 micron, greatly reducing the chip area using electron-beam pattern definition and the first reported use of reactive ion etching (RIE) in chip fabrication.

Dr. Dennard was appointed an IBM Fellow in 1979 and has continued to develop technical strategy for scaling CMOS logic and memory technologies to very small dimensions, anticipating future scaling challenges and studying new device and circuit approaches to continue progress in microelectronics.

He is an author of over 100 technical papers and an inventor of 67 issued US patents.

Dr. Dennard is a Life Fellow of the Institute of Electrical and Electronics Engineers (IEEE), a member of the National Academy of Engineering, and a member of the American Philosophical Society. He received the IEEE Cledo Brunetti Award in 1982. In 1988 he was awarded the National Medal of Technology by President Reagan for his invention of the one-transistor dynamic RAM cell. He received the IRI Achievement Award from the Industrial Research Institute in 1989 and the Harvey Prize from Technion, Haifa, Israel, in 1990. Dr. Dennard was inducted into the National Inventors Hall of Fame in Akron, Ohio in 1997. In 2001 he received the Aachener and Munchener Prize for Technology and also was awarded the IEEE Edison Medal.

He received the Vladimir Karapetoff Award from Eta Kappa Nu in 2002 and the Lemelson-MIT Lifetime Achievement Award in 2005. Dr. Dennard received NEC's C&C Prize in 2006 and the Benjamin Franklin Medal in Electrical Engineering in 2007. He was awarded the Charles Stark Draper Prize by the National Academy of Engineering in 2009. He also was honored with the 2009 IEEE Medal of Honor. Dr. Dennard received the prestigious Kyoto Prize in 2013.

Dr. Dennard and his wife Jane Bridges live in Croton-on-Hudson, NY. They are active participants in Scottish Country Dancing and choral singing.

# TECHNICAL COMMITTEE REPORTS

# EDS VACUUM ELECTRONICS TECHNICAL COMMITTEE REPORT

The Vacuum Electronics Technical Committee (VETC) (Vacuum Devices) is a long-standing committee within the EDS, originally formed to represent Electron Tubes. Since the beginning, the VETC has made it their mission to identify technical trends, help foster new technical developments in the field, and serve the emerging needs of the vacuum device community at large. The committee members include recognized technical experts who represent a very wide spectrum of interests including but not limited to physical electronics, vacuum electronic technology, devices, and education. They work closely together with IEEE journal editors and conference organizers.

The annual face-to-face VETC meeting was held jointly with IVEC 2015 in Beijing on April 28, 2015. Dr. Richard True, Committee Chair, presided over the meeting. Seventeen members attended.

In the meeting, Dr. David Abe, General Chair of IVEC2014, gave a summary of the conference, Dr. Jinjun Feng presented the preliminary report on the ongoing IVEC2015, Dr. David

VETC Chair, Dr. Richard True (standing), hosted the VETC Meeting

Whaley, General Chair of IVEC2016, reported on the progress of the next conference, and Professor Claudio Paoloni described site selection for IVEC2017 in Oxford, United Kingdom. Other topics such as the next IEEE Transactions on Electron Devices Special Issue, the VETC website, and future occurrences of IVEC were also discussed at the meeting.

The VETC would like to express special thanks to Professors Richard

Carter and Manfred Thumm for their service as *IEEE Transactions on Electron Devices* Editors and Professor Claudio Paoloni for founding and maintaining of the VETC website http://vacuumelectronics.org.

Jinjun Feng 2015 IVEC Technical Program Chair

> Richard True EDS VTEC Chair

Committee meeting attendees (missing from picture is Prof. Gun-Sik Park, Dr. Armand Staprans, Dr. William Menninger and Prof. Yaogen Ding)

## AWARDS & RECOGNITION

# CALL FOR NOMINATIONS - IEEE FELLOW CLASS OF 2016

IEEE Fellow is a distinction reserved for select IEEE members. The honor is conferred by the Board of Directors upon a person with an extraordinary record of accomplishments in any of the IEEE fields of interest.

If you know of an IEEE colleague who is a Senior Member or Life Senior Member in good standing, has completed five years of service in any grade of IEEE Membership and who has made an outstanding contribution to the electronic or electrical engineering profession in any of the IEEE fields of interest, you can nominate this person in one of four categories: Application Engineer/Practitioner, Educator,

Research Engineer/Scientist or Technical Leader.

Nominations for the Fellow Class of 2016 are now being accepted.

To learn more about the Fellow program and the application process, visit the Fellow Web Site at http:// www.ieee.org/fellows. The deadline for nominations is 1 March 2015.

# 2014 EDS GEORGE E. SMITH AWARD

Rin Zhao EDS Vice-President of Publications and Products (2013-2015)

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. The George E. Smith Award was established in 2002 to recognize the best paper ap-

pearing in a fast turnaround archival publication of EDS, targeted to the IEEE Electron Device Letters. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The paper winning the 2014 George E. Smith Award was selected from 397 articles that were published in 2014. The paper is entitled, "Record Hole Mobility at High Vertical Fields in Planar Strained Germanium on Insulator With Asymmetric Strain." This paper appeared in the March 2014 issue of the IEEE Electron Device Letters and was

authored by Winston Chern, Pouya Hashemi, James T. Teherani, Dimitri A. Antoniadis, and Judy L. Hoyt.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 7, 2015, in Washington, DC. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society. I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Dimitri Antoniadis received his B.S. in Physics from the National University of Athens in 1970 and his M.S. and Ph.D. in

Electrical Engineering from Stanford University in 1972 and 1976 respectively. He joined the MIT faculty in 1978 and is currently the Ray and Maria Stata Professor of Electrical Engineering. He is member of the National Academy of Engineering, IEEE Life Fellow, and recipient of several professional awards. He has made seminal contributions in the area of solid-state processes and electronic devices, quantum-effect-devices, and CMOS device engineering. His current research is on technology and modeling of nanoscale electronic devices in Si, Ge, and III–V materials.

Winston Chern is a PhD candidate in Electrical Engineering and Computer Science (EECS) at MIT working with Professors Judy

Hoyt and Dimitri Antoniadis. He received his B.S. degree in Materials Science and Engineering at University of Illinois at Urbana-Champaign in 2010, and his M.S. in EECS from MIT in 2012. His research interests include Si/Ge and III-V semiconductor devices and their applications.

Pouya Hashemi received Ph.D. with honors from MIT in 2010 and is

currently a scientist at IBM Research focusing on exploratory CMOS devices and integration of advanced channelmaterials for sub-

10nm nodes. A member of IEEE EDS, his work has led to 80 publications and over 100 pending or issued patents.

Judy L. Hoyt received the B.S. degree in Physics and Applied Mathematics from the University of California, Berkeley in 1981, and the

Ph.D. degree in Applied Physics from Stanford University in December, 1987. From 1988 through 1999 Dr. Hoyt was on the research staff in Electrical Engineering at Stanford University. In January 2000 she became a faculty member in Department of Electrical Engineering and Computer Science, Massachusetts Institute of Technology, Cambridge, MA. Prof. Hoyt's primary research interests are in the areas of silicon-germanium heterostructure devices and technology, epitaxial growth, solar cells, Ge-on-Si photodetectors and CMOS front-end processing. She has authored or coauthored over 180 publications in these areas, and holds 6 patents. Prof. Hoyt has served as General Chair of the IEEE International Electron Devices Meeting (2001), is a Fellow of the IEEE, and a member of the American Physical Society. She received the IEEE Paul Rappaport Award in 1989, the IEEE George Smith Award in 2005, and the IEEE Andrew S. Grove Award in 2011. Additional information is available at http:// www-mtl.mit.edu/wpmu/jlhoyt/

James Teherani joined the Columbia University's Department of Electrical

Engineering as an assistant professor in July 2015. James received his BS in electrical and computer engineering from the University of Texas

at Austin in 2008, and his MS and PhD degrees in electrical engineering and computer science from the Massachusetts Institute of Technology in 2010 and 2015, respectively. James's research interests include electronic devices, quantum structures, and properties of emerging materials, especially 2D semiconductors and graphene. His work spans the study of fundamental material properties to the optimization of real-world devices.

Bin Zhao EDS Vice-President of Publications and Products (2013–2015) Fairchild Semiconductor Irvine, CA, USA

# 2014 EDS PAUL RAPPAPORT AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. Every year, the Society confers its prestigious Paul Rappaport Award to the best paper published in the *IEEE Transactions on Electron Devices*. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The winning paper was selected from over 600 articles that were published in 2014. The winning paper is entitled "Top-Down Fabrication of Epitaxial SiGe/Si Multi-(Core/Shell) p-FET Nanowire Transistors." This paper was published in the April 2014 issue of the IEEE Transactions on Electron Devices, and was authored by Sylvain Barraud, Jean-Michel Hartmann, Virginie Maffini-Alvaro, Lucie

Tosti, Vincent Delaye and Dominique Lafond.

The award will be presented at the plenary session of the International Electron Devices Meeting to be held on December 7, 2015, in Washington, DC. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Dr. Sylvain Barraud is leading the development of nanowire-based CMOS devices at CEA-LETI. His current research interests include the

device physics, the fabrication and

characterization of nanowire transistors and single electron nanodevices.

Dominique Lafond joined LETI, in 1978, and now works at the Nanocharacterization Platform (PFNC) as a specialist of electron

microscopy. He is currently engaged in the characterisation of semiconductor processes and devices using transmission electron microscopy.

Lucie Tosti has worked on different processing steps for silicon device development, i.e., etching, lithography, diffusion, etc., during her career. Her research interests include process integration for advanced SOI devices.

Dr. Jean-Michel Hartmann is a CEA-LETI senior scientist. He is specialized in the epitaxial growth and structural characterization of Si/SiGeC

heterostructures for nanoelectronics and optoelectronics. He has authored or co-authored close to 400 publications or conference proceedings (h index: 31).

Virginie Maffini-Alvaro received the B.Sc. degree in physics from Heriot-Watt University, Edinburgh, U.K., in 2003. In 2005, she

joined CEA-Leti, Grenoble, France, where she is working on advanced CMOS devices with the Innovative Device Laboratory.

Dr. Vincent Delaye, after obtaining his master's degree from "Telecom Saint Etienne", obtained the Ph.D. from