JANUARY 2019 VOL. 26, NO. 1 ISSN: 1074 1879

EDITOR-IN-CHIEF: CARMEN M. LILLEY

### TABLE OF CONTENTS

| TABLE OF GOIVIENTS                        |

|-------------------------------------------|

| **TECHNICAL BRIEFS                        |

| UPCOMING TECHNICAL MEETINGS               |

| SOCIETY NEWS                              |

| Awards and Call for Nominations           |

| YOUNG PROFESSIONALS                       |

| CHAPTER NEWS                              |

| Mini-Colloquia and Distinguished Lectures |

| REGIONAL NEWS36                           |

| EDS MEETINGS CALENDAR50                   |

# TECHNICAL BRIEFS

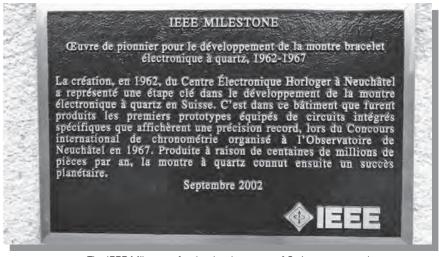

# Marvels in Process Technology Before and During Moore's Law Era

By Joachim N. Burghartz, Institut für Mikroelektronik Stuttgart (IMS CHIPS), Germany

Process technology has always been the guiding and decisive factor in keeping Moore's Law going. Since the 1980's, the semiconductor roadmap helped us looking at the processing needs ahead—this was well coordinated 'engineering on demand' by semiconductor manufacturers, equipment vendors and academics with countless brillant efforts and results on the way. However, there were also marvels in process technology that came out of the blue or with an impact that was not foreseen at all. This third article of the series on 'Marvels of Microelectronics Engeneering' will highlight a few of those.

One might think that in the years before Moore's Law was formulated technology progress in semiconductors was solely based on marvellous discoveries. According to Adolf Goetzberger, former director of the Fraunhofer Institute for Applied Solid State Physics and retired founding director of the Fraunhofer Institute for Solar Energy Systems in Freiburg, Germany, this was, however, not the case in the old days. Goetzberger worked with Shockley from 1958 to 1963 after in 1957 the 'Traitorous Eight' left Shockely Laboratories in Palo Alto. In my recent personal conversation with him he rememberd about Shockley: "We had agreed that I would be in charge of the experiments and he would do the theory. This turned out to become a very good collaboration". Apparently, the theoretical work by Shockley came first and experiments followed to demonstrate the theories. This approach might have been triggered by

(continued on page 3)

### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at clilley@uic.edu

MESSAGE FROM EDITOR-IN-CHIEF......52

# ELECTRON DEVICES SOCIETY

#### President

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

#### **President-Elect**

Meyya Meyyappan NASA Ames Research Center E-mail: m.meyyappan@nasa.gov

#### Treasurer

Subramanian S. Iyer

UCLA

E-mail: iyer@ieee.org

### Secretary

Jacobus Śwart FEEC/UNICAMP

E-mail: jacobus@fee.unicamp.br

#### Jr. Past President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### Sr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

# Vice President of Membership and Services

Ru Huang Peking University

E-mail: ruhuang@pku.edu.cn

# Vice President of Publications and Products

Tsu-Jae King Liu University of California at Berkeley E-mail: king@eecs.berkeley.edu

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

NanoRel E-mail: radhakrishnan@ieee.org

Vice President of Technical

# Committees & Meetings Ravi Todi

GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

#### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

#### **Content Management**

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2019                                                                                                                   | Term                                          | 2020                                                                                                                                            | TERM                                                 | <u>2021</u>                                                                                                                              | TERM                                          |

|------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| Joachim N.<br>Burghartz<br>Ru Huang<br>Shuji Ikeda<br>Meyya Meyyappan<br>Arokia Nathan<br>Jacobus W. Swart<br>Bin Zhao | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) | Roger Booth<br>Mukta Farooq<br>Edmundo A.<br>Gutierrez-D.<br>Benjamin Iniguez<br>Carmen M. Lilley<br>Durga Misra<br>Manoj Saxena<br>Sumant Sood | (1)<br>(2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(1) | Paul Berger<br>Navakanta Bhat<br>Maria De Souza<br>Kazunari Ishimaru<br>William (Bill) Nehrer<br>Murty Polavarapu<br>Camilo Velez Cuervo | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) |

# NEWSLETTER EDITORIAL STAFF

#### **Editor-In-Chief**

Carmen M. Lilley University of Illinois at Chicago E-mail: clilley@uic.edu

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Rinus Lee GlobalFoundries E-mail: rinuslee@ieee.org

# Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

# Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Edmundo A. Guiterrez-D. INAOE E-mail: edmundo@inaoep.mx

#### **REGION 8**

#### Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Marcin Janicki Lodz University of Technology E-mail: janicki@dmcs.pl

#### **UK, Middle East & Africa**

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Mike Schwarz Robert Bosch GmbH E-mail: mike.schwarz1980@ googlemail.com

#### REGION 10

# Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editor-in Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

### Newsletter Deadlines

| ISSUE         | DUE DATE                 |

|---------------|--------------------------|

| April<br>July | January 1st<br>April 1st |

| October       | July 1st                 |

| January       | October 1st              |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016–5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2019 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

# Marvels in Process Technology before and during MOORE'S LAW ERA

(continued from page 1)

Former Shockley Laboratories in Palo Alto (left) and Adolf Goetzberger, research staff at Shockley Labs in the 1960's (Images provided by Adolf Goetzberger)

Shockely's personal experience from the demonstration of the first transistor by Bardeen and Braittain in 1947; it was just after the transistor was demonstrated experimentally that Shockley could complement that birth of semiconductors by his transistor theory.

However, also at Shockley Labs there were instances where experimental success came first. Goetzberger: "In the old Labs in San Antonio Road, diffusion furnaces were set up in a former barn. We did not know about clean work conditions. The pn junctions we fabricated were generally not ideal. More or less by accident, but also by my structured follow-up on observations and reproduction of experiments, I found a technology which gave us perfect junctions every time. This is the gettering step which has been customary in semiconductor technology for several decades". Goetzbergers discovery of metal gettering is a true marvel in semiconductor process technology. He and Shockley published this in the Journal of Applied Physics in 1960. For many years highly doped p-type silicon wafers with lower doped epitaxial device layers had been used to getter metal precipitates and achieve ideal pn junctions. Adolf Goetzberger received the 1983 J.J. Ebers Award in honor of this achievement.

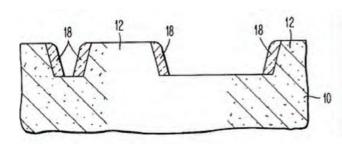

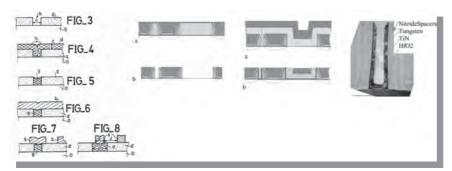

While Goetzbergers discovery was accidental and provided a solution to a known problem, another great invention in microelectronics the sidewall spacer-showed up as an artifact of anisotropic dry etching. Etching in a gaseous atmosphere instead of in liquid chemicals gained attention when both more accurate transfer of lithographic pattern and high selectivity to underlying layers became crucial. In 1975, Texas Instruments demonstrated the first all-dry-etched device, a CCD shift register. However, with the anisotropic nature of the so-called reactive ion etch (RIE) a problem arised: film removal at a steep sidewall became very difficult; only a substantial overetch could remove the undesired residues. It took about five years until Bernie Pogge at IBM thought of making use of this previously undesired sidewall feature. In 1981, he filed US patent 4,256,514 in which he decribed that sidewall to be used as a lateral spacer with its dimension being controlled by the thickness of the previously deposited film. IBM Fellow Tak Ning remembers: "Once the concept was out, many companies explored using sidewall spacer to improve devices or to come up with novel device structures".

First was Ning's invention of the double-poly self-aligned bipolar transistor which he presented in a Late News paper at the 1980 IEDM. He placed a sidewall spacer inside the lithographically defined emitter window and, thus, achieved a sub-lithographic emitter leading to a much reduced intrinsic base resistance. The sidewall also provided a self-aligned isolation of the emitter

Schematic illustration of the sidewall spacer from Bernie Pogge's US Patent 4,256,514 (left) and SEM cross section of a MOS gate with an LDD spacer (middle), and Tak H. Ning, inventor of the double-poly self-aligned bipolar transistor (right). (Images from J.N. Burghartz, "Guide to State-ofthe-Art Electron Devices," Wiley)

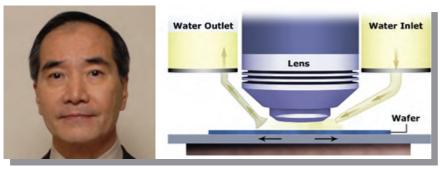

Burn Lin, inventor of immersion lithography (left), schematic of practical implementation of immersion lithography in a commercial step-and-repeat equipment (right)

polysilicon contact to the extrinsic base polysilicon. Ning's double-poly self-aligned bipolar transistor became a standard in semiconductor industry and—in its general form—is still in manufacturing, though today with an epitaxial SiGe:C rather than an implanted Si intrinsic base (see EDS Newsletter Ocober 2018). Tak Ning received the 1989 J.J. Ebers Award partly for his pioneering contribution to bipolar technology.

Next was the lightly-doped drain (LDD) structure using source/drain implants before and after formation of a sidewall-spacer around the gate contact of a MOS device. Ning: "Seiki Ogura's LDD concept was reported in 1981 at IEDM. It was quite effective in suppressing the hot-carrier effect, but only for 5 V designs. Once voltage was scaled down to 2.5 V hot-carrier effect was no longer an issue, and LDD was no longer needed. I would say that LDD was used in high-speed CMOS logic for less than 10 years by the industry".

Another application with high impact was the self-aligned silicide (salicide) process introduced by a team at Texas Instruments, which provides self-aligned metallization at the source, drain and gate contacts of a MOS transistor. The late Roger A. Haken, in whose memory the IEDM named its Best Student Paper Award, was a member of that pioneering team. They published this breakthrough in the 1985 February issue of the IEEE Transactions on Electron Devices.

The sidewall spacer also affected the art of lithographic patterning in

different ways. In the 1970's, that was used to form a sub-lithographic feature, e.g. a gate contact of a MOS-FET. The dummy feature, at which the sidewall spacer was formed and which was removed later on, was called mandrel. Since the sidewall spacer was formed around the mandrel, it had partly to be etched off. This technique was known as sidewall image transfer (SIT). The interest in SIT disappeared with the progress made in lithography but SIT returned in recent years with use in double- and multiple-patterning.

Progress in photolithography was often based on concerted engineering actions but in a few cases innovations appeared as true marvels. Photolithography was introduced in 1958 by Lathrop and Nall from Army Research Laboratories in the US. It became an integral part of the planar process technology, invented by Jean Hoerni in 1957, and the planar integrated circuit, invented by Bob Noye, both with Fairchild at that time and two of those Traitorous Eight whose sudden leave brought Adolf Goetzberger to Shockley Labs.

Tim Brunner, a Globalfoundries Fellow, who spent his professional life in photolithography, mentiones a few milestones: "The chemically amplified photoresist process, invented in late 1980's by Grant Willson and Hiroshi Ito, was essential to high volume manufacturing for three decades. Step-and-scan exposure tools, invented by Perkin-Elmer/SVG in 1973 and then perfected by Nikon and ASML, advanced data-

preparation methods, such as Optical Proximity Correction (OPC) and Sub-Resolution Assist Features (SRAF), and computational lithography methods like Source Mask Optimization (SMO) need to be mentioned." He also points to Extreme Ultra Violett (EUV) lithography as an "incredible engineering tour-deforce that will soon emerge as production-worthy." To him, however, "193 nm immersion lithography was a true marvel that came out of the left field to defeat the crappy 157 nm exposure technology."

Immersion lithography, using water instead of air between lens and wafer, was introduced in 1987 by Burn Jeng Lin, then at IBM, at the Microcircuit Engineering Conference on the future of subhalf-micrometer optical lithography. He remembers: "In that presentation, I told the audience that immersion lithography would be a way to extend optical lithography. There was no immediate follow up because there were many easier ways to extend optical lithography". Lin further: "By 2002, the wavelength has been reduced from 436 nm to 365, 248, 193 and heading to 157 nm. The numerical aperture of the imaging lens had been increased from 0.18, through many steps, to 0.93. Most resolution enhancement techniques had been implemented. That is: unwanted reflections and vibrations in the imaging system have been managed, phase shifting masks were used, off-axis illumination was implemented, and optical proximity correction was introduced. We were facing the limit of Moore's law scaling at the 65 nm logic node and could at most stretch to the 55 nm half node. Reducing the wavelength to 157 nm seemed to be the last resort to improve the resolution but that ran into tremendous difficulties". Burn Lin explains further: "My solution to the above problems was to stay away from the 157 nm wavelength. The vacuum wavelength of 193 nm light becomes 134 nm in water due to its refractive index of 1.44 at the 193 nm

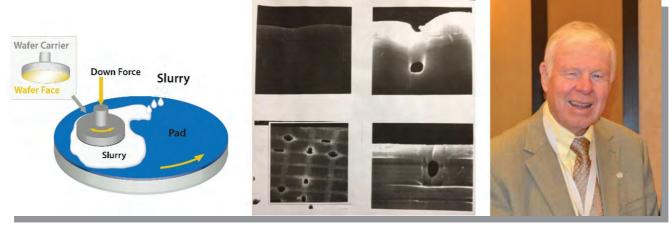

Schematic illustration of chemical-mechanical polishing (CMP) (left), images from the first device experiments (middle) and CMP inventor Klaus Beyer (right). (Photographs provided by Klaus Beyer)

vacuum wavelength. This wavelength is much shorter than 157 nm and can keep the entire optical train in 193 nm. This includes the light source, the illuminator, the mask, the pellicle, the imaging lens, and the environment. One only has to keep the space between the last element of the imaging lens and the photoresist immersed in water and the actinic wavelength will be 134 nm. This configuration is, of course, immersion lithography. At that time the entire lithography community including suppliers and users were all concentrating on making 157 nm work. One billion dollars was estimated to have been spent on this effort." Lin, who was 16 years with TSMC, as senior director and vice president, remembers: "A more difficult task followed. We had to turn the industry around from 157 nm conventional to 193 nm immersion, technically, politically, and commercially." Burn Lin received the 2013 IEEE Jun-Ichi Nishizawa Medal for his pioneering work and his leadeship in immersion lithography.

Immersion lithography turned out to carry the 45 nm, 40 nm, 32 nm, 28 nm, 20 nm, 16 nm, 14 nm, 10 nm, and 7 nm nodes in a span of about 12 years. Besides immersion, also those many other 'tricks' mentioned have to employed to arrive at such small dimensions. One of those extras is double- and multiple patterning, taking advantage of patterning two or more masks to reduce the combined pitch or the SIT enabled by the sidewall spacer, the other marvel in microelectronics we mentioned. This is not the only entanglement of marvellous inventions in microelectronics.

Photolithography also has a close relationship with another marvel in microelectronic engineering, i.e. chemical-mechanical polishing (CMP). This process is applied numerous times in the course of circuit integration to return to a perfectly planar wafer surface. This allows to arrive at an optimum resolution in a trade-off against a small depth-offocus (DOF).

CMP on device structures was invented by IBM Fellow Klaus Beyer. Beyer was assigned by his manager the task of finding a way to eliminate silicon wafer surface scratching caused primarily by the traditional brush cleaning method used to remove the colloidal silica polishing slurry. In the course of his investigations Beyer started to successfully use megasonic cleaning to remove those residues. In a personal communication Klaus Beyers said: "The first CMP application to silicon surfaces was achieved by Walsh and coworkers at Monsanto Corp. in 1962. Approximately in 1973 Monsanto engineers installed their CMP process at IBM. On March 20, 1983,

at the 1983 American Chemical Society Meeting in Seattle/Washington, I showed voltage breakdown measurements of oxides grown on silicon surfaces cleaned by megasonic cleaning of colloidal silica covered silicon surfaces. I mentioned the possibility of this process for device applications". About 12 months earlier he was approached by a development manager and asked to also work on trench refill using glass reflow. His then two managers made a deal and had him work half-time on each of those tasks. At 1.5-µm trench width the glass trench refill process caused unwanted mounds after reflow at random locations. Out of desperation, on a day in January 1983 Klaus Beyer applied his meanwhile scratch-free polishing process from his other job assignment with the result that the device structures became perfectly planar. This was the birth hour of CMP on device structures. Beyer remembers the difficulties they had at IBM before CMP was applied to multi-level interconnects: "A very important problem was also the wiring of computer chips. The extension from three- to four-level wiring was very difficult. Planarization of interlevel oxides was done by applying photoresist as a planarization medium with a subsequent RIE etchback. However, this only worked for certain layout configurations." In 2002, Klaus Beyer retired from IBM

Contact/Via plug principle: detail of France/EU patent: 84.05906 (US patent #: 4,592,802) filed on April 13, 1984 by Simon Deleonibus and Guy Dubois, for Thomson Semiconductors (now ST Microelectronics) (left). First publication of totally self aligned damascene metal gate last/ HiK CMOS integration at IEDM 2002 by CEA, LETI and STMicroelectronics (3 images on right side). (Images provided by Simon Deleonibus)

after having received a major invention award fom IBM's CEO Lou Gerstner, and in 2015, he received a Lifetime Achievement Award from the International Conference on Planarization/CMPTechnology (ICPT).

CMP was also instrumental in enabling Cu damascene, optimized tungsten contact/via plug formation in aluminum multi-level interconnects in the 1990's and to realize metal replacement gates in the 2000's. The plug concept goes back to work at ST Microelectronics in 1983/84 by IEEE Fellow Simon Deleonibus and Guy Dubois. Simon Deleonibus explains: "I was hired by Thomson Semiconductors in 1981, after my PhD. We tried to increase, as much as possible, the step coverage of sputtered or evaporated aluminum in high-aspect-ratio contacts to avoid high contact resistance and reliability issues. We tried several solutions to smoothen the contact opening topography and came to the conclusion that refilling the contact with

a metal by a conformal deposition would solve both step coverage and reliability problems. We filed the basic generic patent on the contact/via plug principle in early 1984 (France/ EU patent: 84.05906, US patent 4,592,802). Our patent covered any conformally deposited metal and any type of removal process. It also offered to reduce the metal levels contacted pitches. I joined CEA, LETI in 1986 and continued my work with my colleagues there. Finally, we published the contact/via plug for 16Mb EPROM at IEDM 1989, featuring W as refill material, TiN/Ti barrier/contact metal stack. W and TiN/Ti were smoothened and etched back by RIE at that time. CMP of W was applied much later by the mid 1990s when the cost-of-ownership was less an issue in synergy with interlevel dielectric planarization and later on Cu integration. The whole microelectronics business is using the plug principle at the sub-10 nm level and has extended it to Through Silicon Vias (TSV). The French Academy of Technologies awarded me with their 2005 Grand Prix for the invention and development of the plug principle, a major innovation for the industry."

Simon Deleonibus continues: "By 1995, I started to develop the damascene metal-gate-last integration. The plug principle was of great inspiration to apply a low thermal budget process on the metal gate material. Annealing before metal deposition was necessary to self-align sources and drains to gate, protect salicided junctions from degradation, keep the metal workfunction value stable and avoid any reaction with the underlying gate dielectric. In 1996, I and François Martin, both with CEA, LETI, filed the patent (France/EU patent 96.15436, US patent 6,346,450) showing the way to integrate the gate-last metal with total self alignment, thanks to the use of a replacement material and the planarization of the final metal by CMP. We published the first results using a W/TiN/HiK(Hf02 deposited by Atomic Layer Deposition) gate stack at IEDM 2002. Today, the damascene gate is massively used by Intel and other manufacturers!".

The gettering technique, the side-wall spacer with its impact on self-aligned bipolar technology, LDD, sacilide and lithographic multiple patterning, immersion lithography, CMP and the via/contact plug principle with extension to damascene gate are true marvels in semiconductor process technology. They all had tremendous impact on keeping Moore's Law to go on.

# A REVIEW OF THE 2018 IEEE INTERNATIONAL ELECTRON DEVICES MEETING (IEDM)

BY KIRSTEN MOSELUND AND RIHITO KURODA

The 64th Annual IEDM conference (www.ieee-iedm.org), sponsored by the IEEE Electron Devices Society, was held December 1–5, 2018, at the Hilton San Francisco Union Square Hotel. Special Focus Sessions of invited papers explored some of today's most important areas of research and included topics on quantum computing, 5G wireless communications, wide-bandgap power devices, and the future of interconnects.

Some highlights of the conference in the area of Neural Networks, Artificial Intelligence and Neuromorphic Computing included a talk on "Exploiting Hybrid Precision for Training and Inference: A 2T-1FeFET-Based Analog Synaptic Weight Cell," by X. Sun et al. from Arizona State Univ., Univ. Notre Dame, and Georgia Institute of Technology. This team of university researchers participating in the SRC/DARPA-sponsored ASCENT program described an in-memory computing architecture in which computing is done at the location of the data storage to accelerate training. This approach also trades unnecessarily high levels of precision

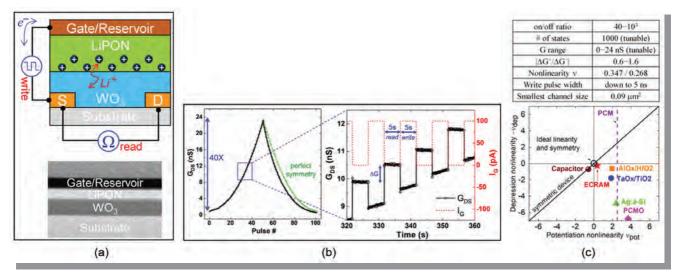

during inferencing for greater speed and energy efficiency. Previous such "in-memory computing" approaches have made use of various non-volatile memories (NVMs), but their overall accuracy has suffered. Here, the team proposed a novel compact analog synaptic weight cell consisting of two MOSFETs and one ferroelectric transistor (2T-1FeFET) to handle both the training and inferencing functions. They used an experimentally calibrated FeFET SPICE model to validate the device performance and embedded it in a convolutional neural network using both the MNIST and CIFAR-10 training datasets, and achieved accuracies of ~97.3% and ~87%, respectively. Another highlight is on an Electrochemical Synaptic Cell titled "ECRAM as Scalable Synaptic Cell for High-Speed, Low-Power Neuromorphic Computing," by J. Tang et al. from IBM. Various non-volatile memory technologies such as RRAM and PCM are being investigated for use as synaptic cells for neuromorphic computing, but they tend to have non-ideal switching characteristics (e.g., asymmetric weight update, limited endurance, and elevated levels of stochasticity, or random behavior). Instead, IBM researchers described a novel scalable electrochemical random access memory (ECRAM) device based on lithium (Li) ion intercalation in tungsten oxide (WO<sub>a</sub>) that can be used as a scalable synaptic cell, see Figure 1. These non-volatile ECRAMs showed high levels of switching symmetry and linearity, good data retention, and up to 1,000 discrete conductance levels useful for multi-level operation in large memory arrays. The researchers demonstrated successful high-speed programming, using 5ns pulse widths with 300 x 300 nm<sup>2</sup> ECRAM devices. Ultra-low switching energy of 1 fJ is projected for scaled 100 x 100 nm2 devices. MNIST image-recognition simulations based on experimental data showed 96% accuracy.

In the area of Memory Technology, a highlight was Intel's presentation on the integration of e-MRAM With 22 nm FinFETs in the talk titled "MRAM as Embedded Non-Volatile

Figure 1. (a) The left image below shows a schematic of the ECRAM device (on top) and a cross-sectional electron microscope image (below it). (b) In the middle is a plot of the source-drain conductance (GDS) during gate current pulses, showing good symmetry and a large on-off ratio (~40). (c) To the right is a table summarizing key ECRAM metrics for neuromorphic computing, and a comparison with other technologies.

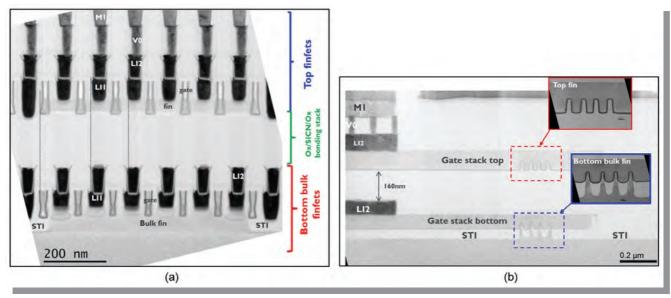

Figure 2. Highest-Density 3D Sequentially Stacked FinFETs. (a) At left above is a cross-sectional electron microscope image of the fabricated 3D stacked FinFETs along fins and across gates, showing the tight alignment achieved by the top processed layers (Gate Li1, Li2) toward the bottom layers. (b) At right is a cross-sectional image of the final devices across fins with the gates covering the fins.

Memory Solution for 22 FFL FinFET Technology," by O. Golonzka et al. from Intel. Embedded non-volatile memory (e-NVM) technologies, which retain data when power is turned off, are essential for Internet of Things (IoT), mobile and other applications, but the dominant embedded technology, e-flash, suffers from cost and scaling issues. Embedded MRAM (magnetoresistive random access memory), with its low manufacturing costs and high data retention and switching endurance, is a compelling alternative. It also has the potential to replace other types of embedded memory besides e-flash, and to serve as a building block for future logic devices as well. Integrating MRAM with mainstream CMOS technology has been problematic for various reasons, but here Intel researchers described the successful integration of embedded MRAM into the company's ultra-low-power 22 nm FinFET CMOS technology on full 300 mm wafers. The work represents a major step forward toward commercial use of the technology for high-performance, low-power applications. The magnetic tunnel junction-based memory cells are built from dual MgO magnetic tunnel junctions (MTJs) separated by a CoFeB-based layer in a 1 transistor-1 resistor (1T-1R) configuration in the interconnect stack. To demonstrate their performance, Intel built 7.2 Mb MRAM arrays which achieved industry-leading data retention (10 years with <1e-6 error rate at 200°C) and endurance (>106 write endurance). Another highlight was on highly integrated self-aligned 3D Crosspoint Storage-Class Memory (SCM) in the paper "High-Performance, Cost-Effective 2z nm Two-Deck Crosspoint Memory Integrated by Self-Align Scheme for 128 Gb SCM" by T. Kim et al. at SK Hynix. Storage-class memories are an evolving class of high-density solid-state devices that attempt to combine the speed and small footprints of "working" computer memory such as DRAM with the non-volatility of flash memory at a low cost per bit. Researchers from SK Hynix discussed a novel 3D crosspoint memory cell for use in SCMs that is built from phasechange materials integrated with a chalcogenide selector device. The researchers fabricated the cells using self-aligned processes and precise materials-engineering techniques to preserve the electrical characteristics of these sensitive materials, which were integrated into a high-density 2z nm two-deck architecture for the first time. The devices demonstrated a read latency of <100 ns in a 16 Mb test array, which the researchers say is suitable for use in a 128 Gb SCM.

A few highlights for the area of advances in CMOS technology include the presentation by Imec researchers on highest-density 3D sequentially stacked FinFETs in the paper titled "First Demonstration of 3D Stacked FinFETs at a 45 nm Fin Pitch and 110 nm Gate Pitch Technology on 300 mm Wafers," by A. Vandooren et al. The Imec researchers reported on 3D sequentially stacked FinFETs that have the tightest pitches ever reported in such a stacked architecture-45 nm fin pitch and 110 nm gate pitch, see Figure 2. The 3D architecture makes use of a sequential integration process yielding tight alignment between very thin top and bottom Si layers. The junctionless devices in the top layer were fabricated and transferred using low-temperature (≤525 °C) processes to avoid performance degradation, and a 170 nm dielectric was used to bond the two wafers. The top layer is so thin that the bottom layer could

be patterned right through it by means of 193 nm immersion lithography, which connects the two via local interconnect. The researchers evaluated various gate stacks, ultimately choosing TiN/TiAl/TiN/HfO, with a LaSiO dipole inserted into the stack. The combination demonstrated good threshold voltage tuning, reliability and low-temperature performance. In addition, the paper "High-Performance InGaAs Gate-All-Around Nanosheet FET on Si Using Template-Assisted Selective Epitaxy" by S. Lee et al. from IBM focused on InGaAs Channels for High-Mobility N-FET Nanosheets. IBM researchers looked to III-V materials as a replacement for Si channels. They monolithically integrated highperformance InGaAs gate-all-around nanosheet N-FETs on Si using what they call a "Template-Assisted-Selective-Epitaxy" (TASE) process designed to integrate high-mobility material formed into nanoscale sheets. The nanosheets are scaled to 10 nm thicknesses and the transistors have <40 nm gate lengths, with the gate metal wrapping around the channel for optimal gate control. The devices demonstrated excellent current drive capability ( $I_{op} = 355 \mu A/$ μm), as well as subthreshold swing of 72 mV/decade. The researchers say device performance can be further improved by scaling gate length/nanosheet dimensions. The devices are compatible with current silicon manufacturing tooling.

In the area of photonics, one highlight is on Ge-on-Si lock-in pixels for distance ranging in the paper titled "High-Performance Germanium-on-Silicon Lock-In Pixels for Indirect Time-of-Flight Applications" by N. Na et al. from Artilux. Rangeimaging is key to many electronics applications such as hand tracking, facial recognition, localization/mapping for navigation, object detection/ ranging for autonomous driving, and many others. However, new technologies are needed to enable accurate range-imaging at wavelengths beyond the visible range, in order to ensure eye safety and for better performance. One approach is to develop better "lock-in" pixels for use in image sensor arrays. Lock-in pixels provide distance information indirectly, using the time-of-flight (TOF) principle. TOF systems determine the distance of an object by shining light on it, reflecting that light to the pixel and noting when it arrives, and calculating the distance light would have traveled in that time. Artilux, Inc. researchers reported the first Ge-on-Si lock-in pixels for indirect TOF measurements for such uses. These Ge-on-Si pixels demonstrated both high sensitivity (quantum efficiency >85% and >46% at 940 nm/1550 nm wavelengths, respectively) and high resolution (demodulation contrast >0.81 at 300 MHz), a significant improvement from their pure Si pixel counterparts. The technology may open new routes to high-performance indirect TOF sensors and imagers, as well as the potential adoption of eye-safe lasers for consumer electronics. The researchers say the lock-in pixels were developed via a foundry's image sensor platform technology and hence may be ready for mass production in the near future. In addition, the paper titled "Quadratic Electro-Optical Silicon-Organic Hybrid RF Modulator in a Photonic Integrated Circuit Technology" by P. Steglich et al. from IHP/Technical University of Applied Sciences Wildau discussed a Si-Organic electro-optical modulator for low-power photonic ICs. The team of researchers led by IHP reported on a hybrid silicon-organic electro-optical (EO) modulator for RF photonic ICs that takes advantage of the quadratic EO effect, opening a path to ultra-low-power photonic building blocks such as tunable filters, switches and RF modulators. Existing hybrid silicon-organic EO modulators have high loss and modulation bandwidth limitations along with reliability and stability issues because they are based on the linear

EO effect, which requires a high voltage to initially "pole" (i.e., activate) the EO material. They also require periodic re-poling, which reduces reliability. The researchers investigated a spin-coated organic polymer that employs the quadratic EO effect instead of the linear effect. It doesn't require post-process poling, and with it the researchers reported an ultra-low per-bit energy consumption of 87 aJ/bit and modulation at just 1 V-cm, which would lead to RF modulators that operate at CMOScompatible driver voltages.

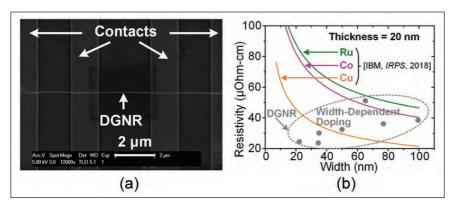

Other noteworthy presentations included CMOS-compatible Graphene interconnects in "CMOS-Compatible Doped-Multilayer-Graphene Interconnects for Next-Generation VLSI" by J. Jiang et al. from Univ. California-Santa Barbara. Integrating graphene into the interconnect scheme holds the promise of increasing performance and limiting power consumption in next-generation CMOS ICs, as graphene offers high conductivity and is not prone to electromigration. One of the main challenges for practical implementations are the high temperatures typically needed to form graphene (800-1000 °C), which would damage the active devices already fabricated at the front-end-of-the-line. University of California-Santa Barbara researchers reported on a new approach in which a low-temperature (300 °C) pressure-assisted solidphase diffusion process enables the growth and doping of multi-level CMOS-compatible graphene nanoribbons, see Figure 3. These nanoribbons demonstrated a markedly lower contact resistance (<20 Ω-μm) than a copper interconnect, yielded a ~4x increase in device performance, and showed negligible electromigration under 100 MA/cm<sup>2</sup> at >100 °C. These results point to a practical and industry-compatible approach toward exploiting the unique electrical properties of graphene in siliconbased CMOS ICs. Another highlight was on nanoelectromechanical

Figure 3. Above are (a) an electron microscope image of 20-nm-wide doped graphene nanoribbon (DNGR) in a four-probe test structure; and (b) the measured resistivity of the DGNR vs. wire width from 4-probe measurements. Reported resistivities of Cu, Co and Ru wires (with liners/barriers) are plotted, assuming 20-nm wire thickness.

switches for ultra-low-power computing by Z.A. Ye et al. from the Univ. of California-Berkeley in the talk "Demonstration of 50-mV Digital Integrated Circuits with Microelectromechanical Relays." ICs made from nanometer-scale mechanical relays are intriguing for some ultra-low-power digital computing applications because, in principle, they can achieve zero off-state leakage current, resulting in zero static power consumption. They also offer abrupt switching characteristics, but although in principle they can be operated with a very low gate voltage swing, in practice hysteretic switching behavior often requires the use of higher bias levels. Researchers from the University of California-Berkeley have overcome this in a novel relay design, and reported a 50-mV operation of digital ICs at room temperature for the first time. To reduce switching hysteresis losses and further enable low gate voltage operation of these relay-based ICs, a body-biasing design was employed to reduce the number of relay contacts and a self-assembled monolayer molecular coating (PFOTES) for low adhesion was used. Finally, the presentation titled "Highly Performant Integrated pH Sensor Using the Gate-Protection Diode in the BEOL of Industrial FDSOI" by G.T. Ayele et al. from STMicroelectronics/Universite de Lyon/Universite de Sherbrooke looked at a pH sensor in the BEOL. The STMicroelectronicsled team reported a novel and highly sensitive pH sensor fabricated in the BEOL using a mainstream fully depleted FDSOI CMOS process. The pH sensing exploits the drain-induced barrier lowering (DIBL) effect with respect to a floating gate, via a gate protection diode in the interconnect stack. The current in the diode, which varies according to the pH in the fluid under study, turns the transistor on or off. The device demonstrated a sensitivity of 1.25 decade/pH and the researchers say 6.6 decade/pH is achievable, or more than 7x better than existing state-of-the-art solidstate pH sensors.

In addition to the many exciting technical talks, there were also 90-minute tutorials bridging the gap between textbook-level knowledge and leading-edge current research on "Reliability Challenges in Advanced Technologies" by Ryan Lu at TSMC, "STT-MRAM Design and Device Requirements" by Shinichiro Shiratake at Toshiba Memory, "Quantum Computing Primer" by Mark B. Ritter at IBM, "PowerTransistors in Integrated BCD Technologies" by Hal Edwards at Texas Instruments, "Design-Technology Co-optimization at RF and

mmWave" by Bertand Parvais at Imec, and "Emerging Device Technologies for Neuromorphic Computing" by Damien Querlioz at CNRS. In addition, there were full-day short courses on "It's All About Memory, Not Logic!" organized by Nirmal Ramaswamy at Micron and "Scaling Survival Guide in the More-than-Moore Era" organized by Jin Cai at TSMC. Monday's Plenary Presentations were on "Future Computing Hardware for AI" by Dr. Jeffery Welser, Vice President, IBM Research-Almaden, "4th Industrial Revolution and Foundry: Challenges and Opportunities" by Dr. Eun Seung Jung, President of Foundry Business, Samsung Electronics, and "Venturing Electronics into Unknown Grounds" by Prof. Gerhard P. Fettweis, TU Dresden. Tuesday's career-focused luncheon event featured industry and scientific leaders talking about their personal experiences in the context of career growth. It was moderated by Curtis Tsai of Intel, and the speakers were Veena Misra, Distinguished Professor and Director of the ASSIST Center at NC State University, and John Chen, Vice President of Technology and Foundry Management at Nvidia. The Tuesday evening panel session was on "The Next 25 years in Electronics." The panelists focused on how the semiconductor technology will evolve and what new lifechanging technologies it will enable in 25 years from today (circa 2045). The group included industry leaders, long-tenured professors, and government participants from the early days of DARPA for this 25-year lookback and 25-year look forward. Finally, there was a vendor exhibition, a poster session on MRAM technology organized by the IEEE Magnetics Society, and a student research showcase hosted by the Semiconductor Research Corporation.

Edited by Carmen M. Lilley

# UPCOMING TECHNICAL MEETINGS

# 2019 IEEE ELECTRON DEVICES TECHNOLOGY AND MANUFACTURING CONFERENCE (EDTM)

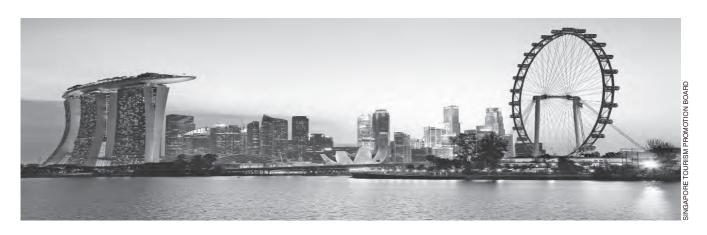

It is our great pleasure to invite you to the 2019 IEEE Electron Devices Technology and Manufacturing (EDTM) conference. It will be held March 12-15, 2019, at the iconic Marina Bay Sands Convention Centre in Singapore.

Launched in 2017 and sponsored by the IEEE Electron Devices Society (EDS), EDTM is rapidly becoming a premier conference for the electron devices community. EDTM provides a unique forum for discussion of a broad range of device-related topics including materials, processes, devices, packaging, modeling, reliability, manufacturing, and yield. The conference location rotates among countries in Asia, coming to Singapore for the first time in 2019.

EDTM 19 conference will kick off on the first day with 4 tutorial sessions and 4 short courses. The 4 tutorial sessions cover topics ranging from front-end CMOS process to back-end-of-line, packaging and nonvolatile memory technology. These tutorials sessions are catered towards students and young engineers in the industry and are intended to give a comprehensive overview of the domain presenting a roadmap of the evolution of the technology over the past two decades. For the 4 short courses lined up for you, they cover the latest advancements in niche application areas of interest, which include hardware security, sensors for IoT, flexible and wearable electronics as well as heterogeneous integration of different device technologies. The short courses are aimed at educating our attendees with the latest ongoing applied research in these four areas that will pave way for the successful realization of internet of everything (IoE), Industry 4.0 and an Al-driven economy.

We are also pleased to announce that the Technical Program Committee has prepared an outstanding technical program. There will be 3 Plenary Talks by distinguished speakers from the industry and academia covering exciting topics in "Differentiated Foundry Solutions for a Connected Future", "Technologies Toward Three-Dimensional Brain-Mimicking IC Architecture" and "Enabling manufacturing of sub-10 nm generations of integrated circuits with EUV lithography." The 3 days technical program will include a total of 112 regular and invited oral presentations organized into several parallel sessions and 60 poster presentation sessions. On top of all these, as a tradition of EDTM, the conference will also include a Women In Engineering (WIE) event to celebrate the contributions of women in the field of electron devices and manufacturing.

http://ewh.ieee.org/conf/edtm/2019 /index.html

On behalf of the organizing and international committees, we look forward to seeing you at the 2019 EDTM in Singapore, where the excitements and hospitalities await you!

Geok Ing Ng General Co-chair of EDTM 2019 Nanyang Technological University

MK Radhakrishnan General Co-Chair of EDTM 2019 NanoRel Technical Consultants

# THE IEEE APP: Your mobile gateway to IEEE. BIEFE **Download** now and get IEEE at your fingertips. App Store **IEEE**

# 2019 IEEE INTERNATIONAL MEMORY WORKSHOP (IMW)

The 11th International Memory Workshop (IMW) will be held at the Hyatt Hotel in Monterey, California, USA, from May 12-15, 2019. The history of the IMW dates back to the NVSMW (Nonvolatile Semiconductor Memory Workshop) which began in 1976 and which later merged with the ICMTD (International Conference on Memory Technology and Design) to become the IMW. The IMW is sponsored by the IEEE Electron Devices Society and meets annually in May. The workshop covers all types of memory technology, is focused on advancing innovation in memory technology, and is organized in a way that provides excellent professional development and networking opportunities for attendees.

The IMW is the premier international forum for both new and seasoned technologists having diverse technical backgrounds to share and learn about the latest developments in memory technology with the global community. The scope of workshop content ranges from new memory concepts in early research to the technology drivers currently in volume production as well as emerging technologies in development. Topics include new device concepts, technology advancements, scaling and integration, circuit design and reliability, as well as emerging applications. Consistent with the increased importance of memory system architecture and integration, the workshop also includes increasing coverage of the systems in which memories are deployed and the co-evolution of memory technology along with memory systems and applications.

The IMW is the preeminent forum covering the latest developments, innovations, and evolving trends in the memory industry. Typical workshop attendance exceeds 250 attendees (350 last year) and the technical program begins with a full day short course given by distinguished experts that provides an excellent professional de-

velopment opportunity for both new and experienced technologists. The single-track technical program spans three days and also includes an evening poster session for informal technical discussion with authors as well as a panel discussion where experts discuss and debate a current hot topic. The 2018 workshop included invited talks from industry and research leaders from Toshiba, Micron, NXP, FMC, LETI, SONY, Applied Materials, Avalanche and Panasonic. Highlights included experts sharing their insights and perspectives on a variety of topics including the 3D NAND scaling horizon, scaling challenges of embedded memories, opportunities for emeraing memories and innovation (PCM, RRAM, MRAM, FeRAM...) for storage class memories, data centric architectures, tremendous growth of connected objects, and neuromorphic circuits. The technical program is organized to maximize networking opportunities and facilitate open information exchange among workshop contributors, committee members, and attendees. The program schedule includes ample time dedicated to social events including provided refreshment breaks, a workshop luncheon, and an evening banquet.

On behalf of the organizing committee, I cordially invite you to participate in the 2019 IMW to continue to participate in the advancement of innovation in the rapidly evolving memory industry. For additional information, including the call for papers, key dates, abstract submission instructions, registration information, and technical program details, please visit the IMW website for the latest updates: http://www.ewh.ieee.org/soc/eds/imw/. I look forward to seeing you in Monterey this May.

Gabriel Molas CEA Leti 2019 IMW Publicity Chair

# SOCIETY NEWS

# Message from EDS President

Dear EDS Colleagues:

Fernando Guarin EDS President (2018-2019)

As we are ending 2018, I would like to take this opportunity to thank our many volunteers that are the lifeblood that energizes our society. It was my distinct honor

and privilege to have served as the Electrons Devices Society as your 2018 President. I would like to share with you the many accomplishments and challenges;

We have completed the definition stage of our future strategy, with a very clear objective "To collaborate, network, and be the center of excellence in electron device technology." I would like to express our sincere gratitude to the Past President Samar Saha and the members of his strategy committee, for their leadership in the definition and outline of our future strategy. Now we move to the next phase to set up the infrastructure to implement and monitor our progress on this important endeavor.

In the publications arena, under the leadership of outgoing chair Hisayo Momose, the submission to publication time of EDS journals maintained a best in class record pace, TED submission stands at 13.1 Weeks, EDL is still the fastest in IEEE with 4 weeks. JEDS continues to solidify our leadership position in Open Access. I would like to thank our outgoing EDL EiC Tsu-Jae King Liu and welcome Jesus del Alamo to this key role.

Our conference portfolio remains very strong and we continue to look for new opportunities. The EDTM2018 with 100% EDS ownership was a success and is emerging as an EDS flagship conference in Asia; EDTM2019 is on track in Singapore.

We continue to maintain very close collaborations with EDS conferences: PVSC, IEDM, EDTM, IRPS, ISPSD, IVEC, VLSI, IFETC, etc., and continue to sponsor Special Issues based on best conference papers and highly relevant topics for TED and JEDS.

Our membership continues to be close to 10K as of November we showed a decreased of 2.7% while our student membership was up by 1.2%. For 2018 EDS Celebrated Member honoree Martin Green was announced at the June World Conference on Photovoltaic Energy Conversion (WCPEC-7). The June BoG meeting was held in Cartagena de Indias, Colombia, where the EDS C&B changes were approved and subsequently accepted by IEEE. They have now been updated on our website. The EDS education activities best practices presentation at TAB led to formation of a TAB ad hoc committee to use across IEEE.

The first draft of new social media platform (Facebook, LinkedIn, Twitter and IEEE Collabratec) was successfully rolled out at the YP/WIE breakfast networking event prior to the IEDM 2018 plenary session. I invite you to join us and participate at:

Facebook https://www.facebook .com/IEEE-Electron-Devices-Society-1581398582006248

**LinkedIn** https://www.linkedin.com/ company/edsglobal

Twitter https://twitter.com/IEEEEDS Our EDS web site is currently undergoing redesign for Desktop version: https://invis.io/FJO2G98EBC6 and Mobile version: https://invis.io/ PJOSFIG6CVA

I would like to extend our sincere gratitude for the efforts of many dedicated volunteers that have positioned EDS on solid ground in the technical and financial areas. As a volunteer-led, volunteer-driven organization, we rely on the dedication of individuals like you who share their time, talent, and energy to help make EDS the premier global society devoted to advancing the field of electron devices for the benefit of humanity. I invite you to become an engaged member of our Society, and play a vital role as we shape the future of our society.

> Fernando Guarin **EDS President**

# REPORT ON THE EDS BOARD OF GOVERNORS MEETING IN SAN FRANCISCO, USA

Jacobus W. Swart EDS Secretary

The EDS BoG Meeting was held in San Francisco, USA, on December 2nd, before the IEDM 2018 conference, and following the EDS ExCom and technical committees meetings the day

before. There were enough members present to form the needed quorum defined by the Constitution and Bylaws. The picture shows the meeting room during EDS President, Fernando Guarin's overview talk at the beginning of the meeting. After the welcome words by the president, many reports were presented and motions discussed and approved.

EDS President Fernando Guarin began his speech with the moto "... building EDS on the foundation of the past to meet the challenges of the future." He highlighted the following achievements:

- T-ED continues an IEEE-best journal, with submission-online and a 13 weeks cycle time. The submission-to-publish journals maintained a record of 4 weeks for EDL. Two new editors were selected for T-ED and EDL, respectively Giovanni Ghione and Jesus del Alamo. The impact factors off the three 100% EDS journals (T-ED, EDL and J-EDS) are all close to 3.0.

- The conference EDTM held in Tokyo is a huge success as an EDS flagship conference in Asia. EDTM 2019 is on track to be held in Singapore. A new EDS conference, called LAEDC, will start in 2019 in Region 9. The first edition will be held in Colombia in February, in conjunction to the conference LASCAS sponsored by CAS.

- The changes voted on during the previous BoG meeting were all

- approved by IEEE and are already updated on the EDS webpage.

- The first versions of a new social media platforms (Facebook, Linkedln, Twitter and IEEE Collabratec) were created and launched at the IEDM 2018 opening as an initiative by the EDS Young Professionals and WIE committees:

- Facebook: https://www .facebook.com/IEEE-Electron-Devices-Society-1581398582006248/;

- LinkedIn: https://www .linkedin.com/company/ edsglobal/;

- Twitter: https://twitter.com/ IEEEEDS

- The EDS website is currently undergoing a redesign:

- Desktop: https://invis.io/ FJO2G98EBC6

- Mobile: https://invis.io/ PJOSFIG6CVA

- EDS financials remain healthy, with a small loss in 2017 and positive numbers for 2018, with revenues and expenses of approximately 6.7 million dollars.

- The EDS Mission Fund has been established to support EDS mission-driven humanitarian, educational, and research initiatives. The current mission fund has a budget of US\$129,000 and can support new proposals.

- The total number of EDS members remains over 10,000 with a slight decrease of higher grade and increase of student members in 2018. A campaign to increase memberships will continue an important effort.

- The number of EDS chapters continues to increase slightly every year, with a total of 211 chapters worldwide in 2018.

- Educational activities included a series of 6 webinars during 2018, among other initiatives, like

- EDS-ETC program, online international college student competition and others.

- The Strategy Plan for the next five years has been outlined, and its implementation will start in 2019. An Ad Hoc committee is being formed to track progress and to make adjustments when applicable.

After the presentation by the president, many other VP's and chairs presented their updates, new ideas and additional details to the broader overview described.

EDS President-Elect, Meyya Meyyappan, proposed the idea of offering an EDS Summer School. This could be one per year, with preference on a topic not regularly taught at EE courses. A motion was approved about the idea of offering a summer school starting in 2020. The budget will be discussed in future BoG meeting.

M.K. Radhakrishnan, EDS VP of Regions & Chapters, reported that out of the 211 chapters, 69 of the chapters are student chapters, 3 of which started in 2018. The total of subsidies amounted US\$47,500.00 in 2018. A total of 14 Mini-Colloquia (MQ) were supported by EDS with a total amount of US\$51,030.00. The number of Distinguished Lectures delivered (not including MQ) was 132, with total support of US\$61,500.00. A motion was approved about updated EDS Regions & Chapters charter.

Bin Zhao reported in name of Ru Huang, EDS VP of Membership and Services, about membership development and recruiting campaigns. Besides the statistics presented, IEEE OU Analytics, a new visual business intelligence tool was announced, already available in vTools, for designated volunteer officers to access membership data: https://tblanalytics.ieee.org.

Ravi Todi, VP of Technical Committees and Meetings, reported about the over 100 conferences sponsored/

EDS Board of Governors meeting during the general overview speech by EDS President Fernando Guarin

co-sponsored by EDS and about the different technical committees. Some of the highlights were about the close collaborations between EDS conferences, the special issues produced for TED and JEDS, the active committees and volunteer participation with a balanced committee membership. The most prominent conferences were also described and discussed.

The treasurer report was presented by VP Subu Iyer. Healthy budgeted details were presented and discussed. Through a motion the budget for 2019 was approved, with a total expenses of US\$6,695,000.00.

Hisayo Momose, Interim VP of Publications & Products reported on EDL, TED, JEDS and other co-sponsored publications. Noticeable are the acceptance rates of the EDS publications: 19.8, 28,2 and 44.0% for EDL, TED and JEDS respectively. Also the time between submission and publication are very good, respectively 4.0, 13.1 and 10.6 weeks. Discussion started on the proposal of a new publication, the Flexible Electronics Journal.

The last item on the agenda was the election of new BoG members. Among the 22 BoG members, 7 ended their 3-year term. Among these, 2 were reelected (one reelection term is allowed in one's lifetime) and 5 new names were elected.

> Jacobus W. Swart EDS Secretary State University of Campinas Brazil

# ARE YOU TRYING TO GROW YOUR CHAPTER MEMBERSHIP?

APPLICATIONS NOW ACCEPTED FOR THE 2019 EDS MEMBERSHIP FEE SUBSIDY PROGRAM!

Our society continually works to increase the value of EDS membership and our colleagues enjoy an incredible array of members-only benefits. One EDS initiative to encourage newcomers and assist EDS chapters stay strong and vibrant, is the EDS Membership Fee Subsidy Program (MFSP). This program offers the generous incentive of one-year complimentary IEEE and EDS memberships (sponsored by EDS), to help launch new chapters or enable existing ones, in low-income geographical areas to grow their memberships.

This special offer is available to students currently enrolled in an accredited course of study, and to those professionals who qualify for reduced IEEE membership fees (i.e., unemployed, retired, or meet a minimum income threshold).

The EDS Membership Fee Subsidy Program policy is as follows:

EDS will cover the cost of IEEE and EDS membership for up to 15 applicants per chapter. Please note that this is a onetime benefit, per applicant. Past recipients of the EDS member-

- ship fee subsidy benefit do not qualify

- Five of the fifteen members each year must be new IEEE members

- Applicants must apply through a local EDS chapter

- Current elected officials on record, of eligible EDS chapters will be emailed instructions

- Each applicant must indicate in their IEEE account prior to applying for EDS Membership Fee Subsidies that they qualify for reduced IEEE membership fees.

EDS has chapters around the world that organize events to benefit your professional development

For a complete list of special circumstances eligible for reduced IEEE membership fees: https://www.ieee .org/membership/special-circumstances.html.

If you wish to apply for IEEE membership and not eligible for the

EDS Membership Fee Subsidy, we encourage you to try the IEEE Electronic Membership option, which is open to new and renewing members who reside in countries where the per capita Gross National Income (GNI) is US\$15,000 or less. Please visit the IEEE website for more details on IEEE Electronic Membership, at https://www.ieee.org/membership/join/emember-countries.html

Chapter Chairs: To submit your chapter's list of applicants for the 2019 EDS Membership Fee Subsidy, please contact Joyce Lombardini (j.lombardini@ieee.org), in the EDS Executive Office.

There are other EDS membership recruitment campaigns scheduled for 2019 and Joyce can provide information upon request.

# EDS MEMBERS RECENTLY ELECTED TO IEEE SENIOR MEMBER GRADE

Rosminazuin Ab Rahim Laurie Calvet Yuri Chaplygin Wanzhao Cui Gerard Cummins Peng Fang Brad Hoff Balaji Jayaraman Sourabh Khandelwal Daisuke Kobayashi Rosa Letizia

Sylvain Marsillac

Nelidya Md. Yusoff

Abdul Rahman Mohmad

Arash Salemi

Juan Sanchez

Ioannis Savidis

Mustafa Yelten

Shinji Yuasa

Vimala Palanichamy

Ashraful Bhuiyan

Lining Zhang

Azrul Hamzah

Maizatul Zolkapli

Mohamad Radzi Ahmad Yoshitaka Kurosaka Wen-Sheng Zhao Chuanxin Lian Michael Kane Joseph Bardin Euisik Yoon K. Michael Han Cormac O'Connell Jonas Jonsson Lionel Trojman

If you have been in professional practice for 10 years, you may be eligible for Senior Membership, the highest grade of membership for which an individual can apply. New senior members receive a wood and bronze plaque and a credit certificate for up to US\$25 for a new IEEE society membership. Upon request, a letter can be sent to employers recognizing this new status. For

more information on senior member status, visit: http://www.ieee.org/membership\_services/membership/senior/index.html

To apply for senior member status, fill out the online application after signing in with your IEEE account: https://www.ieee.org/membership\_services/membership/senior/application/index.html.

# IN MEMORY-DENNIS D. BUSS (1942-2018)

Dennis Buss, a pioneer of HgCdTe monolithic infrared focal plane technology and corporate technology leader, passed away while on a birdwatching vacation with his wife, Alenya Buss, in rural Ecuador.

Dennis Buss received his BS, MS and PhD in Electrical Engineering from MIT in 1963, 1965 and 1968, respectively. In 1969, he began a distinguished industrial career joining the Central Research Laboratories of Texas Instruments. His early research dealt with narrow-gap semiconductors, PbTe and HgCdTe, and the development of charge-coupled devices for analog signal processing, digital memory and IR imaging. In 1978, he became a TI Fellow and in 1980 he was named Vice President and Director of TI's Semiconductor Process and Design Center. Between 1987 and 1997, Dennis was VP of Technology at Analog Devices. He returned to TI in 1997 as VP of SiTechnology Development and in 2007, he became TI Chief Scientist. In 2010, Dennis retired from TI but remained as consultant to TI. He served twice on the Electrical Engineering faculty at MIT in 1968-1969 and 1974-1975.

Along the way, Dennis received numerous technical awards. He was elected IEEE Fellow in 1985 "for leadership in VLSI technology research and development." He received the 1985 IEEE Herschel Award and in 1997, together with Richard Chapman and Michael Kinch, the IEEE Jack A. Morton Award "for the demonstration and development of mercury cadmium telluride monolithically-integrated

charge-coupled device focal plane arrays." In 2000, he was selected by the IEEE Electron Devices Society for the IEEEThird Millennium Medal.

Dennis' extraordinary technical accomplishments have also been recognized through his numerous keynote, plenary and invited talks at major international conferences, such as the 2000 IEEE Emerging Technologies Symposium, 2001 IEEE International Conference on Electronics, Circuits and Systems, 2002 IEEE International Solid-State Circuits Conference, 2005 International Symposium on Low Power Electronics and Design, 2007 IEEE International Symposium on Circuits and Systems, and 2011 IEEE International Electron Devices Meeting, to name just a few. He published numerous invited papers and was Guest Editor of special issues in IEEE publications. His witty and effusive personality and his deep knowledge and experience made him a frequent leader for panel discussions at major conferences, such as ISSCC 1975 and IEDM 1979.

Starting in 2007, Dennis became Visiting Scientist at MIT's Microsystems Technology Laboratories with responsibility for managing joint research programs between TI and MIT. In this capacity, he assembled a rich research portfolio in areas as diverse as secure ID tags, magnetic field sensors, speech recognition, machine learning, gallium nitride transistor reliability, and power management systems. He served as co-advisor in several master's and PhD theses. He instituted the TI Fellowship for Women in Microelectronics in the Department of Electrical Engineering and Computer Science.

Dennis had a passion for history, nature, and mountaineering, as well as an enduring sense of adventure. He was most proud of his climb of McKinley (6,190 m) in 1986 and Aconcagua (6,961 m) in 2000.

Those of us that have had the good fortune of knowing Dennis for some time had come to appreciate his ebullient personality, his deep technological insights, and his vast perspective about microelectronics and electrical engineering education. Most of all, throughout the years, Dennis was an approachable colleague generous in sharing his wisdom through kind and constructive advice.

Jesús A. del Alamo Massachusetts Institute of Technology

# AWARDS AND CALL FOR NOMINATIONS

# EDS MEMBERS NAMED RECIPIENTS OF 2019 IEEE TECHNICAL FIELD AWARDS

Two EDS Members were among the recipients of the 2019 IEEE Technical Field Awards:

### 2019 IEEE Cledo Brunetti Award

Daniel C. Edelstein of IBM, Yorktown Heights, NewYork, has been named co-recipient of the 2019 IEEE Cledo Brunetti Award. The citation states,

"For contributions to manufacturable, reliable, and scalable Cu interconnect and low-k dielectric technology for CMOS".

The combined efforts of Daniel C. Edelstein, Alfred Grill, and C-K Hu in making the benefits of copper (Cu) interconnect technologies a feasible reality forever changed semiconductor manufacturing and allowed the continued scaling of microelectronics. Their pioneering work overcame the manufacturing and reliability challenges of introducing a new material process to replace aluminum interconnect. Edelstein described a qualified and commercial Cu interconnect technology. His dual damascene structure vielded unique microstructures in electroplated Cu nanowires, making it possible to study effects of nanoscale surfaces and interfaces on electron resistivity and mass transport in Cu lines. Grill's development of siliconcarbon-oxygen-hydrogen (SiCOH) dielectrics provided a unique class of low-k dielectrics with strong chemical bonds, offering a distinct molecular structure that strengthened the thermomechanical properties of porous low-k materials. Hu's work on electromigration of Cu interconnects provided insights to understanding the basic scaling law for predicting the degradation of electromigration lifetime and development of new materials for future technology nodes.

An IEEE Senior Member, Edelstein is an IBM Fellow at the IBM T.J. Watson Research Center, Yorktown Heights, NY, USA. Grill is an IBM Fellow Emeritus at the IBM T.J. Watson Research Center, Yorktown Heights, NY, USA. Hu is a research staff member at the IBM T.J. Watson Research Center, Yorktown Heights, NY, USA.

# 2019 IEEE Andrew S. Grove Award

Digh Hisamoto of Central Research Laboratory, Hitachi, Ltd., Tokyo, Japan, has been named the recipient of the 2019 IEEE Andrew S. Grove Award.

The citation states, "For pioneering work in the manufacturing of three-dimensional double-gate MOSFET devices."

Without Digh Hisamoto's development of the three-dimensional (3D) double-gate metal-oxide-silicon field effect transistor (MOSFET) in 1989, many of today's advanced logic products likely would not exist. With conventional planar MOS-FET scaling becoming more difficult due to challenges including shortchannel effects, Hisamoto's DELTA 3D MOSFET was instrumental in allowing miniaturization to continue. He was the first to recognize that it was possible to solve process issues if the channel was formed in vertical "fin" surfaces. His 3D MOSFET featured strong immunity to shortchannel effects, high mobility, and reduced threshold voltage variation. Important to its realization, he demonstrated that his double-gate structure could be fabricated using a conventional self-aligned silicon process. Today's FinFET advanced logic technologies exhibit most of the principal operating concepts introduced by Hisamoto's thin-body vertical-channel FET work.

An IEEE Fellow, Hisamoto is senior chief researcher, Hitachi, Ltd., Tokyo, Japan.

Samar Saha EDS Awards Chair Prospicient Devices Milpitas, CA, USA

# ANNOUNCEMENT OF THE 2018 EDS PHD STUDENT FELLOWSHIP WINNERS

Carmen M. Lilley EDS Student Fellowship Committee Chair

The Electron Devices Society PhD Student Fellowship Program was designed to promote, recognize, and support PhD level study and research within the Electron Devices Society's field of interest.

EDS proudly announces three EDS PhD Student Fellowship winners for 2018: Chen Jiang - University of Cambridge, England; Junkai Jiang, University of California, USA; Yuanyuan Shi, Rovira I Virgili University, Spain. Brief biographies of the recipients appear below. Detailed articles about each PhD Student Fellowship winner and their work will appear in forthcoming issues of the EDS Newsletter.

Chen Jiang received the B.S. degree in engineering from Shanghai Jiao Tong University, China, in 2014. Since then, he has been pursuing his

Ph.D. degree in engineering at the University of Cambridge, UK, and has worked on exploring novel electronic devices for low-power, lowcost electronics, encompassing device fabrication, and device physics

and modeling. His research interests include novel electronic device architectures, printable large-area electronics, and low-power high-gain amplifiers for wearable sensor interface circuits and systems. He was a recipient of the Cambridge International Scholarship Scheme and the China Scholarship Council Scholarship, and was also the winner of the Cambridge Society for the Application of Research Award 2018.

Junkai Jiang joined UCSB as a MS/PhD student under the supervision of Prof. Kaustav Banerjee, upon completing his BS degree in microelectronics

from Peking University, Beijing, China. Mr. Jiang's research is focused on modeling, design and characterization of interconnect materials/structures and monolithic-3D integration based on graphene and beyond-graphene two-dimensional materials. His doctoral work spanned fundamental materials modeling, compact modeling, device/circuit design and finally experimental demonstration of applications uniquely enabled by these materials. His research contributions have appeared in leading IEEE conferences and journals, including IEDM, IRPS, S3S and IEEE T-ED, as well as in Nature Electronics and Nano Letters.

Yuanyuan Shi is currently pursuing her PhD degree in Nanoscience at Rovira i Virgili University, under the supervision of Prof. Mario Lanza.

She worked 12 months at Stanford University (H.-S. Philip Wong's group) on 2D materials based electronic synapses for neuromorphic applications, and her results were published in Nature Electronics and IEDM 2017. Yuanyuan has published 38 articles, one book chapter, and two international patents (one of them received 1 M\$ investment). She has attended 12 international conferences, and in 6 of them gave an oral presentation. She is a student member of IEEE, EDS, and RSC, and she serves as an active reviewer for several international journals, such as Scientific Reports, Thin Solid Films and ChemElectroChem.

Carmen M. Lilley EDS Student Fellowship Committee Chair University of Illinois at Chicago Department of Mechanical Engineering Chicago, IL, USA

# CALL FOR NOMINATIONS—EDS NEWSLETTER REGIONAL EDITOR

The society currently has opportunities available to join the EDS Newsletter editorial board. This position requires only a few volunteer hours on a quarterly basis, but plays a vital society communication role.

We would appreciate if this volunteer opportunity was promoted at your next chapter meeting. Please send nominations or self-nominations to j.lombardini@ ieee.org.

# ANNOUNCEMENT OF THE 2018 EDS MASTERS STUDENT FELLOWSHIP WINNERS

Carmen M. Lilley EDS Student Fellowship Committee Chair

The Electron Devices Society Masters Student Fellowship Program was designed to promote, recognize, and support Masters level study and research within the Electron Devices Society's field of interest.

EDS proudly announces the winners of the 2018 EDS Masters Student Fellowship.

Neel Chatterjee is currently pursuing a Master's in Electrical Engineering at University of Minnesota working with Profes-

sor P. Paul Ruden and Professor Sarah Swisher on numerical modelling and simulation of charge transport in inorganic thin film transistors. He has also worked on fabricating self-assembly structures for biomedical applications under the guidance of Professor Jeong-Hyun Cho. Neel did his undergraduate in Electronics and Communication engineering from Amity University where he worked on design and simulation of nanowire field effect transistors with Professor Sujata Pandey and published papers in IEEE conferences like IEEETENCON and INDICON. His current research interests also include solution processed dielectrics and DFT calculations of 2D materials heterostructures.

Yu-Chieh Chien received his B.S. degree in materials and optoelectronic science at National Sun Yat-Sen University, Taiwan, in

2018, where he is currently pursuing the M.S. degree, supervised by Prof. Ting-Chang Chang and Prof. Tsung-Ming Tsai. His research interests include oxide TFTs, flexible electronics, and GaN HEMT. His current research focuses on optimizing the reliability and developing the potential application in oxide TFTs. Yu-Chieh Chien has proposed degradation mechanisms for oxideTFTs under moist environment to improve stability of the devices. In addition, he has demonstrated an ultra-high sensitivity UV sensor based on oxide TFTs. To date, he has authored 4 articles to peer-review journals and 2 to international conferences.

Carmen M. Lilley

EDS Student Fellowship

Committee Chair

University of Illinois at Chicago

Department of Mechanical Engineering

Chicago, IL, USA

# CALL FOR NOMINATIONS— IEEE FELLOW CLASS OF 2020

IEEE Fellow is a distinction reserved for select IEEE members. The honor is conferred by the Board of Directors upon a person with an extraordinary record of accomplishments in any of the IEEE fields of interest.

If you know of an IEEE colleague who is a Senior Member or Life Senior Member in good standing, has completed five full years of service in any grade of IEEE Membership and who has made an outstanding

contribution to the electronic or electrical engineering profession in any of the IEEE fields of interest, you can nominate this person in one of four categories: Application Engineer/Practitioner, Educator, Research Engineer/Scientist or Technical Leader.

Nominations for the Fellow Class of 2020 are now being accepted.

To learn more about the Fellow program and the application process, visit the Fellow Web Site at http://www.ieee.org/fellows where you can also find three important Fellow Guides that can help you write an effective nomination. There are some novelties in the nomination process and a summary of them can be found in The Institute article "It's Now Easier to Nominate a Potential Fellow"

The deadline for nominations is March 1, 2019.

# 2019 PhD Student Fellowship

**Description:** One year fellowships will be awarded to promote, recognize, and support PhD level study and research within the Electron Devices Society's field of interest. The field of interest for EDS is all aspects of engineering, physics, theory, experiment and simulation of electron and ion devices involving insulators, metals, organic materials, plasmas, semiconductors, quantum-effect materials, vacuum, and emerging materials. Specific applications of these devices include bioelectronics, biomedical, computation, communications, displays, electro and micro mechanics, imaging, micro actuators, optical, photovoltaics, power, sensors and signal processing.

Three fellowships are expected to be awarded to eligible students in each of the following geographical regions for 2018: Americas. Europe/Middle East/Africa, and Asia & Pacific. Only one candidate can win per educational institution.

**Prize:** US\$5,000 to the student and if necessary funds are also available to assist in covering travel and accommodation costs for each recipient to attend the EDS Governance meeting in December 2019 for presentation of the award plaque. The EDS Newsletter will feature articles about the FDS PhD Fellows and their work over the course of the next vear.