JULY 2015 VOL. 22, NO. 3 ISSN: 1074 1879

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

#### TABLE OF CONTENTS

| TECHNICAL BRIEFS1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>Reliability Trends of Nano-scaled CMOS Devices</li> <li>Report on 2015 IEEE International Reliability<br/>Physics Symposium</li> </ul>                                                                                                                                                                                                                                                                                                                                                         |

| Wide Bandgap Semiconductors, They're Special                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| UPCOMING TECHNICAL MEETINGS                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Symposium (CSICS)  • 2015 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM)                                                                                                                                                                                                                                                                                                                                                                                                                    |

| SOCIETY NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| EDS Vision and Mission Statements     EDS President's Message     Message from EDS Vice President of Regions/<br>Chapters                                                                                                                                                                                                                                                                                                                                                                               |

| Message from Newsletter Editor-in-Chief     EDS Governance Meeting Summary     Call for EDS Board of Governors Nominations     EDS Board of Governors Election Process     IEEE Election Reminder     EDS Compound Semiconductor Devices and                                                                                                                                                                                                                                                            |

| EDS Compound Semiconductor Devices and Circuits Technical Committee Report     2015 William R. Cherry Award Winner     42nd Photovoltaic Specialists Conference (PVSC) Young Professional Award     Congratulations to the EDS Members Recently Elected to IEEE Senior Member Grade     Enhance Your Career with IEEE Senior Membership     EDS Guidelines for Distinguished Lectures and Mini-Colloquia Programs     EDS Chapter Subsidies for 2016     IEEE Bring Your Daughters and Sons to Work Day |

| 2015 EDS Award Winners and 2016 Call for<br>Nominations                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| YOUNG PROFESSIONALS29                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| <ul> <li>Reflections from EDS Young Professionals</li> <li>IEEE Young Professionals—An Exciting New Rebranded Outlook</li> <li>Register Now for Upcoming EDS Webinars!</li> <li>New Webinars Available in the Archive</li> <li>EDS-ETC Report</li> </ul>                                                                                                                                                                                                                                                |

| CHAPTER NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| WIMNACT 45—IEEE EDS Mini-Colloquium— Yokohama WIMNACT 46—IEEE EDS Mini-Colloquium— Shenzhen                                                                                                                                                                                                                                                                                                                                                                                                             |

| • IEEE ED NIST Student Chapter's 4th Mini-Colloquium                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

# **IEEE**

#### TECHNICAL BRIEFS

## RELIABILITY TRENDS OF NANO-SCALED CMOS DEVICES

GUIDO GROESENEKEN

IMEC AND KU LEUVEN, BELGIUM

With the continuous downscaling of CMOS technologies, reliability is more and more becoming a major bottleneck and this for several reasons. First of all the electric fields and current and power densities have increased continuously and are now reaching the maximum values that can be allowed for reliable operation. At the same time an impressive effort is taking place introducing new materials and novel device architectures to maintain the effective performance scaling. New materials like high k dielectrics and metal gates for both logic and memory technologies and novel device concepts such as Multiple gate FET's have already been introduced, while Ge or III-V materials for high mobility devices are under investigation. These new materials and devices often have unknown reliability behavior and/or introduce new failure mechanisms, whereas their speed of introduction exceeds the capabilities to explore their reliability performance in great detail. Finally, the market is continuously demanding higher reliability levels, with single digit failure rates in FIT units (1 FIT = 1 failure per 109 operating device hours) for present technologies. In the past, the technological reliability margins that were available to achieve the required failure rate levels were always sufficiently high, but in some of the technologies under development this becomes more and more cumbersome. In this technical note we review the evolution of reliability for nanoscaled technologies, and we show that for some failure mechanisms the lifetime can no longer be guaranteed. As a result alternative ways of reliability assurance will become necessary.

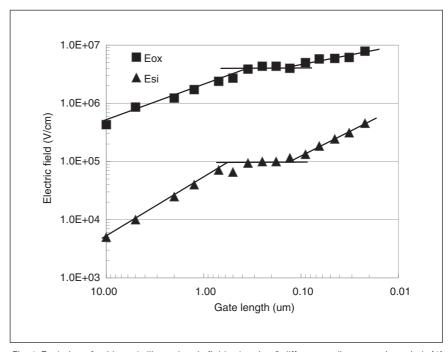

As an example of the trends in the electric fields existing in the transistors under operating conditions, Fig. 1 shows the evolution over the past 40 years of the oxide and silicon fields as a function of the gate length [1].

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

#### **ELECTRON DEVICES** SOCIETY

#### President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### President-Elect

Samar Saha Ultrasolar Technology E-mail: samar@ieee.org

#### Treasurer

Ravi M. Todi Qualcomm Technologies, Inc. E-mail: rtodi@ieee.org

#### Secretary

Fernando Guarin IBM Microelectronics E-mail: guarinf@us.ibm.com

#### Jr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

#### Sr. Past President

Renuka P. Jindal University of Louisiana at Lafavette E-mail: r.jindal@ieee.org

#### Vice President of Membership and Services

Mikael Ostling

KTH, Royal Institute of Technology E-mail: mostling@kth.se

#### Vice President of Publications and Products

Bin Zhao Fairchild Semiconductor E-mail: bin.zhao@ieee.org

#### Vice-President of Regions/

Chapters Xing Zhou

Nanyang Technological University E-mail: exzhou@ntu.edu.sg

#### Vice President of Technical **Committees & Meetings**

Leda Lunardi North Carolina State University E-mail: leda\_lunardi@ncsu.edu

#### **IEEE Newsletters**

Theresa Smith **IEEE Operations Center** E-mail: tlsmith@ieee.org

#### **Executive Director**

Christopher Jannuzzi **IEEE Operations Center** E-mail: c.jannuzzi@ieee.org

#### Membership Administrator

Joyce Lombardini IEÉE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html

#### **EDS Board of Governors (BoG) Elected Members-at-Large**

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| <u>2015</u>                                                                              | TERM                                          | 2016                                                                                             | Term                                          | 2017                                                                                                    | TERM                                                 |

|------------------------------------------------------------------------------------------|-----------------------------------------------|--------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|

| D. Camacho<br>S. S. Iyer<br>M. Meyyappan<br>A. Nathan<br>M. Shur<br>D. Verret<br>B. Zhao | (1)<br>(2)<br>(2)<br>(2)<br>(2)<br>(1)<br>(2) | A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) | Z. Celik-Butler<br>S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose<br>T.L. Ren | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) |

#### NEWSLETTER **EDITORIAL STAFF**

#### **Editor-In-Chief**

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

#### REGIONS 1-6, 7 & 9

#### Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq IBM Systems and Technology E-mail: farooqm@us.ibm.com

#### Central USA & Canada (Regions 4 & 7)

Karim S. Karim University of Waterloo E-mail: kkarim@uwaterloo.ca

#### Southwestern & Western USA (Regions 5 & 6)

Adam M. Conway Lawrence Livermore Nat. Lab. E-mail: conway8@llnl.gov

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

#### **REGION 8**

#### **Eastern Europe**

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### **UK, Middle East & Africa**

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

#### REGION 10

#### Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.mv

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech. ac.jp

#### **East Asia**

Mansun J. Chan Hong Kong Univ. of Sc. & Tech. E-mail: mchan@ust.hk

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editorin-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

#### Newsletter Deadlines

| <u>Issue</u> | DUE DATE    |

|--------------|-------------|

| January      | October 1st |

| April        | January 1st |

| July         | April 1st   |

| October      | July 1st    |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

IEEE Electron Devices Society Newsletter (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright @ 2015 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

**FPO**

#### RELIABILITY TRENDS OF NANO-SCALED CMOS DEVICES

(continued from page 1)

Clearly 3 periods can be distinguished: a first constant voltage scaling period in the seventies and eighties, in which the power supply voltage was not reduced when scaling the geometries, and consequently the fields increased continuously with scaling. This was followed by a more or less constant field scaling period, in which the power supply voltages were reduced with every new technology node, so that the fields saturated at a certain plateau. Since the 65 nm node, however, the power supply voltages are saturating at a level around 1 V, and can no further be reduced because of the non-scaling sub-threshold slopes of the MOS-FET's. As a result we observe again a further increase in the electric fields, which starts to put new constraints on the reliability of the devices. Moreover, the power density has also continuously increased, which leads to higher chip temperatures, and consequently even a stronger acceleration of the degradation mechanisms. All of this leads to a strong reduction of the reliability margins for most failure mechanisms.

Until now, reliability assessment and assurance was mainly carried out at the technology level, through accelerated testing for each major failure mechanism. Accelerated test methodologies and models have been developed and are available for most failure mechanisms such as hot carrier degradation, Time-Dependent Dielectric Breakdown, Bias-Temperature Instability (BTI)], electromigration, stress voiding, interconnect dielectric instability and breakdown.

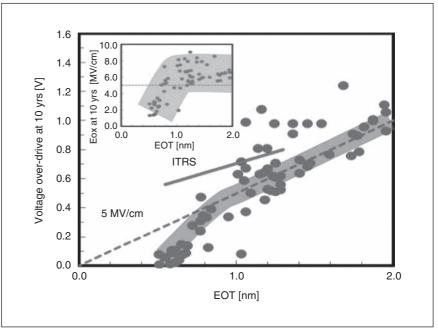

Due to the trends discussed above, however, reliability margins of these failure mechanisms are reduced, in some cases even to zero. As an example, Figure 2 shows the 10 year over-drive voltage to be decreasing with reducing EOT [2].

Fig. 1. Evolution of oxide and silicon electric fields showing 3 different scaling scenario periods [1]

Fig. 2. Evolution of p-MOSFET NBTI over-drive voltage at 10 years. ITRS roadmap data is also added. [2]

This figure shows that the extrapolated gate overdrive at 10 year is linearly dependent on EOT. The expected NBTI overdrive versus EOT is shown by the dotted iso-electric field line of 5 MV/cm. However, it

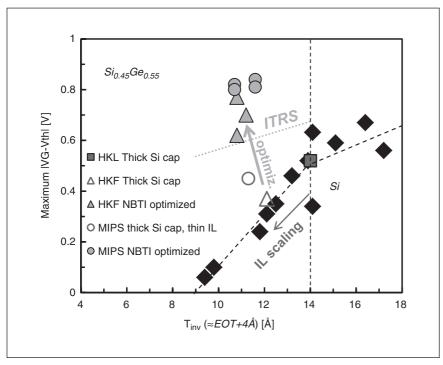

Fig. 3. Optimized SiGe devices boost the maximum operating overdrive to meet the target  $V_{\rm nn}$  at ultra-thin EOT.

is clearly observed that below 1 nm EOT the NBTI degradation is faster than expected. The extrapolated operating field at 10 year lifetime is plotted versus the EOT in the inset in Figure 2. Conversely to ITRS specifications, the devices below 1 nm EOT show a rapid decrease in the maximum operating field. The strong electric field dependence change below 1 nm suggests a different or additional NBTI degradation mechanism in the sub 1-nanometer EOT regime. We have found the additional mechanism for this severe degradation in sub-nanometer EOT devices to be the increased bulk charge trapping effect enhanced by the reduced interfacial layer [2]. This means that it will become more and more difficult to guarantee the lifetime of the transistors as it was done before using the classical accelerated testing approaches.

There are some technology solutions available for the dramatic reduction in BTI lifetime. One of them is the use of SiGe-based devices, which are not only investigated to

boost the performance by their higher mobility, but also promise a significantly improved NBTI robustness, as is illustrated on Fig. 3. To benefit from this property, the SiGe quantum well devices were optimized for enhanced reliability, including a high Ge fraction in the channel, a sufficiently thick quantum well and a Si passivation layer of reduced thickness [3, 4]. By means of such optimization, sufficiently reliable ultra-thin EOT SiGe pMOSFETs with a 10 year lifetime at operating conditions in both gate-first and gate-last process flows were demonstrated, as shown on Fig. 3 [5].

Nevertheless because of such reduced reliability margins in the future we will have to learn to design reliable circuits with unreliable components. Interaction with the design community to fine-tune the lifetime assessment and using realistic circuit-based failure criteria becomes mandatory [6].

On top of this trend another one is observed in reliability assessment, namely the impact of increas-

ing statistical variability of the degradation effects, comparable to the well-known increasing variability of the initial parameters. Until now, the large, micrometer-sized FET devices of the past CMOS technologies were considered identical in terms of electrical performance. Similarly, the application of a given stress resulted in an identical parameter shift in all devices. With the gradual downscaling of the FET devices the oxide dielectric was the first to reach nanometer dimensions, thus introducing the first stochastically distributed reliability mechanism—the Time Dependent Dielectric Breakdown. With the shrinking of lateral device dimensions to sub-22 nm levels, variations between devices start to appear due to effects such as random dopant fluctuations and line edge roughness [7, 8]. Similarly, application of a fixed stress in such devices results in a distribution of the parameter shifts [9, 10]. Understanding these distributions is crucial for correctly predicting the reliability of future deeply downscaled technologies [11].

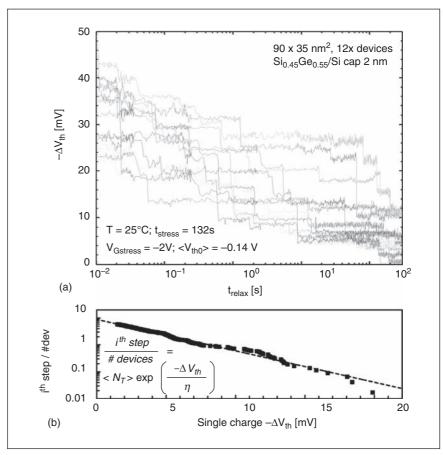

In such deeply downscaled CMOS technologies only a handful of defects is present in each device, while their relative impact on the device characteristics is significant. The behavior of these defects is stochastic, voltage and temperature dependent, and widely distributed in time, resulting in each device behaving very differently during operation. Fig. 4 shows a typical result of a Measure-Stress-Measure (MSM) measurement of a relaxation transient following NBTI (Negative-Bias-Temperature Instability) stress. Clear steps caused by single discharge events are visible in the NBTI relaxation transients. For larger device sizes these relaxation transients are continuous and spread over several decades in time. In this case, however, the average step height is significantly larger than reported earlier. It is important to note here that the steps corresponding to a single discharging event in some devices

exceed 30 mV, the BTI lifetime criterion presently used by most groups, which means that 1 single charge can cause threshold voltage shifts as high as the failure criterion. The histogram of the step heights is shown on Fig. 4b.

This trend leads to a shift in our perception of reliability: the "topdown" approach (deducing the microscopic mechanisms of average degradation in large devices) is being replaced in deeply-scaled devices by the "bottom-up" approach, in which the time-dependent variability of several degradation mechanisms, such as RTN and BTI, is understood in terms of charging and discharging of individual defects.

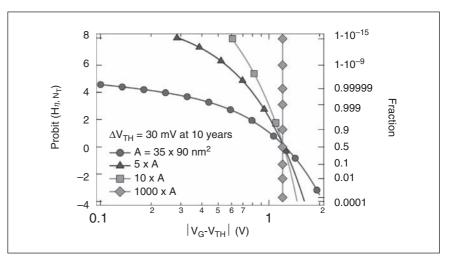

Values of  $\Delta V_{th}$  caused by individual defects appear to be approximately exponentially distributed in our devices (Fig. 4b) [12,13] The average  $\Delta V_{th}$  value of the distribution  $\eta$ scales inversely with device area but is expected to improve with lower channel doping concentrations. The knowledge of single defect impact distribution, combined with the assumption of Poisson-distributed number of defects per device, allows predicting the distribution of the total degradation per device [12,13] and projecting the fraction of failing devices at 10 years, as is shown on Fig. 5 [11]. This figure clearly shows the trend: for large area devices, like in the past, all devices behave identical and have one single predicted maximum overdrive voltage. But for nanoscaled devices, although the median of the devices has the same maximum overdrive as the large area devices, there is a huge tail towards lower maximum overdrives. This poses new challenges on the reliability assessment and assurance of such nanoscaled technologies.

In conclusion, it is generally accepted that reliability margins assessed using the classical method are rapidly vanishing. This becomes more critical when in the near future the use of high-mobility channels will be considered for further device

Fig. 4. (a) NBTI relaxation transients recorded on nanoscaled SiGe devices. (b) Weighted complementary Cumulative Distribution Function (CCDF) plot of the individual  $\Delta V_{\tau H}$  step heights observed on multiple devices. The average number of defects per device,  $\langle N_{\tau} \rangle$ , can be easily read in this plot as the intersection of the distribution with the y-axis [11].

Fig. 5. Predicted 10 years maximum overdrive cumulative distributions of the pFET for  $\Delta V_{th}$  = 30 mV at  $t_{color}$  = 1 ms for various device area. The median overdrive is independent of device area, but a significant fraction exceeds failure criteria at lower overdrives as the device area decreases [11].

performance enhancement in future CMOS technology nodes. (Si)Ge and III-V based quantum well devices are the first candidates for p- and n-type

channels, respectively. Although promising drive current performance has been reported for these devices by several groups, much less information on their reliability is available. Nevertheless, it is mandatory that, besides good performance and mobility, also sufficient reliability can be guaranteed before these Beyond-Silicon devices can be considered for production.

Next to this, the increasing systematic and statistical variability caused by the stochastic nature of the failure mechanisms will have to be considered in the design of future ULSI circuits. To that end, the time dependence of the parameter distributions during circuit operation, after being thoroughly understood, will need to be inserted into circuit simulators. Recent work has shown very strong workload-dependent characteristics in the aging of scaled devices and wires. As a result a need has emerged for mixed statisticaldeterministic modeling approaches [6] as opposed to the early worstcase modeling or more recent statistical modeling options.

Reliability assessment of future applications can thus be seen as time-dependent variability analysis. All this will ultimately lead to a paradigm shift in the reliability assessment and assurance of future technologies, circuits and systems, which will have to be guaranteed at the system design level rather than at the device and technology level. Research is underway to develop such reliability-aware design methodologies [15] which will change the operation conditions of the critical transistors during runtime.

#### References

[1] G. Groeseneken, R. Degraeve, B. Kaczer and K. Martens L, "Trends and perspectives for electrical characterization and reliability assessment in advanced CMOS technologies", Proceedings ESSDERC conference 2010, p. 64–72, 2010.

[2] M. Cho, J-D Lee, M. Aoulaiche, B. Kaczer, P. Roussel, T. Kauerauf, R. Degraeve, J. Franco, L. Ragnarsson, G. Groeseneken, "Insight Into N/PBTI Mechanisms in Sub-1-nm-EOT Devices", IEEE Trans El. Dev. Vol 59, p. 2042, 2012.

[3] J. Franco, B. Kaczer, M.J. Cho, G. Eneman, T. Grasser and G. Groeseneken, "Improvements of NBTI reliability in SiGe p-FETs," in Proc. IEEE IRPS, pp. 1082–1085, 2010.

[4] J. Franco, B. Kaczer, G. Eneman, J. Mitard, A. Stesmans, V. Afanas'ev, T. Kauerauf, Ph.J. Roussel, M. Toledano-Luque, M. Cho, R. Degraeve, T. Grasser, L.-Å. Ragnarsson, L. Witters, J. Tseng, S. Takeoka, W.-E. Wang, T.Y. Hoffmann and G. Groeseneken,. "6Å EOT Si0.45Ge0.55 pMOSFET with Optimized Reliability (V<sub>DD</sub> = 1V): Meeting the NBTI Lifetime Target at Ultra-Thin EOT, in Proc. IEDM, pp. 70–73, 2010;

[5] J. Franco, B. Kaczer, M. Toledano-Luque, Ph.J. Roussel, J. Mitard, L.-Å. Ragnarsson, L. Witters, T. Chiarella, M. Togo, N. Horiguchi, G. Groeseneken, M.F. Bukhori, T. Grasser and A. Asenov, "Impact of single charged gate oxide defects on the performance and scaling of nanoscaled FETs", Proceedings IEEE International Reliability Physics Symposium., p. 5A.4.1–6, 2012.

[6] D. Rodopoulos, S. Mahato, V. Valduga de Almeida Camargo, B. Kaczer, F. Catthoor, S. Cosemans, G. Groeseneken, A. Papanicolaou and D. Soudris,,"Time and Workload Dependent Device Variability in Circuit Simulations", Proceedings of the IEEE International Conference on IC Design and Technology (ICIDT), p. 978-1-4244-9021-9/11, May 2011.

[7] A. Asenov, "Random dopant induced threshold voltage lowering and fluctuations in sub-0.1 mu m MOSFET's: A 3-D "atomistic" simulation study," IEEE Trans. El. Dev., vol. 45, p. 2505, 1998.

[8] A. Asenov, S. Roy, R.A. Brown, G. Roy, C. Alexander, C. Riddet, C. Millar, B. Cheng, A. Martinez, N. Seoane, D. Reid, M.F. Bukhori, X. Wang,

U. Kovac, "Advanced simulation of statistical variability and reliability in nano CMOS transistors", IEEE Tech Digest International Electron Device Meeting (IEDM), p. 421, 2008.

[9] S. E. Rauch, "Review and reexamination of reliability effects related to NBTI-induced statistical variations", IEEETrans. Dev. Mat. Rel., p. 524, 2007.

[10] V. Huard C. Parthasarathy, C. Guerin, T. Valentin, E. Pion, M. Mammasse, N. Planes, L. Camus, "NBTI degradation: from transistor to SRAM arrays" Proceedings IEEE International Reliability Physics Symposium., p. 289, 2008.

[11] M. Toledano-Luque, B. Kaczer, J. Franco, Ph.J. Roussel, T. Grasser, T.Y. Hoffmann, and G. Groeseneken, "From mean values to distributions of BTI lifetime of deeply scaled FETs through atomistic understanding of the degradation," IEEE VLSITechnology SymposiumTech Dig., p. 152–153, 2011.

[12] B. Kaczer, T. Grasser, Ph. J. Roussel, J. Franco, R. Degraeve, L.-A. Ragnarsson, E. Simoen, G. Groeseneken, H. Reisinger, "Origin of NBTI variability in deeply scaled pFETS's", Proceedings IEEE International Reliability Physics Symposium, p. 26, 2010.

[13] B. Kaczer, Ph. J. Roussel, T. Grasser and G. Groeseneken, "Statistics of multiple trapped charges in the gate oxide of deeply-scaled MOSFET devices—application to NBTI", IEEE Electron Device Letters, vol. 31, p. 411–413, 2010.

[14] B. Kaczer, J. Franco, M. Toledano-Luque, Ph. J. Roussel, M. F. Bukhori, A. Asenov, B. Schwarz, M. Bina, T. Grasser and G. Groeseneken, "The relevance of deeply-scaled FET threshold voltage shifts for operation lifetimes," Proceedings IEEE International Reliability Physics Symposium., p. 5.A.2.1–6, 2012.

[15] S. Hamdioui, D. Gizopoulos, G. Groeseneken, M. Nicolaidis, A. Grasset and P. Bonnot, "Reliability challenges of real-time systems in forthcoming technology nodes," Design, Automation & Test in Europe

Conference & Exhibition-DATE, Proceedings pp.129-134, 2013.

Groeseneken

Guido Groeseneken is an IMEC Fellow and Professor at the KU in Leuven, Belgium, where he is Program Director of European Erasmus Mundus Master program in

Nanoscience and nanotechnology. He is responsible for research in reliability physics for deep submicron CMOS technologies at IMEC and has made contributions to the fields of non-volatile semiconductor memory devices and technology, reliability physics of VLSI-technology, hot carrier effects in MOSFET's, time-dependent dielectric breakdown of oxides, Negative-Bias-Temperature Instability effects, ESD-protection andtesting, plasma processing induced damage, electrical characterization of semiconductors and characterization and reliability of high k dielectrics. Recently he has also interest in nanotechnology for post-CMOS applications, such as carbon nanotubes for interconnect and sensor applications, tunnel FET's for alternative ultra-low power devices. He has served as a technical program committee member of several international scientific conferences, IEDM, IRPS, IEEE SISC, European Solid State Device Research Conference (ESSDERC) and the EOS/ESD Symposium. From 2000 until 2002 he also acted as European Arrangements Chair of IEDM. He was the General Chair of the Insulating Films on Semiconductor (INFOS) conference in 2005. From 1999 until 2006 he was an editor of IEEE Transactions on Electron Devices. Since January 2005 he is elected to the grade of IEEE Fellow.

#### REPORT ON 2015 IEEE INTERNATIONAL RELIABILITY Physics Symposium

The IRPS15 held from April 19-23, 2015, at the Hyatt Regency Monterey Resort and Spa, Monterey, California, USA, serendipitously kicked off exactly on the 50th anniversary of Moore's Law on April 19th which was recognized in IEEE Spectrum's April publication. The key question with respect to reliability—can Moore's Law continue and not be limited by reliability? IRPS15 technical program kicked off with keynotes by Kaizad Mistry of Intel and Brent Keeth of Micron respectively addressing these topics.

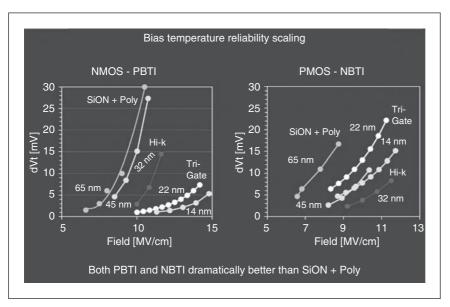

Kaizad Mistry illustrated Dennard's classical scaling which was applicable through the late 1990's and how a "golden age of innovation" was occurring with advent of strained silicon, high-K metal gate, and tri-gate (fin-fet) introduction in the 21st century. Improvements in reliability mode data of time dependent dielectric breakdown (TDDB), bias temperature instability (BTI), and soft error were reviewed.

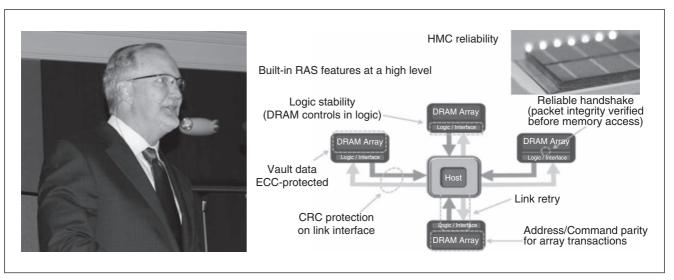

Brent Keeth presented dynamic random access memory (DRAM) performance and scaling, citing the need for a dramatic performance changes to ready 1 TB/s bandwidth, reduced energy consumption of 5mW/ GB/s, and x-scale computing of 1018 Flops/s. A radical rethinking of DRAM design to utilize tightly stacked memory in through silicon vias (TSV) coupled with a logic layer to manage the memory and communications with the host which included reliability, availability, and serviceability (RAS) features. These keynotes provided excellent introduction to the technical program and substantial motivation towards continual enabling of reliability aspects of Moore's Law!

IRPS15 technical program featured reliability topics focusing on the continued advancement of Moore's Law with several 14 nm and many FIN- FET papers from industry leaders. The technical program kicked off with a first-ever combined gate dielectrics and back-end-of-line (BEOL) breakdown session which was highly attended. As dimensions have been scaled continuously, new considerations for interconnect dielectric breakdown must be made in addition to traditional electromigration reliability. Wednesday's evening poster session, in the Monterey Grand Ballroom, featured over seventy-five poster presentations accompanied by delicious dinner selections. Conference proceedings

Kaizad Mistry, VP Intel, delivering keynote "Transistors and Reliability in the Innovation Era."

Brent Keeth, Senior Fellow Micron, delivering keynote "Hybrid Memory Cube (HMC): Achieving High Performance and High Reliability" and Hybrid Memory Cube built in reliability, availability, and serviceability (RAS) features (courtesy Brent Keeth, Micron).

BTI reliability scaling by process generation showing effectiveness of innovation in making improvements in reliability with scaling (courtesy Kaizad Mistry, Intel).

are available in the *IEEE Xplore Digital Library*. The "best of IRPS15" will be announced on Twitter.

The next IRPS will be held in Pasadena, California, April 17–21, 2016. Call For Papers have been issued with an abstract deadline of October 12, 2015, and late news submissions due January 11, 2016. Please follow on Facebook, Linked-IN, Twitter @IEEEIRPS, and visit http://IRPS.org for latest information. The Device Reliability team looks forward to seeing you in Pasadena for IRPS16!

Chris Connor, Yuan Chen and Giuseppe LaRosa 2015 IRPS Publicity, Technical Program and General Chairs

#### WIDE BANDGAP SEMICONDUCTORS, THEY'RE SPECIAL

Recent advances in wide band gap semiconductors (typically compound, like Gallium Nitride (GaN) and Silicon Carbide (SiC), but also elementary, like Diamond) for power applications were a big hit during the IEDM 2014 conference. The IEDM invited plenary speech by J.W. Palmour of Cree, showed impressive data on the yield and performances of SiC devices on 15 cm substrates—micro-pipes still are a threat but their density has decreased so much that yield is almost unaffected. The pre-

sentation included an unusual testimonial for widegap semiconductors. US President Barack Obama himself in a speech held at NCSU on January 15, 2014, supporting a \$140 million proposal to bring a manufacturing innovation hub to Raleigh, with

Jayant Baliga as a principal investigator. "Wide bandgap semiconductors, they're special because they use up to 90 percent less power; they can operate at higher temperatures than normal semiconductors. So that means they can make everything from cell phones to industrial motors to electric cars smaller, faster, cheaper. There are still going to be applications for traditional semiconductors, but these can be focused on certain areas that will vastly improve energy efficiency, vastly improve the quality of our lives." See the transcript of Barack Obama's speech, http://www.bizjournals.com/triangle/ transcript-of-president-obamasspeech.html?page=all.

As pointed out by Prof. Baliga in the invited paper Social Impact of Power Semiconductor Devices, those play a fundamental role in a sustainable society and involve an impressive range of applications, from transportation to air conditioning and refrigeration to lighting. Two-digit improvements in efficiency have led, during the last 20 years, to staggering results in terms of energy consumption and decrease in carbon dioxide emissions.

Cars are one of the major sources of carbon dioxide emission and 93.5% of the energy used for transportation is based on fossil fuels. This could be improved in the future with a more widespread use of Hybrid Electrical Vehicles (HEV) and EVs. Researchers from Toyota Central R&D Labs presented a novel SiC vertical JFET for automotive applications, allowing for a 50% reduction of switching losses vs. conventional MOSFETs. Despite their impressive performances, widegap semiconductor power devices based on SiC or GaN should be targeted towards specific applications where they bring real advantages in terms of performance but also cost vs. Si. A complex SWAT analysis of different technologies for power switching is discussed, by researchers from Infineon. In a nutshell, Si still dominates for low price applications, SiC for high-end, high voltage applications, GaN (but only in the GaN-on-Si variety) for high-end and medium voltage applications.

Widegap power semiconductor devices will also play a fundamental role in smart power grids. SiC devices with ultrahigh breakdown voltage (>10 kV) for UHV applications in power grids (researchers from Kyoto University, AIST and Kansai Electric Power). An optimized PiN SiC process is described with high temperature performances up to 250 C and 70% expected power reduction expected vs. Si converters operating at a switching frequency of 2 kHz.

GaN has become widespread in our homes thanks to the introduction of GaN-based LED high-efficiency lighting (as recognized by the recent Nobel prize in physics to Isamu Akasaki, Hiroshi Amano and Shuji Nakamura), but very soon domestic appliances exploiting GaN power devices will become widespread, at least in Japan. PV conditioners using 600 V GaN-on-Si devices will be sold on the Japanese market starting January 2015. The PV conditioner exploits a JEDEC-qualified GaN-on-Si process using a cascode configuration with a normally-off Si MOSFET. The 1500 V breakdown voltages ensures reliability in the targeted 600 V application, with a 40% loss reduction and size reduction when compared to a Si implementation; the switching frequency is 27 MHz and careful packaging alleviates EMI problems. In the future, 900 V emode devices will be on the market.

Bulk GaN substrates could be the ultimate solution for GaN electronics, in particular for vertical devices. Researchers from the Advanced Research Projects Agency show an overview of available widegap

power solution, having in mind a target price of 0.1 \$/A at 40 KHz switching frequency. Contrary to common belief, the SiC solution is not necessarily more expensive than the Si one-the cost is higher but also the power density is larger. For GaN-on-GaN vertical devices, the current solutions are monothermal GaN boules or GaN transferred substrates obtained by epitaxial lift-off.

A last area of interest is diamond power electronics, for which the main challenge remains n-type doping in bipolar diodes and transistors. A possible solution for power diamond devices avoiding the issues related to doping is the surface H-termination (already proposed about 20 years back), that induces a surface 2D hole gas, allowing for the development of diamond-based MESFETs and MOSFETs. Very good results in terms of stability and highvoltage operation were presented by Waseda University researchers. The technology exploited here is a MOSFET with an Al2O3 layer. The proposed process also has good properties in terms of high-temperature behavior up to 400 C.

IEDM 2014 had sessions where many technological developments were reported, and the contribution of the session invited speakers well summarized the contents of the sessions: Dr. Tetsu Ueda, from Panasonic reported on the potential of the GaN HEMTs in the power switching applications. Prof. Gaudenzio Meneghesso, from the University of Padova, provided an important overview of the most critical parasitic effects today present in these devices that need to be taken care of, to allow for a large market penetration.

> Giovanni Ghione Politecnico di Torino

Gaudenzio Meneghesso University of Padova

#### UPCOMING TECHNICAL MEETINGS

# 2015 IEEE INTERNATIONAL INTEGRATED RELIABILITY WORKSHOP (IIRW)

The 2015 IEEE International Integrated Reliability Workshop (IIRW), sponsored by the IEEE Reliability Society and the IEEE Electron Devices Society, will be held at the Stanford Sierra Conference Center on the shores of Fallen Leaf Lake near South Lake Tahoe, California, October 11–15, 2015. This workshop provides a unique forum for open and frank discussions of all areas of reliability research and technology for present and future semiconductor applications.

Some of the highlights of this year's technical program will include:

- A keynote speech on Product Reliability given by Prasad Chaparala, Director, Hardware Reliability Engineering, Amazon Lab 126

- A strong collection of invited speakers including (but not limited to): John Conley Jr. (Oregon State University)—Dielectric Stack Engineering; Christian Shweta Deora (Sematech)—RRAM Reliability; JH Lee (TSMC)—FEOL Reliability; Sang-Woo Pae (Samsung)—FEOL Reliability; Pieter Wechx (IMEC)—RTN and BTI time-dependent reliability, John Robertson (Cambridge University)—Reliability of III-V MOSFETs

- A strong tutorial program will cover many hot reliability topics including (and not limited to) radiation effects on devices including non-volatile memories, 14 nm node FinFET reliability, LDMOS reliability & modeling, reliability of power GaN devices, physical analysis of device degradation (TEM, STM, CAFM etc.).

- On Sunday (first) night "tech lite" presentation: Brian Schratz, Lead Engineer, Entry Descent

View of Fallen Leaf Lake from the ski dock at the Stanford Sierra Conference Center. The Stanford Sierra Conference Center provides lodging, meals and meeting facilities as well as excellent recreation including hiking in the Desolation Wilderness and boating on Fallen Leaf Lake

and Landing Telecommunications Team, **Mars Curiosity Rover**, JPL-NASA

The IIRW is also an excellent forum to present new and original technical works. Reliability topics for the workshop include: SiGe and strained Si, III-V, SOI, high-k and nitrided SiO2 gate dielectrics, reliability assessment of novel devices, organic electronics, emerging memory technologies (RRAM etc.) and future "nano"-technologies, NEMS/MEMS, photovoltaic's, transistor reliability including hot carriers and NBTI/ PBTI, Cu interconnects and low-k dielectrics, product reliability and burn-in strategy, impact of transistor degradation on circuit reliability, reliability modeling and simulation, optoelectronics, single event upsets, as well as the traditional topics of wafer level reliability (WLR) and built-in reliability (BIR). The Call for Papers can be found at the web address (www. iirw.org). The abstract submission deadline is July 12, 2015. Contact the Technical Program Chair, Richard Southwick (southwick@us.ibm. com) for further details. Also, visit www.iirw.org for continued updates about the conference. Also note that all attendees have the opportunity to present a "walk-in" poster of their latest work. This is a great way to share that new project you are working on and to get world-class feedback

IIRW is fairly different from a typical technical conference. Located 6000 ft. high in the Sierra Nevada Mountains, the Stanford Sierra Conference Center provides an ideal atmosphere for a relaxing yet informative workshop. Nestled throughout the pines and cedars along the shoreline of Fallen Leaf Lake, attendees stay in cabins furnished in the

rustic style of an alpine resort. All cabins have decks with magnificent views of Fallen Leaf Lake and the surrounding Sierra peaks. Comfortable, informal dress is encouraged, affiliations are downplayed, and meals are provided family-style in the lodge dining room.

All aspects of the workshop, including the physical isolation of the venue, the absence of distractions such as in-room phone and televisions, and the format of the technical program encourage extensive interaction among the workshop attendees. Such opportunity is seldom available at most other conferences. Participants spend their evenings at poster sessions, discussion groups, and special interest groups, all com-

plemented with refreshments and snacks. The evening moderated discussion groups provide a forum with unparalleled access to world experts to discuss a wide array of relevant reliability issues. Often these discussions lead to the formation of a smaller special interest group, whose discussions extend long after the conclusion of the workshop.

The technical program is purposely kept open for Wednesday afternoon to allow attendees to enjoy a variety of the outdoor activities which the Stanford Sierra Conference Center location has to offer. These include hiking, sailing or kayaking, walking, or simply continuing that intriguing conversation from the night before. This free afternoon is a

great way to not only network, but also to build long-lasting friendships.

Additional information about the workshop is available on the IIRW website at www.iirw.org, or by contacting Jason Ryan, NIST, 2015 IIRW General Chair, (Jason.ryan@nist.gov) Note: If you want to take part in this event, please register early as space at the Stanford Sierra Conference Center is limited to roughly 120 attendees and the workshop has sold out in the past.

On behalf of the 2015 IIRW Committee, I look forward to meeting you in Lake Tahoe!

Barry O'Connell 2015 IIRW Communications Chair Fairchild Semiconductor San Jose, CA, USA

#### 2015 IEEE COMPOUND SEMICONDUCTOR IC Symposium (CSICS)

OCTOBER 11th-14th IN NEW ORLEANS, LOUISIANA

The 2015 IEEE CSICS will be held on October 11th-14th at the Sheraton Hotel located in New Orleans, Louisiana, USA.

The Compound Semiconductor IC Symposium (CSICS) covers GaN, GaAs, InP, SiGe, and nanoscale CMOS technologies and their application to microwave/mm-wave, THz, analog mixed signal, power conversion, and optoelectronic IC design. Now in its 38th year, CSICS has become the premier symposium at which to present state-of-

the-art results in the areas of circuit switching speed, RF frequency of operation, RF output power, PA efficiency, and noise performance. The symposium also showcases the latest advances in emerging semiconductor device technology, modeling and manufacturing.

The symposium includes a three day dual track technical program, two short courses, a primer course, and a technology exhibition. Also, for the 2nd year, CSICS will offer a student paper competition. The technical program includes 60-70 high quality papers and 4 topical panel sessions. This year, CSICS is proud to announce 20 internationally renowned invited speakers, notably: Pascal Chavalier (ST), Jesus del Alamo (MIT), Eric Lind (Lund Univ.), Akira Nakajima (AIST), Masataka Higashiwaki (NICT), Thomas Zimmer (University of Bordeaux), Bruce Wallace (DARPA), Zoya Popovic (University of Colorado, Boulder), Ian Betty (Ciena), John Volakis (Ohio State University), Ken Brown (Raytheon),

Patrick Courtney (Qorvo), Bill Deal (Northrop Grumman), Kazuhiko Honjo (The University of Electrocommunications, Japan), Shogo Yamanaka (NEC), Takayuki Shibasaki (Fujitsu), Sam Palermo (Texas A&M), Nomand Wolf (HHI), Michel Poulin (TeraXion), and Efthymios Rouvalis (Finisar). These distinguished speakers will present the latest advances in SiGe BiCMOS, InGaAs MOSFET's, nanowire FET devices, E-mode GaN HEMT's, device modelling, mmwave/THz PA's and systems, spatially combined PA's, envelope tracking PA's, and low power RX and TX circuits and DSP's, as well as Si and InP modulators and drivers.

CSICS offers two in-depth short courses on Sunday, October 11th. The first course, Transmit and Receive IC Design for Fiber Optic Links, will be presented by leading experts: Linh Nguyen (Finisair), Kumar Lakshmikumar (Cisco), and Mark Webster (Cisco). This course details high-speed analog IC design basics for electronic and optoelectronic applications. The course will prove in-

valuable for anyone involved in high speed electronic or optoelectronic devices, circuit design, or systems.

The second course, Microwave Package Design Fundamentals, will be taught by leading high speed packaging experts. This course will cover the basics of microwave packaging for high speed and high power microwave applications. It will cover the packaging materials and technologies, assembly techniques, and design considerations for packaging high frequency microwave and mmwave devices. It will be useful for device, circuit, and system designers.

On Sunday evening, Waleed Khalil (Ohio State), will teach an expanded Primer Course on Si RFIC design. This 3.5 hour lecture is intended for participants of all technical backgrounds who wish to learn or refresh their understanding of the fundamentals of designing the principal circuit building blocks in radio and radar SoCs. Among the blocks covered are PAs, LNAs, Mixers, VCOs, as well as integrated passives, with examples drawn from

both CMOS and SiGe technology. The primer is an excellent way to start the symposium and is guaranteed to enhance attendee appreciation of the technical program.

In recognition of the exceptional contributions made by students, CSICS is proud to hold its second Student Paper Competition. To participate in the competition, an eligible student must submit a regular contributed paper naming, at a minimum, themselves and their principal supervisor as authors. The Student Paper Finalists must present their own papers at their assigned symposium session.

For registration and up-to-date information, please visit the CSICS website at www.csics.org. Further questions may be addressed to the Symposium Chair: Dr. Charles F. Campbell, Phone: +1 972 994-3644, e-mail: Charles.Campbell@gorvo.com.

We hope you can attend, 2015 IEEE CSICS Organizing Committee

Bruce Green CSICS 2015 Publicity Chair

# 2015 IEEE BIPOLAR/BICMOS CIRCUITS AND TECHNOLOGY MEETING (BCTM)

BOSTON HYATT, BOSTON, MA, USA

WWW.IEEE-BCTM.ORG

SHORT COURSE: MONDAY, OCT. 26, 2015, CONFERENCE: TUESDAY-WEDNESDAY, OCT. 27-28, 2015

Jean-Baptiste Begueret

Doua Weiser

Invitation to IEEE BCTM 2015

On behalf of the IEEE BCTM'15 Executive Committee, we are honored

and delighted to invite you to the 2015 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) at the Boston Hyatt, Boston, Massachusetts, October 26–28, 2015. We invite you to participate at the 2015 BCTM where the highlights include:

- Keynote addresses "5G Systems" by Dr. Yukihiko Okumura of NTT DOCOMO

- Day-long short-course on How to Make Great RF Products Using BiCMOS Technologies

- Guofo Niu (Auburn University): Device Physics and Optimization for RF Applications

- Colin McAndrew (Freescale): Models for RF Circuit Simulation: Capabilities and Shortcomings

- Lawrence Larson (Brown University): Design fundamentals for RF Transmitters and Receivers

- Freek van Straaten/Henk Thoonen (NXP): Packaging Challenges for RF

- Forward-looking Emerging Technologies Session with invited speakers: Dieter Knoll (IHP) on "Photonic BiCMOS technology" and Pascal Chevalier (STMicroelectronics) on "14 nm FDSOI and HBT integration feasibility"

- Invited papers exploring advances in process technology, device physics, wireless design, analog/mixed-signal, and modeling

- Technical papers covering the latest advances in physics, design, performance, fabrication, characterization, modeling, and application of Si/SiGe/SiC bipolar, BiCMOS, and GaN ICs

- Evening dinner banquet

The IEEE BCTM is a forum for technical communication focused on the needs and interests of the bipolar and BiCMOS community. Papers covering the design, performance, fabrication, testing and application of bipolar and BiCMOS integrated circuits, bipolar phenomena, and discrete bipolar devices are solicited. A Special Issue of the IEEE Journal of Solid-State Circuits will include selected papers from BCTM 2015.

#### **General Contact Information**

Visit the conference website www. ieee-bctm.org or contact Catherine Shaw, Conference Manager: Phone: 1-732-501-3334, e-mail: cshaw.cmpevents@gmail.com

The IEEE BCTM is the world's premier forum focused on the needs and interests of the bipolar and BiCMOS community. If you are interested in leading edge bipolar/BiCMOS devices and technology, circuits, and applications, as well as networking with experts in these areas, please kindly join us this year in the beautiful city of Boston, MA, USA.

> Jean-Baptiste Begueret 2015 BCTM General Chair University of Bordeaux

Doug Weiser 2015 BCTM Technical Program Chair Texas Instruments

#### SOCIETY NEWS

#### EDS VISION AND MISSION STATEMENTS

#### **Vision Statement**

Promoting excellence in the field of electron devices for the benefit of humanity.

#### Mission Statement

To foster professional growth of its members by satisfying their needs for easy access to and exchange of technical information, publishing, education, and technical recognition and enhancing public visibility in the field of Electron Devices.

#### EDS PRESIDENT'S MESSAGE

Albert Wang EDS President

Dear Fellow EDS Members,

I am writing this Message in the air, which reminds me of two things: time does fly at a speed certainly not slower in an airplane and

our volunteers are busy with their day jobs. Therefore, this Message should be informative, yet short.

Our last year-end Board of Governors (BoG) meeting series was held December 13-14, 2014, in San Francisco. As usual, several group working meetings were held on Saturday, December 13th, including all Standing Committee meetings and some Technical Committee meetings, i.e., the Power Devices and ICs Committee meeting and the Optoelectronic Devices Committee meeting. The BoG general meeting was held on Sunday, December 14th. Following a new format, the BoG meeting had a one-hour Open Forum session for all attending volunteers to discuss general issues of interests to EDS. The December BoG meeting was very fruitful and covered many critical issues.

One topic that attracted lots of attention was on developing new Editor-in-Chief (EIC) Selection and Evaluation Procedures for the EDS journals including IEEE Transactions on Electron Devices (T-ED), IEEE Electron Device Letters (EDL), and the IEEE Journal of the Electron Devices Society (J-EDS). As a brief background, this new EIC selection proposal development task is part of the effort that I have been pushing for, aiming to ensure transparency of EDS operations in response to EDS members' voices recently. Believe or not, EDS does not have a formal written policy for its journal EIC evaluation and selection. A task force, led by Samar Saha (past VP for Publications) and Bin Zhao (VP for Publications and Products), was formed to investigate the details and to develop new formal EIC Selection and Evaluation Procedures.

There were extensive discussions among volunteers on this EIC selection matter during the Publications and Products Committee (PPC) meeting and BoG general meeting in San Francisco. Various comments and opinions on the EIC selection matter have been expressed during the meetings in San Francisco and after that, which clearly indicated that the EIC selection issue is a critical matter to our members and the existing EIC selection practices have room for improvement. As a result, two resolutions were recently approved by the PPC committee and the EDS Forum: first, the new "working" EIC Selection Proposal will be used for the immediate task of EIC selection for T-ED and EDL; second, a parallel process will continue for the PPC committee to develop and finalize the final written EIC Selection and Evaluation Procedures for future use, which will be submitted to the Forum and BoG for approval before the end of 2015. I want to remind all EDS members that the goal of this EIC selection proposal task is about transparency of EDS operations, fair opportunities for members, spirits of rotation for volunteer services, and avoiding potential conflict of interests. At this time, all EDS members should have received several email notices about nominations for the current TED and EDL EIC Search. I appreciate your active participation in this critical business.

Operations transparency is also a heated topic at IEEE level. It has drawn lots of attention recently, with the main focus on IEEE finance transparency. Largely initiated by a presentation on EDS incomes and the growing IEEE TAB support fees by then EDS President, Paul Yu, at the IEEE Technical Activity Board (TAB) meeting in February 2013, a group of five IEEE society presidents, including EDS, started to work together to lead the effort to push for IEEE finance transparency. An Ad Hoc IEEE Fin-Trans task group was formed in early 2014 to focus on this major task, and presented its analysis and motions at each IEEE TAB meeting since February 2014. We are seeing progresses now, though slowly. The IEEE finance team has been cooperating with the Fin-Trans Ad Hoc by providing IEEE financial data to selected societies for analysis on a trial basis. As volunteers who dedicate our time and effort to IEEE professional activities, we certainly deserve a transparent picture of IEEE finances. Considering the volunteer and rotating nature of member services, this Fin-Trans effort is deemed to be a challenging task. I will continuously update you on this matter.

The EDS mid-year Governance meeting series was held May 30–June 1, 2015 in Singapore. To encourage more active participation from EDS members, a two-hour Open Forum session was arranged for volunteers to discuss any EDS related issues. For a summary of the Governance meeting, see pages 16 and 17. To conclude this Message, I encourage you to write to me for any of your concerns and comments on EDS business.

Sincerely, Albert Wang from Southern California

Albert Wang is a Professor of Electrical and Computer Engineering at the University of California, Riverside. He is President for IEEE Electron Devices Society (2014-2015) and an IEEE Fellow. His research interests center on RF and mixed-signal IC designs, integrated design-for-reliability, device and circuit integration, emerging devices and circuits, and IC CAD.

#### Message from VP Regions and Chapters

"Joe" Xing Zhou EDS Vice President-Regions/Chapters

This is the third year I have been serving as VP-Regions/Chapters (R/C), and I would like to take this opportunity share with EDS members and volunteers some of my observations

and thoughts related to EDS regions and chapters. A year ago, I wrote Message from VP-Regions/Chapters [Newsletter, p. 11, July 2014], in which I outlined some major activities and programs under R/C, such as chapter subsidy, chapter of the year (CoY) award, sub-committee for regions/chapters (SRC), distinguished lecturer (DL) and mini-colloquia (MQ) programs, and some ideas for improvements. Many of the topics we discussed over the years in R/C committee meetings "were centered on how to serve members and reward volunteers at the society/ region/chapter levels" [Newsletter, p. 11, Oct. 2013], and many of the ideas I proposed were detailed at the December 2012 AdCom meeting in my role as SRC-R10 chair, when I was appointed as the incoming VP-R/C.

Members and chapters are the grass-roots of a society, without them there will be no society and no meaning for such a volunteer-driven organization. Among the society (or IEEE) members, they can be largely categorized into two groups: active members (or "volunteers") and inactive members (who just pay dues without participating in any society activities). Among the volunteers, they can be active members at two different levels: chapter and society (the SRC within EDS is an "intermediate" regional level that is actually belonging to society level). Among the chapters, there is a large variety of different needs and practices: some are financially strong with large member base and well-established renewal process, and others are in short of funds or relying on institutional resources and struggle to maintain membership. The linkage between chapters and the society has been various programs under R/C, such as the biennial regional chapter meetings as well as the subsidy, CoY, DL/MQ programs. These programs have been designed to better "serve members and reward volunteers" with different levels of success over the years, and it has been a major challenge on how to improve these programs to serve the variety of different needs of chapters and members. With the limited total funds, ideally it would be better to have non-uniform fund allocation and targeted fund utilization for the diversity in different needs. However, it has always been a difficult task for making changes over established practices.

The DL and MQ programs have been very popular and successful among our chapters. Unlike some other societies, our DLs are not designed for the "prestige" but for serving our chapters. The limited funds are meant for assisting DLs and chapters in organizing technical events for members. We have been encouraging coordinated MQ organization and leveraging various resources. One good example was the joint MQs (WIMNACT-42, 43, 44) in November 2014, coordinated by Prof, Steve Chung as SRC-R10 chair, in which a group of DLs visited the Shanghai, Nanjing, and Hangzhou chapters in a combined trip with funds from the MQ and SRC budgets as well as chapters' support. However, we do still have a situation in which DL participation and chapters hosting MOs are very non-uniform. We need to assist those less-active DLs to participate and especially to serve those less-active chapters. SRC chairs/vice-chairs and R/C committee members can also serve the roles in linking DLs to chapters. Besides "top-down" assistance from EDS and SRC, "bottom-up" pro-active initiatives from all DLs as well as local chapters are also the key to engaging more DLs and chapters in these programs. I'd like to call for all DLs to check the EDS chapters' map (http:// eds.ieee.org/global-chapters-map. html), and contact EDS/SRC for assistance if needed, to link with local chapters for a DL talk when traveling to various places. For MQ initiators, we also encourage coordination for joint events with nearby chapters and in conjunction with regional conferences. It is important to note that we would like to leverage various resources and DLs being on a side-trip, rather than supporting DLs to attend paid conferences from DL/MQ budgets. Together, let us work towards better service for our members and reward our volunteers.

"Joe" Xing Zhou EDS Vice President-Regions/Chapters Nanyang Technological University Singapore

"Joe" Xing Zhou, Vice President of Regions/Chapters of IEEE EDS, is a professor at Nanyang Technological University, Singapore. His group has been developing a core compact model for silicon bulk-CMOS, SOI, FinFET and nanowire, as well as III-V HEMT devices. He was a guest-EiC for the Feb'2014 special issue of IEEE Transactions on Electron Devices on compact modeling for emerging devices, and is currently an editor for IEEE Electron Device Letters.

#### MESSAGE FROM EDITOR-IN CHIEF

M K Radhakrishnan Editor-in-Chief, EDS Newsletter

Dear Readers,

Greetings from the EDS Newsletter team. We have initiated a new column "Reflections from Young Professionals" in the Newsletter starting from this issue. An in-

terview with a vivid EDS YP is published in this column. This column is intended to reflect the person's perception about the profession, IEEE as well as EDS and how the associa-

tion with EDS helps in nurturing the professional career. We are planning to have such interviews with EDS young professionals in different career paths and from all geographic regions in future.

In the Technical Briefs section the major article is on Reliability Trends in nanoscale CMOS Devices. This will be the first one of its kind on the device reliability trends. The technical summary and links of major conferences in devices area are also featured.

Summary of the deliberations at the EDS Board of Governors meeting held on 31 May 2015 at Singapore is included in this issue. Our idea is to communicate to all our members in a speedy manner. Newsletter is now available in mobile compatible Flipbook version also, apart from the print and pdf format. Also it is accessible to all through EDS website. However, we are not receiving sufficient feedback from our readers. We would like hear the readers' views, and I encourage everyone to write to me or to edsnewsletter@ieee.org

M K Radhakrishnan Editor-in-Chief, EDS Newsletter e-mail: radhakrishnan@ieee.org

#### EDS GOVERNANCE MEETING SUMMARY

#### Singapore Fling!

Fernando Guarin EDS Secretary

May 30-June 1, 2015: The EDS Mid-year Governance Meeting returned to Region 10 this year in grand style, bringing together the Society's senior leadership

with over 20 EDS Chapter Chairs from across Asia and the Pacific in beautiful Singapore. The meeting was a phenomenal success, combining vital society business with some truly special social events to create an enriching and energizing event for all attendees. The weekend began on Saturday morning, with a series of important Standing Committee meetings.

#### **Fellows Evaluations**

Despite long travel, and heavy jet-lag, the Fellows Evaluation Committee began their work bright and early Saturday morning, with the difficult task of reviewing and evaluating 47 IEEE Fellow nominations. Led by Guido Groeseneken, the committee deliber-

ated for over 9 hours, proving once again that the work of this committee is among the most challenging and important to the Society and the IEEE.

#### Publications and Newsletter Joint Meeting

Fernando Guarin and MK Radhakrishnan presented the status and recent improvements to the

ED Malaysia Chapter was selected as the 2014 recipient of the IEEE Electron Devices Society Region 10 Chapter of the Year Award.

'Joe' Xing Zhou, EDS VP Regions/Chapters (right), presenting award to Dr. Burhanuddin Yeop Majlis (Chapter Advisor) and Assoc.

Dr. Badariah Bais (Chapter Chair)

"My goal is to keep EDS a happy volunteer family with transparency and efficiency."

> Albert Wang EDS President

newsletter. The increased emphasis on technical content as well as the transition to web format received positive reviews.

Bin Zhao, EDS VP of Publications and Products, chaired the critical Publications committee meeting. In addition to reviewing the status of the ongoing in-depth and detailed searches for the T-ED and EDL Editors-in-Chief, the committee launched plans to improve the health and vitality of some of the smaller, cosponsored publications.

## Technical Committees and Meetings

Led by EDS's VP of Technical Committees and Meetings, Leda Lunardi, 2014 was a banner year for EDS's robust roster of technical meetings and conferences. To build on that success, the committee held a strategic planning

Attendees of the 2015 EDS Region 10 Chapters Meeting held at the Marina Mandarin Hotel, Singapore

Attendees of the EDS Board of Governors Dinner enjoyed the panoramic views of the Singapore skyline at the Pan Pacific Singapore Hotel (Marina Bay)

session to ensure not only the health of our conferences, but also define way to engage our 14 technical committees in all aspects of the society's affairs, such as publication, webinars, and defining new technical areas for the society to explore.

### Education, Membership, and Chapters

Combining three committee discussions into a single afternoon meeting, Vice Presidents Mikael Östling (Membership) and Joe Zhou (Regions and Chapters) and EDS Secretary and Education Chair, Fernando Guarín, convened an outstanding forum to address these critical areas of the society's life. In addition to providing an important strategic planning session, the highlight of the meeting was the open dialogue and frank discussion with over 20 EDS chapter chairs from across Region 10. Chapters are the life-blood of the society and this meeting provided an excellent opportunity for staff and volunteer leadership to learn more about the chapters' perspectives, needs, and successes and to gain valuable insight into how EDS needs to continually evolve to meet the needs of its key constituents throughout the globe particularly through the webinar and EDS-ETC programs.

#### **EDS Governance Meeting**

The EDS Forum and Board of Governors met on Sunday, May 31st, for the Mid-Year Governance meeting. The meeting's discussions covered nearly every aspect of the society's operations, ending with an extended Open-Forum to provide a free exchange of ideas and debate over how we can continue to improve the Society to ensure its preeminence as the world's leading organization devoted to device engineering. Here are some of the highlights:

RaviTodi, EDSTreasurer, reporting remotely, reviewed the finan-

- cial state of EDS and the news is good! We have well over a year's expenses in reserve. In addition he received approval for key 2016 budget inputs and additional spending in 2015 of roughly \$100K.

- Past Vice President of the IEEE Technical Activities Board (TAB), Jacek Zurada, joined us to present information on the TAB's strategic direction and some new initiatives to support it.

- Paul Yu, EDS Junior Past President and Awards Chair, successfully presented a proposal from the Photovoltaics Specialists Conference (PVSC) to elevate the conference's William Cherry Award to be an official EDS Society-level award. Now that EDS has approved, the next step is to seek TAB's approval, which will happen at the TAB meeting series in November.

(continued on back cover)

# CALL FOR NOMINATIONS EDS BOARD OF GOVERNORS—BOG (FORMERLY ADCOM) MEMBERS-AT-LARGE ELECTION

Paul Yu EDS Chair of Nominations & Elections

The IEEE Electron Devices Society invites nominations for election to its Board of Governors – BoG (formerly AdCom). The next election will be held after the BoG meeting on Sunday, December 6, 2015. This year, seven out of the twenty-two members will be elected for a 3-year term, with a maximum of two consecutive terms.

This year EDS will again be running the pilot program for one of the seven BoG Memberat-Large seats to be elected via the entire EDS membership. All nominees must choose to participate in either the election by EDS membership or the election by the BoG. There must be a minimum of two nominees for the seat elected by membership. If there are less than two nominees for the seat, an election by EDS membership will not be held and the candidate will be moved to the election by the BoG. All electees begin their term in office on January 1, 2016. The nominees need not be present to run for the election. Self-nominations are allowed.

Any EDS member who has served for a minimum of one year as an EDS Officer, Vice-President, Standing & Technical Committee Chair/Member, Publication Editor, and Chapter Chair is eligible to be nominated. The electees are expected to attend both BoG Meetings every year. While the December meeting is organized in connection with the IEEE International Electron Devices Meeting, the mid-year meeting is frequently held outside the US. Partial travel support is available to attend both of these meetings.

All nominees must be endorsed by one BoG member, i.e., one of the four officers (President, President-Elect, Treasurer or Secretary), the Jr. or Sr. Past President or one of the 22 current BoG Members-at-Large. It is the responsibility of the endorser to make sure that, if elected, the nominee is willing to actively serve in the position as a BoG member. In the unlikely event that a nominee must withdraw their name from the election ballot, they must do so by November 1, 2015.

Please submit your EDS BoG nomination by August 1, 2015, using the online nomination form (http://eds.ieee. org/bog-call-for-nominations.html).

Also, all endorsement letters should be sent to Laura J. Riello, EDS Executive Office, via e-mail: l.riello@ieee.org by August 1, 2015. If you have any questions, please feel free to contact Laura Riello (l.riello@ieee.org) with a copy to me at p.yu@ieee.org.

Paul Yu EDS Chair of Nominations & Elections University of California at San Diego San Diego, CA, USA

#### EDS BOARD OF GOVERNORS MEMBERS-AT-LARGE ELECTION PROCESS

Paul Yu **EDS Nominations** and Elections Chair

The Membersat-Large (MAL) of the EDS Board of Governors are elected for staggered 3-year terms, with a maximum of two consecutive terms. The 1993 Constitution and Bylaws

changes mandated increasing the number of elected MAL from 18 to 22, and required that there be at least two members from each of the following geographic areas: Regions 1-7 and 9; Region 8; Region 10. In 2003, EDS made changes to its Constitution and Bylaws to require that at least one elected BoG member is a Young Professional (YP - formerly Gold member). A Young Professional member is defined by IEEE as a member who graduated with his/her first professional degree within the last fifteen years. It is also required that there are at least 1.5 candidates for each opening.

This year EDS will again be running the pilot program for one of the BoG Member-at-Large seats to be elected via the entire EDS membership. All nominees must choose to participate in either the election by EDS membership or the election by the BoG. There must be a minimum of two nominees for the seat elected by membership. If there are less than two nominees for the seat, an election by EDS membership will not be held and the candidate will be moved to the election by the BoG. All electees begin their term in office on January 1, 2016. The nominees need not be present to run for the election. In 2015, seven positions will be filled.

The election procedure begins with the announcement and Call for Nominations in the EDS Newsletter. The slate of nominees is developed by the EDS Nominations Committee and includes the non-Committee and self-nominations received. Nominees are asked to submit a two-page biographical resume and an optional 50 word personal statement in a standard format. The election for the one BoG seat voted on by the EDS membership will be done using Vote Net. Vote Net is a web based tool that allows members the opportunity to cast their ballots electronically. An e-announcement will be sent to those EDS members who have email addresses in the IEEE database prior to the election launch date. It will give the members an opportunity to indicate their preference to receive an electronic or paper ballot. By default, paper ballots are automatically printed and mailed to EDS members without email on file as well as to those that have indicated they prefer not to receive election material electronically (based upon the communication preference in their member profile).

Any EDS member who has served for a minimum of one year as an EDS Officer, Vice-President, Standing & Technical Committee Chair/ Member, Publication Editor & Chapter Chair is eligible to be nominated, unless otherwise precluded from doing so in the EDS Bylaws. All nominees must be endorsed by one BoG member, i.e., one of the four officers (President, President-Elect, Treasurer or Secretary), the Jr. or Sr. Past President or one of the 22 current BoG Members-at-Large. Self-nomination is allowed. Endorsers should send a brief email to Laura Riello stating that they would like to endorse the candidate. Please note that there is no limit to the number of candidates that a full voting BoG member can endorse.

Nominations are closed after August 1, 2015, and the biographical resumes and endorsement letters are distributed to the BoG prior to the December BoG meeting. The election is then held after the conclusion of the meeting.

Paul Yu EDS Chair of Nominations & Elections University of California at San Diego San Diego, CA, USA

#### IEEE ANNUAL ELECTION—DID YOU VOTE YET?

This is a reminder for EDS members to vote in the 2015 IEEE Annual Election for the following positions and candidates. Listed below are the positions and candidates that will appear on the 2015 IEEE Annual Election ballot.

| Position                                                                  | Candidate                                                                                                                                                                                     |