JULY 2016 VOL. 23. NO. 3 ISSN: 1074 1879

TECHNICAL BRIEFS.....

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

### TABLE OF CONTENTS

• Tunnel Field Effect Transistors: Past, Present and Future

| UPCOMING TECHNICAL MEETINGS9                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>2016 IEEE International Integrated Reliability Workshop (IIRW)</li> <li>2016 IEEE Bipolar/BiCMOS Circuits and Technology</li> </ul>                                                                                                                                                                                                                                                                                                          |

| Meeting (BCTM)                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SOCIETY NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Message from EDS President     Message from EDS Vice President of Membership<br>and Services     Message from Editor-in-Chief                                                                                                                                                                                                                                                                                                                         |

| <ul><li>EDS Board of Governors Meeting Highlights</li><li>EDS Region 8 Meeting</li></ul>                                                                                                                                                                                                                                                                                                                                                              |

| Awards and Recognitions16                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 2016 William R. Cherry Award Winner     43rd Photovoltaic Specialists Conference (PVSC) Young Professional Award Winner     Editorial 2015 IEEE T-SM Best Paper Award     2014–2015 EDS Region 9 Outstanding Student Paper Award                                                                                                                                                                                                                      |

| • EDS Members Recently Elected to IEEE Senior Member Grade                                                                                                                                                                                                                                                                                                                                                                                            |

| Call for Nominations and Election                                                                                                                                                                                                                                                                                                                                                                                                                     |

| <ul> <li>Call for Nominations – EDS Board of Governors<br/>Members-at-Large Election</li> <li>EDS Board of Governors Members-at-Large Election Process</li> <li>IEEE Election Reminder</li> <li>2017 EDS Chapter Subsidies</li> <li>Enhance Your Career with IEEE Senior Membership!</li> <li>2016 EDS Chapter of the Year Award – Call for Nominations</li> </ul>                                                                                    |

| YOUNG PROFESSIONALS                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| • EDS Webinars—Recent Events                                                                                                                                                                                                                                                                                                                                                                                                                          |

| • EDS-ETC Programs                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| QuestEDS                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| CHAPTER NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Reflections from EDS Malaysia Chapter     EDS South Asia Chapter Chair Meeting                                                                                                                                                                                                                                                                                                                                                                        |

| MQs, DLs and Conference Reports                                                                                                                                                                                                                                                                                                                                                                                                                       |

| EDS Mini-Colloquium Held in Grenoble, France     Mini-Colloquium Held at Tokyo Institute of Technology     AP/ED Bombay Chapter Mini-Colloquium     ED NIST Student Chapter Mini-Colloquium     ED Bhubaneswar-Kolkata Chapter Mini-Colloquium     Distinguished Lecture at ED IIT Roorkee Student Chapter     Distinguished Lecture at ED Taipei (Hsinchu) Chapter and ED NCTU Student Chapter     EDS Distinguished Lecture at ED Peking University |

| Student Chapter  Report on China SemiconductorTechnology International Conference (CSTIC 2016)  Report on 22nd IPFA                                                                                                                                                                                                                                                                                                                                   |

| REGIONAL NEWS37                                                                                                                                                                                                                                                                                                                                                                                                                                       |

EDS MEETINGS CALENDAR......48

### TECHNICAL BRIEFS

### TUNNEL FIELD EFFECT TRANSISTORS: PAST, PRESENT AND FUTURE

MAYANK SHRIVASTAVA AND V. RAMGOPAL RAO

### Why Tunnel FETs?

The answer to this question is linked with breakdown of Moore's law and Dennard's scaling theory. In the last two decades, MOS technology has seen a significant progress in terms of scaling down from sub-micron feature sizes to sub-10 nm dimensions. To give a quantitative feel, the gate length, gate dielectric thickness and junction depth have been reduced by about three orders of magnitude in the past 20 years, which has significantly improved the power-performance metrics. However, in recent times, the scaling pace has slowed down - for example, a 11 nm technology node doesn't have 11 nm gate length devices anymore. The minimum gate lengths are still around 20-24 nm. This is attributed to an increased S/D leakage, weak gate control and higher power consumption at very short gate lengths. To address this, power supply  $(V_{pp})$ scaling is desired; however, to meet the ON current requirements, i.e. performance targets, the threshold voltage needs to be scaled along with VDD. However, leakage current increases exponentially as threshold voltage is reduced. Hence, threshold voltage has become a non-scalable parameter, as any decrease of threshold voltage exponentially increases the leakage current, which is mainly because of MOSFET's fundamental limit of subthreshold swing (60 mV/dec at room temperature). In reality, owing to the short channel effects, subthreshold swing (SS) is far worse than the ideal value of 60 mV/decade.

Around the same time when Dennard's scaling theory practically became difficult to implement (late 90's), a significant increase in requirement for low power technologies for wireless and handheld applications was seen. The surge in handheld consumer electronic devices like smart phones, smart watches and tablet PCs requires

(continued on page 3)

### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

# SOCIETY

### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

### **President-Elect**

Fernando Guarin GlobalFoundries

E-mail: fernando.guarin@ieee.org

### Treasurer

Subramanian S. Iyer UCLA E-mail: iyer@ieee.org

### Secretary

Simon Deleonibus CEA-LETI

E-mail: simon.deleonibus.1992@

ieee.org

### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

### Sr. Past President

Paul K.L. Yu

University of California at San Diego E-mail: p.yu@ieee.org

# Vice President of Membership and Services

Tian-Ling Ren Tsinghua University

E-mail: rentl@mail.tsinghua.edu.cn

### Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: hmomose@ynu.ac.jp

### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

### Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

### IEEE Newsletters

Theresa Smith

IEEE Operations Center

E-mail: tlsmith@ieee.org

### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

### Membership Administrator

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2016                                                                                             | TERM                                          | <u>2017</u>                                                                                             | TERM                                                 | 2018                                                                                                | TERM                                          |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) | Z. Celik-Butler<br>S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose<br>T.L. Ren | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) | N. Bhat<br>D. Camacho Montejo<br>S. Deleonibus<br>M. leong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) |

# NEWSLETTER EDITORIAL STAFF

### **Editor-In-Chief**

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

### **REGIONS 1-6, 7 & 9**

Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

### Central USA & Canada (Regions 4 & 7)

Karim S. Karim University of Waterloo E-mail: kkarim@uwaterloo.ca

### Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

### REGION 8

### Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

### Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

### **UK, Middle East & Africa**

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

# REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malavsia

E-mail: susi@ukm.edu.my

### **Northeast Asia**

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

### East Asia

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either the Editor-in-Chief or appropriate Editor. The e-mail addresses of these individuals are listed on this page. Whenever possible, e-mail is the preferred form of submission.

### Newsletter Deadlines

| <u>Issue</u> | Due Date    |

|--------------|-------------|

| January      | October 1st |

| April        | January 1st |

| July         | April 1st   |

| October      | July 1st    |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2016 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

**FPO**

### TUNNEL FIELD EFFECT TRANSISTORS

(continued from page 1)

minimization of active as well as static power dissipation by scaling down the supply voltage below 0.5 V, while maintaining acceptable performance targets. It was therefore well accepted that, in order to reduce the leakage current and scale supply voltage, it is important to explore new device structures, which can offer subthreshold swing values below 60 mV/ decade. MOSFET devices, which work on the principle of thermionic injection of carriers from source to channel, do not offer enough design space and therefore limit the supply voltage scaling. To account for the future roadmap, several CMOS like devices such as the Nanowire Gate All Around (GAA) MOSFETs, FinFETs, carbon nanotube field effect transistor (CNT-FET), Impact ionization FETs (I-MOS-FET), and TFETs were demonstrated by various groups, in order to minimize the short channel effects (SCE) and to lower the source-drain leakage current. Among these devices, only TFET and I-MOSFET promise a SS less than 60 mV/dec and improved short channel performance, which is attributed to fundamentally a different mechanism used for carrier injection from source to channel. However, given the fact that I-MOSFET requires very high voltage operation, TFET is the only promising solution available beyond FinFET and Nanowire FETs. Tunnel FET fundamentally offers a very steep sub-threshold slope, thereby allowing threshold voltage and  $V_{\scriptscriptstyle {

m DD}}$ scaling beyond CMOS limits without affecting the static leakage and ON currents.

### **Quick Review**

In last 15 years there have been extensive investigations on Tunnel FET devices for ultra-low power and high performance operation. Tunnelling phenomena allows sub-60 mV subthreshold operation thereby has a

potential to scale leakage and improve ON current at lower supply voltages. The very early TFET concept of gated Pi-N diode configuration, despite several advancements like SiGe source, Low-k drain spacer, high-k source spacer, low drain doping, highly doped source, abrupt source junction profiles, post silicidation implant, band gap engineering and double gate architectures, suffered from extremely low ON currents. This was primarily attributed to limited tunnelling cross-section/area available in gated P-i-N diodes (also known as point tunnelling FETs) [1]-[9]. To overcome this problem, vertical tunnelling [10], [11]/area scaled tunnelling [12], [13] / line tunnelling [14]–[16] devices were proposed, which theoretically show significantly improved ON current, reduced leakage and subthreshold swing which can be attributed to an increased tunnelling cross section and gate-field aligned binary tunnelling mechanism [17], [18]. However, there are still open concerns related to TFET design in terms of dealing with trap assisted tunnelling (TAT) [19] and diffused junction profiles [20], which adversely affect the ON current and cause an increased leakage and SS of area scaled tunnelling or vertical tunnelling devices.

### **Circuit Advantages**

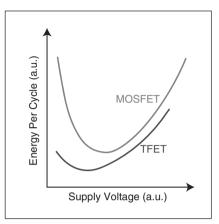

As mentioned above, higher SS limits the supply voltage scaling, which further increases the power dissipation ( $\alpha I_{\it OFF}$  ·  $V_{\it DD}^3$ ). Higher power dissipation at shorter channel lengths necessitates supply reduction, which however is limited by higher SS. To reduce the SS and thereby allow supply voltage scaling, one requires relying on carrier injection methods other than thermionic injection. A sub-thermionic injection device is expected to offer better energy performance compared to MOSFETs, as depicted in Fig. 1 [21].

Fig. 1. Energy consumption per cycle as a function of supply voltage for MOSFET and TFET devices [21].

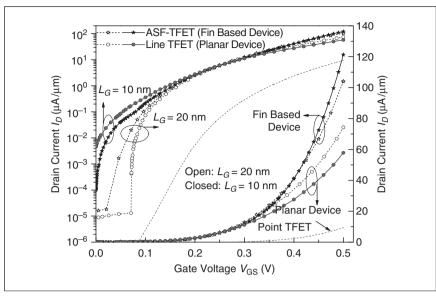

Fig. 2. Input characteristics of various switching devices [28].

Figure 2 compares the input characteristics of some of the potential candidates for sub-thermionic operation. These are NEMS switches [22], Negative capacitance FET (NCFET), Impact Ionization FET (I-MOSFET) [24] and Tunnel FET. NCFETs and I-MOSFET require a certain minimum voltage for their adequate operation and thereby do not allow supply voltage scaling beyond a certain point. Tunnel FET so far is the most promising alternative for supply voltage reduction while maintaining steep sub-threshold slope. It has potential

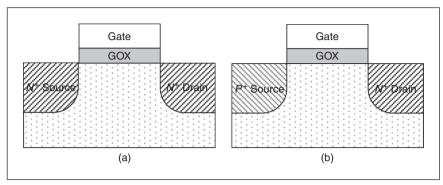

Fig. 3. Schematic view of (a) MOSFET and (b) TFET devices.

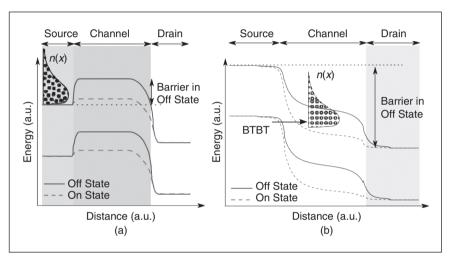

Fig. 4. Energy band diagram of (a) MOSFET and (b) TFET in ON and OFF states, depicting fundamental difference between thermionic injection mechanism and band to band tunnelling.

Fig. 5. Functional and structural difference (a) Line TFET and (b) Line TFET. The arrows and their density depict the tunnelling path and tunnel cross sectional area, respectively.

to offer low static leakage and adequate ON current even at lower supply voltages, which minimises power dissipation without sacrificing the performance. It also combats various short channel effects such as DIBL [30], hot carrier effects [34] even at shorter channel lengths, which makes it a potential candidate for future technology nodes.

### **How Tunnel FET Works?**

A. Fundamental Principle: Figure 3 compares cross sectional view of a MOSFET and TFET. The only difference is in the way the source region is engineered, which in fact defines the carrier injection from source to channel. In principle a TFET is a gated p-i-n diode which behaves like a tunnel diode in ON state and like a

reverse bias P-i-N diode under OFF state. Asymmetry in the structure and tunnel injection of carriers allows very high I<sub>ON</sub>/I<sub>OFF</sub>; however, it restricts the source-drain exchange, which works well in case of MOSFET.

Figure 4 compares the operational difference between Tunnel FET and MOSFET. In case of MOSFET, carriers are injected thermionically over the barrier, whereas in case of TFET they are injected from source to channel due to gate field induced band to band tunnelling (BTBT). In the OFF state, alignment between the conduction band of the channel and the valence band of the source is missing, which avoids carrier tunnelling and maintains a very low leakage current. However, in the ON state, when the gate field is present, the channel region's conduction band is pulled down, which allows it to align with the source region's valance band. This alignment reduces the tunnelling barrier width and height, which allows carrier injection/tunnelling from source to channel region. This enables a sharp turn-on when the bands are aligned, and therefore allows TFET devices to operate well below the sub-thermionic limits with sub-threshold swing values below 60 mV/dec. Under OFF state condition, TFET has comparatively higher barrier for the minority carriers, which leads to negligible leakage current due to minority carrier injection. In fact whatever leakage current exists in TFET is mostly dominated by SRH recombination and trap assisted tunnelling (TAT) [25] at the sourcechannel junction, which however, are well below leakage in MOSFET devices at shorter channel lengths.

# B. Point TFET versus Area Scaled TFET: Despite its ability to combat short channel effects, enable voltage scaling and minimise leakage, the conventional/gated P-i-N TFET architectures suffer from their low ON current. In recent literature, this device is frequently referred as point TFET (Fig. 5a). ON current of TFET is directly proportional to the tunnelling

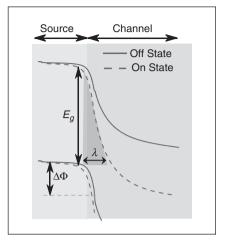

probability  $(T_{RTRT})$  and tunnelling cross-section. The expression for the tunnelling probability obtained by approximating the tunnel barrier by a triangular barrier, as shown in Figure 6, and using WKB approximation is given by [35]:

$$egin{align} T_{ extit{BTBT}} &= \exp\Biggl( -rac{4\lambda\sqrt{2m*E_g^3}}{3qh\Bigl(E_g+\Delta\Phi\Bigr)} \Biggr) \ &pprox \exp\Biggl( -rac{4\sqrt{2m*E_g^3}}{3qhF} \Biggr) \ \end{aligned}$$

Where m\* is the effective tunnelling mass,  $E_a$  is the bandgap of the material, F is the electric field and  $\lambda$  is the tunnelling distance. For pointTFET, the only parameter which one can engineer is to use the low bandgap material with low tunnelling effective mass. This improves the tunnelling probability and improves the ON current; which however is at the cost of increased SRH leakage. To keep the SRH leakage under control, use of low bandgap material only at the tunnel junction is a technique which is implemented widely. Except at the tunnelling junction (low bandgap source region for N-type device and low bandgap channel region for P-type device), rest of the device uses a relatively higher bandgap material, which is also known as hetero-junction TFET. Other methods which were proposed to improve point TFET's performance were use of Low-k drain spacer, high-k source spacer, low drain doping, highly doped source, abrupt source junction profiles, post silicidation implant, and double gate architectures. However, they all suffer from extremely low ON currents, which is attributed to limited tunnel area available. This issue was addressed by increasing tunnelling cross section area, by introducing vertical tunnelling [10], [11] in the direction of gate field [17], [18] by incorporating a N-type pocket sandwiched between gate stack and P+ source (Fig. 5b). This concept is also known as area scaled tunnelling [12], [13] or line tunnelling [14]-[16], which significantly improves the ON current, subthreshold slope and gate control over the tunnelling junction.

Pocket layer design and source engineering plays a very important role in lineTFET's performance. The design parameters are source and pocket layer's doping and bandgap, as well as pocket region's thickness [12]. One can say that the pocket engineering leverages additional control to design device for a range of applications. It is worth mentioning that lineTFET architecture is CMOS compatible and easy to integrate using standard CMOS unit process steps [13].

### **TFET Future Beyond FinFET: Fin Enabled Area Scaled TFET**

It took almost 20 years for FinFET technology to mature and become a reality

Fig. 6. Energy band bending, tunnelling barrier height and tunnelling distance at the sourcechannel junction under ON and OFF states of the device

for semiconductor products by replacing planar devices. However, as technology evolution doesn't allow abrupt changes, FinFETs too enjoy advancements from planar nodes like High-k metal gate, raised/epi source-drain, strained silicon and gate last process. It is widely accepted that Si or SiGe FinFET can be replaced by TFETs, but what was not so clear was whether there will be a serious change in technological evolution while scaling below 7 nm nodes. In other words how to takeTFET concept to Fin-based technologies, allowing smooth transition from FinFET technology to Fin-based vertical Tunnel FETs, while enjoying benefits of FinFET architecture.

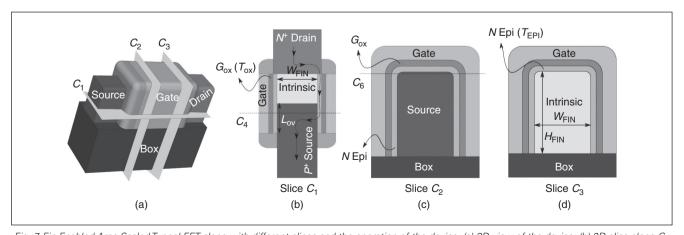

Fig. 7. Fin Enabled Area Scaled Tunnel FET along with different slices and the operation of the device. (a) 3D view of the device; (b) 2D slice along C, depicting paths followed by the carrier from source to drain; (c) & (d) 2D views along the slices C, and C,

Fig. 8. Input characteristics Point TFET, Line TFET and ASF-TFET [25].

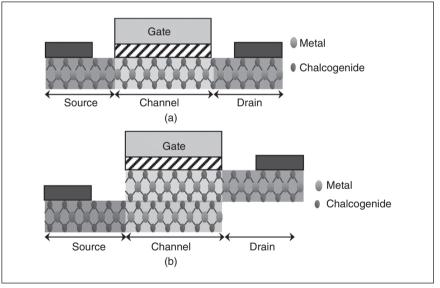

Fig. 9. Schematic of TMDC based (a) point TFET and (b) Line TFET.

To address this, a Fin Enable Area Scaled Tunnel FET namely ASF-TFET was recently proposed [25], as depicted in Fig. 7. The working principle of this device is same as lineTFETs, however the device enjoys excellent gate control over the channel as well as the tunnel junction, which improves the performance significantly [36], as depicted in Fig. 8. According to simulated results, ASF-TFET at 10 nm gate length, when compared to the conventional vertical tunnelling FET or planar area scaled device, offers 100%

improvement in ON current, 15× reduction in OFF current, 3× increase in the transconductance, 30% improvement in output resistance, 55% improvement in the unity gain frequency and more importantly 6× reduction in the footprint area for a given drive capability. Furthermore, the proposed device brings the average and minimum sub-threshold swing (SS) down to 40 mV/dec and 11 mV/dec at 10 nm gate length. This gives a path for beyond FinFET System on Chip (SoC) applications while enjoying

analog, digital and RF performance improvements [25].

### TFET Beyond Conventional Semiconductors: 2D Material Based Hetero-Structure TFET

In recent years 2D materials like Graphene, Hexagonal Boron Nitride (h-BN) and Transition metal dichalcogenides (TMDC) have seen extensive investigations for electronics applications. These investigations revealed greater potential of 2D materials for low power SoC products, which is attributed to (i) their extraordinary channel properties, (ii) atomically thin channel, which allows excellent gate control and hence scalability beyond Si limits and (iii) flexible nature of 2D materials which allows integration over flexible substrates [26]-[29]. Moreover, the 2D material surfaces are extremely flat and free of defects, which potentially offer improved device reliability [19]-[20]. Like conventional semiconductors, various groups have been exploring TFET possibilities using 2D materials as well (Fig. 9) [30]-[33]. Initial results depict a great potential of TMDC based tunnel FET, which is attributed to excellent gate control over the tunnel junction, scalability, broken gap TFET architecture and absence of TAT leakage; however, the technology still has a long road ahead, as far as meeting the semiconductor industry roadmap targets is concerned.

### References

[1] T. Krishnamohan, D. Kim, S. Raghunathan, and K. Saraswat, "Double gate strained-Ge heterostructure tunneling FET (TFET) with record high drive currents and <60 mV/dec subthreshold slope," *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2008, pp. 1–3.

[2] G. Dewey et al., "Fabrication, characterization, and physics of III–V heterojunction tunneling field effect transistors (H-TFET) for steep sub-threshold swing," *Proc. IEEE Int. Electron Devices Meeting (IEDM)*, Dec. 2011, pp. 33.6.1–33.6.4.

- [3] K. Tomioka, M. Yoshimura, and T. Fukui, "Steep-slope tunnel field effect transistors using III-V nanowire/ Si heterojunction," Proc. Symp. VLSI Technol. (VLSIT), Jun. 2012, pp. 47-48.

- [4] Q. T. Zhao et al., "Tunneling field-effect transistor with a strained Si channel and a Si<sub>0.5</sub>Ge<sub>0.5</sub> source," Solid-State Electronics, vol. 74, pp. 97-101, Aug. 2012.

- [5] S. H. Kim, H. Kam, C. Hu, and T.-J. K. Liu, "Germanium-source tunnel field effect transistors with record high  $I_{ON}/I_{OFF}$ ," VLSI Technology Symposium, June 2009, pp. 178-179.

- [6] K. K. Bhuwalka, J. Schulze, and I. Eisele, "Vertical tunnel field-effect transistor with bandgap modulation and workfunction engineering," 34th European Solid-State Device Research Conf. (ESSDERC), Sep. 2004, pp. 241-244.

- [7] J. T. Smith, S. Das, and J. Appenzeller, "Broken-gap tunnel MOS-FET: A constant-slope sub-60-mV/ decade transistor," IEEE Electron Device Letter, Vol. 32, No. 10, pp. 1367-1369, Oct. 2011.

- [8] E. Yu, L. Wang, Y. Taur, and P. Asbeck, "Design of tunneling field effect transistors based on staggered hetero junctions for ultralow-power applications," IEEE Electron Device Letters, vol. 31, no. 5, pp. 431-433, May 2010.

- [9] N. Patel, A. Ramesha, and S. Mahapatra, "Drive current boosting of n-type tunnel FET with strained SiGe layer at source," Microelectronic Journal, vol. 39, no. 12, pp. 1671-1677, Dec. 2008.

- [10] K. Ganapathi, Y. Yoon, and S. Salahuddin, "Analysis of InAs vertical and lateral band-to-band tunneling transistors: Leveraging vertical tunnelling for improved performance," Appl. Phys. Letters, Vol. 97, no. 3, p. 033504, 2010.

- [11] L. Lattanzio, N. Dagtekin, L. De Michielis, and A. M. Ionescu," On the static and dynamic behavior of the germanium electron-hole bilayer tunnel FET," IEEE Trans. Electron Devices, vol. 59, no. 11, pp. 2932-2938, Nov. 2012.

- [12] A. Rajoriya, M. Shrivastava, H. Gossner, T. Schulz, and V. R. Rao,

- "Sub 0.5 V operation of performance driven mobile systems based on area scaled tunnel FET devices," IEEE Trans. Electron Devices, vol. 60,no. 8, pp. 2626-2633, Aug. 2013.

- [13] R. Asra, M. Shrivastava, K. V. R. M. Murali, R. K. Pandey, H. Gossner, and V. Ramgopal Rao, "A tunnel FET for VDD scaling below 0.6 V with a CMOS-comparable performance," IEEE Trans. Electron Devices, vol. 58, no. 7, pp. 1855-1863, Jul. 2011.

- [14] A. M. Walke et al., "Fabrication and analysis of a Si/Si $_{0.55}$ Ge $_{0.45}$  heterojunction line tunnel FET," IEEE Trans. Electron Devices, vol. 61, no. 3, pp. 707-715, Mar. 2014.

- [15] I. A. Fischer et al., "Silicon tunneling field-effect transistors with tunneling in line with the gate field," IEEE Electron Device Letters, vol. 34, no. 2, pp. 154-156, Feb. 2013.

- [16] K.-H. Kao et al., "Optimization of gate-on-source-only tunnel FETs withcounter-doped pockets," IEEE Trans. Electron Devices, vol. 59, no. 8, pp. 2070-2077, Aug. 2012.

- [17] C. Hu et al., "Prospect of tunneling green transistor for 0.1 V CMOS," in Proc. IEEE Int. Electron Devices Meeting, Dec. 2010, pp. 16.1.1-16.1.4.

- [18] R. Asra, K. V. Murali, and V. R. Rao, "A binary tunnel field effect transistor with a steep sub-threshold swing and increased on current," Jpn. J. Appl. Phys., vol. 49, no. 12R, p. 120203, 2010.

- [19] X. Y. Huang et al., "Effect of interface traps and oxide charge on drain current degradation in tunneling field-effect transistors," IEEE Electron Device Letters, vol. 31, no. 8, pp. 779-781, Aug. 2010.

- [20] A. Vandooren, D. Leonelli, R. Rooyackers, K. Arstila, G. Groeseneken, and C. Huyghebaert, "Impact of process and geometrical parameters on the electrical characteristics of vertical nanowire silicon n-TFETs," Solid-State Electron., vol. 72, pp. 82-87, June 2012.

- [21] A. M. Ionescu and H. Riel, "Tunnel field-effect transistors as energy efficient electronic switches," Na-

- ture, vol. 479, no. 7373, pp. 329-337, Nov. 2011

- [22] Kam, Hei, Donovan T. Lee, Roger T. Howe, and Tsu-Jae King, "A new nano-electro-mechanical field effect transistor (NEMFET) design for low-power electronics," In Electron Devices Meeting, 2005. IEDM Technical Digest. IEEE International, pp. 463-466. IEEE, 2005.

- [23] Salahuddin, Saveef, and Supriyo Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," Nano letters 8, no. 2 (2008): 405-410.

- [24] Gopalakrishnan, Kailash, Peter B. Griffin, and James D. Plummer, "I-MOS: a novel semiconductor device with a subthreshold slope lower than kT/q," In Electron Devices Meeting, 2002. IEDM'02. International, pp. 289–292. IEEE, 2002.

- [25] K. Hemanjaneyulu and M. Shrivastava, "Fin Enabled Area Scaled Tunnel FET," in IEEE Transactions on Electron Devices, vol. 62, no. 10, pp. 3184-3191, Oct. 2015.

- [26] Novoselov, K. S. A., Andre K. Geim, et. al., "Two-dimensional gas of massless Dirac fermions in graphene," nature 438, no. 7065 (2005): 197-200.

- [27] Zhang, Yuanbo, Yan-Wen Tan, Horst L. Stormer, and Philip Kim, "Experimental observation of the quantum Hall effect and Berry's phase in graphene," Nature Vol. 438, Issues: 7065, 2005, pp: 201-204.

- [28] Novoselov, Kostya S., Andre K. Geim, et. al., "Electric field effect in atomically thin carbon films," Science Vol. 306, Issue: 5696, 2004, pp: 666-669.

- [29] Nirschl, Th, J. Fischer, M. Fulde, A. Bargagli-Stoffi, M. Sterkel, J. Sedlmeir, C. Weber et al, "Scaling properties of the tunneling field effect transistor (TFET): Device and circuit," Solid-state electronics, Vol. 50, No. 1, 2006, pp: 44-51.

- [30] Ghosh, Ram Krishna, and Santanu Mahapatra, "Monolayer transition metal dichalcogenide channelbased tunnel transistor," IEEE Journal

of the Electron Devices Society, Vol. 1, No. 10, 2013, pp: 175-180.

[31] Ilatikhameneh, Hesameddin, Yaohua Tan, Bozidar Novakovic, Gerhard Klimeck, Rajib Rahman, and Joerg Appenzeller, "Tunnel field-effect transistors in 2-D transition metal dichalcogenide materials," IEEE Journal on Exploratory Solid-State Computational Devices and Circuits, Vol. 1, 2015, pp: 12-18.

[32] Sarkar, Deblina, Xuejun Xie, Wei Liu, Wei Cao, Jiahao Kang, Yongji Gong, Stephan Kraemer, Pulickel M. Ajayan, and Kaustav Banerjee, "A subthermionic tunnel field-effect transistor with an atomically thin channel," Nature, Vol. 526, No. 7571, 2015, pp: 91-95.

[33] Roy, Tania, Mahmut Tosun, Xi Cao, Hui Fang, Der-Hsien Lien, Peida Zhao, Yu-Ze Chen, Yu-Lun Chueh, Jing Guo, and Ali Javey, "Dual-Gated MoS2/WSe2 van der waals tunnel diodes and transistors," ACS Nano Vol. 9, No. 2, 2015, pp: 2071-2079.

[34] A. C. Seabaugh and Q. Zhang, "Low-Voltage Tunnel Transistors for Beyond CMOS Logic," Proceedings of the IEEE, Vol. 98, No. 12, pp: 2095-2110. Dec. 2010.

[35] Sze, Simon Min, Semiconductor devices: physics and technology". John Wiley & Sons, 2008.

[36] Qin Zhang, Wei Zhao and A. Seabaugh, "Low-subthreshold-swing tunnel transistors," in IEEE Electron Device Letters, vol. 27, no. 4, pp. 297-300, April 2006.

Mayank Shrivastava is an Assistant Professor in the Department of Electronic Systems Engineering, Indian Institute of Science Bangalore, India. Prof.

Shrivastava has over 50 publications in international journals and conferences and 26 patents in the areas of Electron Devices and Nanoelectronics. He was among the first recipient of Indian section of American TR35 award and the recipient of IEEE EDS Early Carrier Award for year 2015. In addition to this he has received several other awards and honours including excellence award for his PhD thesis in 2010 and industrial impact award from IIT Bombay in 2008.

Prof. Shrivastava had held short term visiting positions in Infineon Technologies, Munich, Germany from April 2008 to October 2008 and again in May 2010 to July 2010. He worked for Infineon Technologies, East Fishkill, NY; Intel Mobile Communications, Hopewell Junction. NY; and Intel Corp., Mobile and Communications Group, Munich, Germany between 2010 and 2013. He joined Indian Institute of Science as an Assistant professor in year 2013 where he has established Advance Nanoelectronic Device and Circuit Research Group.

To get more information about Prof. Shrivastava's current research interests, publications and patents visit: http://www.dese.iisc.ernet.in/people/ mayank/.

V. Ramgopal Rao was a P. K. Kelkar Chair Professor for Nanotechnology in the Department of Electrical Engineering and the Chief Investigator for

the Centre of Excellence in Nanoelectronics project at IIT Bombay. He is currently on lien from IIT Bombay to serve as a Director at IIT Delhi. Dr. Rao has over 400 publications in the area of Electron Devices &Nanoelectronics in refereed international journals and conference proceedings and is an inventor on 32 patents (including 13 issued US patents) and patent applications, with many of his patents licensed to industries for commercialization. He is also a co-founder of the company NanoSniff Technologies

Pvt. Ltd. at IIT Bombay which is developing products in the area of Nanotechnology.

Prof. Rao's work is recognized with many awards and honors in the country and abroad. He is a recipient of the Shanti Swarup Bhatnagar Prize in Engineering Sciences in 2005 and the Infosys Prize in 2013. Dr. Rao also received the Swarnajayanti Fellowship award from the Department of Science & Technology, IBM Faculty award, Best Research award from the Intel Asia Academic Forum, Techno-Mentor award from the Indian Semiconductor Association, DAE-SRC Outstanding Research Investigator award, NASI-Reliance Platinum Jubilee award, J.C.Bose National Fellowship, Prof. C.N.R.Rao National Nanoscience award and the Excellence in Research Award from IIT Bombay. Prof. Rao was an Editor for the IEEE Transactions on Electron Devices during 2003-2012 for the CMOS Devices and Technology area and currently serves on the Editorial boards of various other international journals. Dr. Rao is a Fellow of the Indian National Academy of Engineering, Indian Academy of Sciences, National Academy of Sciences, and the Indian National Science Academy. He is a Distinguished Lecturer, IEEE Electron Devices Society and interacts closely with many semiconductor industries including Intel, IBM, Infineon, Applied Materials, Maxim and Texas Instruments.

Dr. Rao served as a Chairman, IEEE AP/ED Bombay Chapter and is currently the Vice-President, Materials Research Society of India. He also served as a Vice-Chairman, IEEE Asia Pacific Regions/Chapters sub-committee during 2007-2013 and was the first elected Chairman for the India section, American Nano Society during 2013-2015.

For more information about Prof. Rao's current research interests and a list of publications visit: http:// www.ee.iitb.ac.in/~rrao/

## UPCOMING TECHNICAL MEETINGS

### 2016 IEEE INTERNATIONAL INTEGRATED RELIABILITY WORKSHOP (IIRW)

The 2016 IEEE International Integrated Reliability Workshop (IIRW), sponsored by the IEEE Reliability Society and the IEEE Electron Devices Society, will be held at the Stanford Sierra Conference Center on the shores of Fallen Leaf Lake near South Lake Tahoe, California, October 9-13, 2016. This workshop provides a unique forum for open, lively discussions of all areas of reliability research and technology for present and future semiconductor applications.

Reliability topics for the workshop include: SiGe and strained Si, III-V, SOI, high-k and nitrided SiO, gate dielectrics, reliability assessment of novel devices, Power devices reliability (SiC, GaN), organic electronics, emerging memory technologies (RRAM etc.) and future "nano"-technologies, NEMS/MEMS, photovoltaics, transistor reliability including hot carriers and NBTI/PBTI, Cu interconnects and low-k dielectrics, product reliability and burn-in strategy, impact of transistor degradation on circuit reliability, reliability modeling

and simulation, optoelectronics, single event upsets, array testing as well as the traditional topics of wafer level reliability (WLR) and buildingin reliability (BIR). Special focus this year will be on MEMS and other sensor reliability, atomic and molecular scale modeling for reliability, and advanced characterization techniques for reliability studies.

The Call for Papers can be found at www.iirw.org. Please submit abstracts though www.iirw.org. The submission deadline is July 11, 2016. Contact the Technical Program Chair, Tom Kopley (tpc.iirw2016@gmail. com) for any further questions or visit www.iirw.org for continued updates about the conference.

IIRW is guite different from a typical technical conference. Located 6400 feet above sea level in the California Sierra Nevada, the Stanford Sierra Conference Center provides an ideal atmosphere for a relaxing yet informative workshop. All aspects of the workshop, including the physical isolation of the location, the absence of distractions such as in-room phone/ television, and the format of the technical program, encourages extensive interaction among the workshop attendees. You feel yourself drawn into technical discussions from the start.

Attendees lodge in cabins nestled throughout the pines and cedars along the shoreline of Fallen Leaf Lake. All rooms have decks with magnificent views of Fallen Leaf Lake and the surrounding Sierra peaks. Comfortable, informal dress is encouraged, affiliations are downplayed, and meals are provided family-style in the lodge dining room. This peaceful setting presents a terrific opportunity to get to know your colleagues, including internationally renowned experts. Such opportunity is seldom available at larger conferences. Participants spend their evenings at poster sessions, discussion groups, and special interest groups, all complemented with refreshments and snacks. At the end of the day, attendees are free to relax in front of a roaring fireplace in the rustic Old Lodge.

Aerial view of the Stanford Sierra Conference Center - The Center provides lodging, meals and meeting facilities as well as excellent recreational opportunities, including hiking in the Desolation Wilderness and boating on Fallen Leaf Lake

The conference traditionally begins Sunday evening after the majority of attendees arrive. The single Sunday night talk includes refreshments, and is designed for the weary traveler, being a technically toned-down presentation on an interesting topic either peripherally related to reliability, or simply an interesting hobby or business from one of the attendees. This year we are delighted to announce this Sunday night talk will be on the applications of sensor fusion for motion tracking by Per Slyke, VP of Fairchild's Motion Tracking product line.

Invited speakers at this year's IIRW will include Roya Maboudian (UC Berkeley) on MEMS reliability, Stuart Friedman (PrimeNano) on scanning microwave impedance microscopy, Ashraf Alam (Purdue U.) on polymer dielectric reliability, Don Gajewski (Wolfspeed, CREE) on SiC reliability, Gaudenzio Meneghesso (U. Padova) on GaN reliability, and Kevin Huang (TSMC) on AC stress for standard cell aging characterization, among several others.

Another advantage of attending IIRW is the extensive collection of tutorials, presented by leading experts and included at no additional cost. This year the tutorials cover diverse reliability topics such as BEOL reliability (Patrick Justison, Globalfoundries), SiC power device reliability (Kevin Matocha, Monolith Semi), MEMS reliability (Allyson Hartzell, |Veryst), and DFT defect modeling in SiO<sub>2</sub> and HfO<sub>2</sub> dilectrics (Al-Moatasem El-Sayed, UCL). Please check the IIRW website for updates on tutorial presenters.

One other advantage of IIRW is the moderated discussion groups that are held in the evenings. Following up on the discussion groups are the Special Interest Groups, which are composed of small groups of attendees who want to continue their discussions on a particular topic of interest, which often continue even after the workshop.

One unique aspect of the workshop is the opportunity for any attendee to present a walk-in poster of their latest work. Finally, attendees have Wednesday afternoon off to enjoy a variety of outdoor activities such as hiking, volleyball, sailing or kayaking, biking, walking, or simply continuing that intriguing conversation from the night before. This free afternoon is a great way to not only network, but also to build long-lasting friendships.

Additional information about the workshop is available on the IIRW website at www.iirw.org, or by contacting Richard G. Southwick, III, 2016 IIRW General Chair, (southwick@us.ibm.com). Information on the Stanford Camp is available at stanfordsierra. com. Note: If you want to take part in this event, please register early as space at the Stanford Sierra Conference Center is limited to roughly 120 attendees and the workshop has sold out in the past.

On behalf of the 2016 IIRW Management Committee, I look forward to meeting you in Lake Tahoe!

Zakariae Chbili 2016 IIRW Communications Chair GLOBALFOUNDRIES, Inc. Malta, NY, USA

The IEEE Journal of Electron Devices Society (J-EDS) is a peer-reviewed, open-access, fully electronic scientific journal publishing papers ranging from applied to fundamental research that are scientifically rigorous and relevant to electron devices.

Please submit your manuscripts for consideration of publications in J-EDS at <a href="http://mc.manuscriptcentral.com/jeds">http://mc.manuscriptcentral.com/jeds</a>.

The J-EDS publishes original and significant contributions relating to the theory, modelling, design, performance, and reliability of electron and ion integrated circuit devices and interconnects, involving insulators, metals, organic materials, micro-plasmas, semiconductors, quantum-effect structures, vacuum devices, and emerging materials with applications in bioelectronics, biomedical electronics, computation, communications, displays, microelectromechanics, imaging, micro-actuators, nano-devices, optoelectronics, photovoltaics, power IC's, and micro-sensors. Tutorial and review papers on these subjects are, also, published.

As an open-access title J-EDS provides the electron devices community:

- Faster speed of publication;

- Free access to readers globally;

- Worldwide audience;

- Increased dissemination:

- High impact factor (IF),

- Articles can be cited sooner;

- Articles potentially cited more frequently.

### 2016 IEEE BIPOLAR/BICMOS CIRCUITS AND TECHNOLOGY MEETING (BCTM)

SHORT COURSE: SEPTEMBER 25, 2016; CONFERENCE: SEPTEMBER 26-27, 2016

On behalf of the IEEE BCTM'16 Executive Committee, we are honored and delighted to invite you to the 2016 IEEE Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) at the beautiful Hyatt Regency, New Brunswick, New Jersey, USA, from September 25th-27th. We invite you to participate at the 2016 BCTM where the highlights include:

- Day-long short-course on Advances in Design Enablement for RF and High Performance **Analog Circuit Design**

- Dr. Sharad Kapur (Integrand Software): Advanced EM Simulation

- Art Schaldenbrand (Cadence): Developments in EDA tools for analog design

- Dr. Ali Niknejad (UC Berkeley): Modeling of Passives at High Frequencies

- Dr. Shahriar Shahramian (Bell Labs): Circuit design point of view on EM Simulation, EDA tools, and modeling

- Invited papers exploring advances in analog/mixed-signal design, device physics, modeling and simulation, process

Doug Weiser

Foster Dai

technology, and wireless desian

- Technical papers covering the latest advances in physics, design, performance, fabrication, characterization, modeling, and application of Si/SiGe/ SiC bipolar, BiCMOS, and GaN ICs

- · Evening dinner banquet

The IEEE BCTM is a forum for technical communication focused on the needs and interests of the bipolar and BiCMOS community. Papers covering the design, modeling, performance, fabrication, testing and application of bipolar and BiCMOS integrated circuits and devices as well as high-performance circuits using other competitive technologies such as CMOS, SiC, GaN, GaAs, and InP are solicited.

Best Paper Awards will be given to the top regular and student papers. A Special Section of the IEEE Journal of Solid-State Circuits will include selected papers from BCTM 2016.

### **General Contact Information**

Visit the conference website: www. ieee-bctm.org or contact: Catherine Shaw, Conference Manager, Phone 1-732-501-3334, E-mail: cshaw.cmpevents@gmail.com

The IEEE BCTM is the world's premier forum focused on the needs and interests of the bipolar and BiCMOS community. If you are interested in leading edge bipolar/BiCMOS devices and technology, circuits, and applications, as well as networking with experts in these areas, please kindly join us this year at the beautiful Hyatt Regency, New Brunswick, New Jersey, USA!

Foster Dai 2016 BCTM Technical Program Chair University of Auburn

> Doug Weiser 2016 BCTM General Chair Texas Instruments

### SOCIETY NEWS

### Message from EDS President

Samar K. Saha EDS President 2016–2017

Dear Fellow EDS Members:

At the onset of assuming the duties as 2016–2017 President of IEEE Electron Devices Society (EDS), in my first message in January, I stated to continue buil-

ding EDS on the excellent foundation of the past to meet the challenges of the future. Accordingly, the plans to continue ongoing activities and executions and define the future directions of our Society along with suitable outreach programs were outlined. A gist of the progress made so far in the initiated programs is in this message.

However, before summarizing the initiated EDS programs, I am happy to inform all our members that James Skowrenski joined the EDS office as the Operations Director. Jim is highly experienced and knowledgeable in working with membership-based organizations. His experience with the American Diabetes and American Medical Associations will bring new perspective in our society's day-today operations. In addition, he has a strong background in institutional publishing including executive roles with Nature Publishing and Macmillan Magazines Ltd. Jim, also managed a consulting business focusing on both association marketing and membership. Please join me in welcoming Jim to the EDS staff.

In an effort to grow and retain EDS membership, we have started implementing different strategies through EDS Membership Fee Subsidy Program and various activities of Regions and Chapters Committees.

About 600 new members have joined the EDS during the first 4 months of this year through these efforts. The details of these strategies as well as the number growth process of EDS membership will be reported in the Board-of-Governors (BoG) meetings and later in issues of this Newsletter.

Our flagship publications, the IEEE Transactions on Electron Devices (T-ED) and IEEE Electron Device Letters (EDL) are of world class by themselves and are in good shape under the new Editor-in-Chiefs (EiC) of each journal. In order to establish our worldwide leading position in Open Access (OA) publications through the IEEE Journal of Electron Devices Society (J-EDS), we are in the process of implementing several initiatives to increase the number of manuscript submission. I am also happy to inform that we have successfully completed the J-EDS Editor-in Chief (EiC) search process by the (EiC) search committee ensuing the (EiC) Selection Procedure. Professor Mikael Östling of KTH Royal Institute of Technology Sweden has been selected and appointed as the second (EiC) of the three-year old infant, J-EDS. For the healthy growth of J-EDS to maturity, we are in the process of initiating plans to integrate J-EDS in the publication loop of EDS's flagship conferences for publishing selected high-impact extended conference papers.

Besides sustaining our existing flagship conferences, we need to *expand our worldwide leading position* with respect to device and technology conferences to the geographical regions with major activities on device and technology. In this endeavour, the inaugural conference of the newly

proposed EDS's Electron Devices Technology and Manufacturing (EDTM) is scheduled at Toyama International Conference Center, Toyama, Japan on February 28 to March 2, 2017. EDTM is the resultant of a concerted effort by a dedicated team of volunteers led by Shu Ikeda as the Chair of EDTM Executive Committee. EDTM is structured to be a unique EDS's flagship conference in Asia that is intimately integrated to EDS Executive and Technical Committees along with publication process tied to the J-EDS.

With more than 190 EDS Chapters around the globe distributed in all the 10 Regions serving the members and constantly engaging with academia and industry, our target is to penetrate the young, especially students, through more active EDS student Chapters. It is extremely critical to plan the growth and development of EDS Student Chapters in academic institutions with existing IEEE chapters only. We are also pursuing the service to the community through joining in the IEEE Special Interest Group in Humanitarian Technology (SIGHT) program and promoting it through our EDS Chapters.

We are continuing our stellar educational programs including Masters Student and PhD Student Fellowships, Distinguished Lectures (DLs), Mini-Colloquia (MQ), Webinars, and so on. I am pleased to report that through April 2016, we organized two EDS Webinars of total six planned in 2016.

We have initiated reaching out to other IEEE Organizational Units (OUs) with common interest for bilateral collaboration of mutually beneficial programs as well as to outreach youth. In continuing effort to outreach to youth, EDS hosted a student event at the 43rd Photovoltaic Specialists Conference (PVSC), June 5-10, 2016, in Portland.

The first open session to discuss EDS's strategy on Future Direction program is slated in 2016 mid-year BoG meeting at Grenoble, France.

In summary, some of the programs initiated and outlined in my earlier message in the January 2016 issue of the Newsletter is shaping its results.

Details will be informed through future issues of this Newsletter.

> Samar K. Saha EDS President Prospicient Devices Milpitas, CA, USA

### Message from EDS VICE President of Membership AND SERVICES

Tian-Ling Ren EDS Vice President of Membership and Services

I am extremely honored and pleased to work as the new **EDS Vice President** Membership of and Services. EDS is one of the best societies of IEEE and members' benefits are always our primary

concerns. EDS has a steady member count of over 10,000 members. The member count was kept constant while some other societies had an obvious decline in membership. Although the result is encouraging, we

still need to do better to attract more members.

During the EDS Board of Governors Meeting (BoG) in 2015, we had an interesting discussion about how to increase the member benefits. Some of the conclusions were to continue to focus on young professionals and affiliate members, focus on on-line membership and improve the way we promote the Society at events such as EDS Distinguished Lectures (DLs) and Mini-Colloquium (MQ). We will also continue the focus on webinar offerings, which deliver live lectures with luminaries from the field of electron device engineering.

Most importantly, the success of EDS depends on you, our valuable members. Please get in touch and tell us your ideas on what you expect and want to see. You are all invited to share your ideas. You can preferably do this by e-mail to Joyce Lombardini, who is the EDS Membership Administrator, e-mail: j.lombardini@ieee.org

Sincerely yours,

Tian-Ling Ren EDS Vice President of Membership and Services Tsinghua University Beijing, China

### Message from Editor-IN-Chief

M. K. Radhakrishnan Editor-in-Chief

Dear EDS Members and Readers,

I hope you enjoy reading the information featured in this issue of the newsletter, such as the technical article discussing the research studies and

the development which led to Tunnel FET (TFET) devices. TFETs could provide solutions for one of the greatest challenges in device technology through ultra-low power consumption during transistor switching. After a se-

ries of articles on reliability trends in devices, now we are moving towards new developments in device technology. Such technical articles by experts which are so digestible to any reader is published for the benefit of all the members and readers of this Newsletter and we welcome your views and comments about them.

A summary of the deliberations at the mid-year meeting of the EDS Board of Governors held at Grenoble, France on May 29, 2016, is included in the Society News Section. Also, the announcement of various EDS awards is given in the section.

Our Regional Editors Adam Convey (Regions 5 & 6) and Mansun Chan (Region 10 - East Asia) served their terms very successfully, engaging the Chapters and activities in their respective Regions. On behalf of all our readers and the EDS Newsletter team, I would like to express our sincere gratitude to both of them. Thank you, Adam and Mansun.

Two new members have joined our Editorial team. Kyle Montgomery from Air Force Research Laboratory, Albuquerque, as the Regional Editor for Regions 5 & 6 and Ming Liu from Institute of Microelectronics, Chinese Academy of Science as Regional Editor for East Asia of Region 10. It is my pleasure to welcome both of them to our team as New Editors.

Kyle Montgomery is a Research Engineer with the Air Force Research Laboratory (AFRL) in Albuquerque, New Mexico, USA.In addition, he holds

a Research Assistant Professor title at the University of New Mexico in the Electrical & Computer Engineering department, where he teaches a graduate course on solarcells. Dr. Montgomery's research interests (PhD, Purdue University, 2012) focus on high efficiency solar cells and power systems for space applications. He serves on the EDS Young Professionals Committee and the planning committee of the IEEE Photovoltaic Specialists Conference (PVSC).

Ming Liu is a Professor at the Institute of Microelectronics, Chinese Academy of Sciences and Director of the Key Laboratory of Microelectronics Devices & Integrated Technology. She received her Ph.D. in Material Engineering from Beijing University of Aeronautics and Astronauts, China in 1998 and later joined the Institute of Microelectronics, Chinese Academy of Sciences and became professor in 2000. Her current research areas include micro/nanofabrication, new structure NVM device and circuit, modeling and simulation, reliability and organic electronic devices.

M. K. Radhakrishnan Editor-in-Chief, EDS Newsletter e-mail: radhakrishnan@ieee.org

### EDS BOARD OF GOVERNORS MEETING HIGHLIGHTS

Simon Deleonibus EDS Secretary

May 28–29, 2016: The EDS Mid-Year Governance Meeting returned to Region 8 this year in grand style, bringing together the Society's senior leadership and several

EDS Chapter Chairs from across Region 8 to beautiful Grenoble, France. The meeting was a phenomenal success, combining vital society business with some truly special social events to create an enriching and energizing event for all attendees. The weekend began on Saturday morning, with a series of important Standing Committees meetings.

The EDS BoG meetings started with the introduction of new EDS Operations Director, James Skowrenski, who joined the EDS team with extensive experience in association management. The first day's meetings included Fellows Evaluations, Publications and Newsletter Joint meeting, Technical Committees meeting and Education, Membership and Chapters meeting.

The Fellows Evaluation Committee began their work bright and early Saturday morning, with the

EDS Forum members during dinner at Restaurant du Teleferique in Grenoble (450m above sea level) – May 29, 2016

difficult task of reviewing and evaluating 42 IEEE Fellow nominations. Led by Paul Yu, the committee did the evaluations of all nominations and endorsements for many hours, proving once again that the work of this committee is among the most challenging and important to the Society and the IEEE.

As the EiC of Newsletter, M. K. Radhakrishnan presented the status and the improvements made in the

newsletter during the last 3 years. The increased emphasis on technical content, introduction of columns for YPs and introduction of Messages from Presidents in each issue were highlighted. The transition to web format and open access for Newsletter received positive reviews.

Hisayo Momose, EDS VP of Publications and Products, chaired the critical Publications committee meeting. The new editor for J-EDS was

announced as Mikael Ostling and the strategy for the management of the EDS publication portfolio was shared.

Led by EDS's VP of Technical Committees and Meetings, Ravi Todi reviewed our many technical meetings and conferences. The discussions also included the newly approved Electron Devices Technology and Manufacturing Conference, which will be held on February 28 to March 2, 2017 in Japan.

Combining the Membership, Chapters and Education meetings has proved very effective. Vice Presidents Tian-Ling Ren (Membership), M. K. Radhakrishnan (Regions and Chapters) and Mansun Chan (Education Chair), convened an outstanding forum to address these important areas of the society's life. In addition to providing an important strategic planning session, the highlight of the meeting was the open dialogue with all present. This meeting was followed by Region 8 Chapters meeting chaired by Region 8 SRC Chair Simon Deleonibus in which several EDS chapter chairs from across Region 8 participated. The meeting provided an excellent opportunity for staff and volunteer leadership to learn more about the chapters' perspectives, needs, and successes. This meeting continued with the Region 8 Chapters meeting

The EDS Forum and Board of Governors met on Sunday, May 30th for the Mid-Year Governance meeting chaired by the President Samar Saha. The meeting's discussions covered nearly every aspect of the society's operations, ending with an extended Open-Forum to provide a free exchange of ideas and debate over how we can continue to improve the Society to ensure its preeminence as the world's leading organization devoted to device engineering. Here are some of the highlights:

- EDS Treasurer, Subramanian Iyer, reviewed the financial state of EDS and the news is good! Publication page counts and prices for 2017 have been approved. Also, EDS membership dues will remain the same at \$18 for 2017.

- EDS has endorsed the collaboration with the CMPT society and SEMI in sponsoring the heterogeneous integration roadmap with the goal of collaboration with other IEEE societies and other organizations.

- An updated EDS field of interest has been approved and will be sent to IEEE for formal approval.

- It has been noted that EDS member strength is almost stagnant and the student member strength

- is very low compared to the student Chapters.

- A good number of Chapters are found to be shy in communicating activities and reports. Regions and Chapters committee is empowered to revitalize weak Chapters. A concerted effort to improve and monitor student Chapters is planned.

- For the EDS Region 9 Outstanding Student Paper Award a minor modification to the eligibility requirements is made by allowing a nominee to be enrolled at a higher education institution located in Region 9 at the time of the paper publication date.

- A motion was made and passed to create an EDS Documents Review Ad Hoc Committee to review the inconsistencies of the EDS Constitution and Bylaws, along with other documents.

We offer our sincere thanks to Mireille Mouis and Marco Pala for their invaluable help in planning this meeting. Without their diligence, patience, and dedication, this meeting simply would not have happened.

> Simon Deleonibus EDS Secretary

### EDS REGION 8 MEETING

The EDS Region 8 Meeting was held during the BoG/Forum meetings series in Grenoble on the afternoon of May 29th. The meeting gathered 30+ attendees from all regions and mainly Region 8 Chapters Chairs and Representatives (11). For the meeting preparation, all Region 8 Chapters Chairs were requested by Region 8 SRC Chair, Simon Deleonibus, to send 3 highlights from their Chapter's recent activities. After introductory remarks and data presentations by both M. K. Radhakrishnan, EDS Vice President of Regions and Chapters and Simon Deleonibus, the **Chapters Chairs and Representatives** were invited to comment directly on their highlights tables.

An intensive debate occured during the discussion on the following points:

- Region 8 is the widest region for IEEE and includes 1,619 members, 52 chapters, among which 13 are 100% EDS, 31 are Joint Chapters and 8 Students Chapters. It has the largest proportion of Joint Chapters among all re-

- gions, mainly due to the fact that diversification is widely spread in the industry activities.

- The formal reporting of our Chapters to the IEEE EDS headquarters was analyzed and commented through the use of a common metrics. The available data include L31 forms, MQ and DL deliveries, and EDS Newsletter reporting. As a matter of fact, the number of L31 forms generated by the Chapters is not a direct measure of Chapters' activities because these forms are used for

different purposes by different Chapters. The number of these forms ranges from 0 to 132 in a year (2015) in different Chapters! For no reason, these forms have to be used for internal reporting! Region 8 has at least 6 «dormants/shy Chapters» (3 Chapters are 100% EDS), which for unknown reasons have not reported for the last 3 years. This number has to be corrected and we should know why.

• The activity of Region 8 SRC (Chair Simon Deleonibus; Vice-Chairs Tomislav Suligoj, Arokia Nathan and Andrzej Napieralski) was reported. Region 8 SRC has prioritized since 2015 to revitalize «dormant/ shy» chapters (2 were reactivated last year and 6 are in revitalization process in 2016), increase the number of chapters (2 were created in 2015 and 2 are in process), strengthen the network by visits to the Chapters (2 in 2015). New opportunities for chapters creation (at

Society officers and chapter chairs who attended the EDS Region 8 Meeting in Grenoble, France

least 3) are analyzed and being considered.

- A discussion was carried out on the opportunity to create new chapters from larger ones. This is not a simple question, because local conditions in each country need to be considered. For example, in some countries, maintaining or defining one/several chapters could be critical because members may be spread all over the country or concentrated in a specific area. Finally, do we need

- more chapters or more members? Which is the optimal number to set up a Chapter? All these questions have to be addressed properly on a case-by-case basis.

- The detailed highlights tables of different chapters and their slides presented at the meeting have been disseminated to all Chapters Chairs.

Simon Deleonibus Region 8 SRC Chair CEA/LETI, MINATEC Grenoble, France

### AWARDS AND RECOGNITIONS

### 2016 WILLIAM R. CHERRY AWARD WINNER

Dr. Pierre Verlinden

Dr. Pierre Verlinden, Chief Scientist and Vice-President of Trina Solar, has received the IEEE William R. Cherry Award in recognition of his long and distinguished career

at the forefront of PV technology and commercialization, for leading technology advances including the interdigitated back contact (IBC) cell, mono- and multicrystalline PERC silicon solar cells and multijunction III–V dense array technology for CPV application, and for his overall leadership of key R&D organizations throughout his career. Dr. Verlinden is currently

Vice-Chair of the State Key Laboratory of PV Science and Technology, Changzhou, China, as well as adjunct Professor at Sun Yat-sen University, Guangzhou, China.

He has been involved with high-efficiency PV technologies for more than 35 years, first as an early developer of IBC silicon solar cells from 1979, at the University of Louvain, Belgium, and Stanford University, California. He continued his pioneer work on IBC solar cell development for CPV and onesun applications as Director of R&D at SunPower until 2001. After a short stay at Origin Energy Solar, Australia, to build a pilot line for the Sliver cell, he founded AMROCK and helped many other companies and research centers

to develop advanced PV technologies, including multijunction III–V dense arrays for reflective CPV systems at Solar Systems, Australia. In early 2012, Dr. Verlinden joined Trina Solar in Changzhou, China, where, marrying western-style and Chinese-style R&D, he transformed the State Key Laboratory of PV Science and Technology into one of the most advanced research centers in photovoltaics. He has been associated with several efficiency world records during his long career dedicated to photovoltaics.

Dr. Verlinden delivered his Cherry Award acceptance speech on Monday, June 6th in the Oregon Ballroom, during the 2016 PVSC Opening Keynote Session.

### 43rd Photovoltaic Specialists Conference (PVSC) YOUNG PROFESSIONAL AWARD WINNER

Dr. Bram Hoex, Recipient of the 43rd PVSC Young Professional Award

The IEEE Photovoltaic Specialists Conference (PVSC) continued this year in recognizing an outstanding young professional in the photovoltaics (PV) community. The PVSC Young Professional Award recognizes individuals

who have made significant contributions to the science and technology of PV energy conversion, including work on PV materials, devices, modules, and/or systems. The award recipient must also show significant promise as a leader in the field.

On behalf of the organizing and program committees of the 43rd IEEE PVSC, I am delighted to announce the recipient of this year's award-Dr. Bram Hoex (The University of New South Wales). He is recognized for pioneering work on rear-surface passivation of Si solar cells, which enabled an industry transition to higher efficiency, passivated emitter rear contact (PERC) cell technology.

Bram Hoex completed a MSc degree and PhD degree in Applied Physics from the Eindhoven University of Technology (TU/e) in the Netherlands. His PhD work on functional thin films for high-efficiency solar cells was recognized by both the SolarWorld "Junior Einstein" and Leverhulme "Technology Transfer" awards. After completing his PhD degree in 2008 he joined the Solar Energy Research Institute of Singapore (SERIS) at the National University of Singapore (NUS) as head of the Photovoltaic Characterization group. From 2012 to the end of 2014 he was Director of the Silicon Materials and Solar Cells Cluster as well as group leader Monocrystalline Silicon Wafer Solar Cells. In 2015 he joined the School of Photovoltaic and Renewable Energy Engineering (SPREE) at the University of New South Wales (UNSW) in Australia as an academic in a convertible tenure track position. His research focusses on the development and characterization of high-

efficiency silicon wafer solar cells, typically working in close collaboration with equipment and solar cell manufacturers to ensure rapid transfer to the PV industry. His current research focuses on development and commercialization of high-efficiency device architectures that capitalize on the UNSW advanced hydrogenation technique. He is best known for his ground breaking work on aluminum oxide for crystalline silicon surface passivation which is now the de facto standard for industrial PERC solar cells. He also pioneered the application of atomic layer deposition for silicon wafer solar cell manufacturing. During his career he has raised over US\$ 15M in competitive research funding of which US\$ 11M as lead Principal Investigator. He has published over 100 journal and conference papers which have been cited over 3100 times to date.

Congratulations, Dr. Hoex!

Kyle Montgomery Awards Chair, PVSC-43 Air Force Research Laboratory

### EDITORIAL 2015 IEEE T-SM BEST PAPER AWARD

High quality scholarship requires technical excellence but also connects the work to the primary references in the field. In this way the reader advances their knowledge and gains perspective. The Transactions on Semiconductor Manufacturing supports these goals by recognizing the best paper chosen by the Associate Editors and reviewers.

The winning paper was selected from 140 papers published by T-SM in 2015. The winner is "An Algorithm of Multisubpopulation Parameters with Hybrid Estimation of Distribution for Semiconductor Scheduling with Constrained Waiting Time" by Hung-Kai Wang, Chen-Fu Chien, and Mitsuo Gen published in the August 2015 issue of IEEE Transac-

tions on Semiconductor Manufacturing (10.1109/TSM.2015.2439054). I congratulate the authors on their selection.

> Anthony J. Muscat, Editor-in-Chief, T-SM Department of Chemical & Environmental Engineering University of Arizona

### 2014-2015 EDS REGION 9 OUTSTANDING STUDENT PAPER AWARD

The Electron Devices Society confers its prestigious Region 9 Outstanding Student Paper Award to the best Region 9 student paper published in an internationally recognized IEEE sponsored journal or conference in the field of electron devices related topics. The winning paper is entitled, "Modeling the Impact of Multi-Fingering Microwave MOSFETs on the Source and Drain Resistances". This paper was published in the IEEE Transactions on Microwave Theory and Techniques, and was authored by Fabián Zárate-Rincón, Roberto S. Murphy-Arteaga, Reydezel Torres-Torres, Adelmo Ortiz-Conde and Francisco J. García-Sánchez. The award will be presented at Symposium on Microelectronics Technology and Devices (SBMicro), which will be held August 30 to September 2, 2016 in Belo Horizonte, Brazil. The Award consists of a certificate and reimbursement of up to US \$1.500 to cover one author's travel and accommodations to attend the conference. On behalf of the Electron Devices Society, I would like to congratulate Fabián Zárate Rincón and the remaining authors for this achievement. Brief biographies of all the authors of the paper are given below.