OCTOBER 2016 VOL. 23, NO. 4 ISSN: 1074 1879

EDITOR-IN-CHIEF: M.K. RADHAKRISHNAN

#### TABLE OF CONTENTS

| TECHNICAL BRIEFS                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Message from EDS President-Elect     Message from the Editor-in-Chief     Message from EDS Vice President of Publications     EDS VLSITechnology and CircuitsTechnical Committee     IEEE/OSA Journal of DisplayTechnology (JDT)     Letters to the Editor     Call for Nomination – EDS Newsletter Editor-in-Chief                                                                                                                                                  |

| Award Recipients and Call for Nominations  2015 Paul Rappaport Award Winners 2015 EDS George Smith Award Winners 2017 William R. Cherry Award – Call for Nominations  EDS Members Named Winners of 2016 IEEE Medals and Awards  EDS Members Recently Elected to IEEE Senior Member Grade  2014–2015 EDS Region 9 Outstanding Student Paper Award  Announcement of the EDS Masters Student Fellowship Winners  Announcement of the EDS PhD Student Fellowship Winners |

| YOUNG PROFESSIONALS     Reflections from EDS Young Professionals     EDS-ETC Programs     IEEE Technical Community Spotlight     EDS Webinar on Nanometer-Scale III–V CMOS     Learn More About QuestEDS                                                                                                                                                                                                                                                             |

| CHAPTER NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| REGIONAL NEWS                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

EDS MEETINGS CALENDAR......55

# TECHNICAL BRIEFS

# FROM MEMORY TO SENSOR, LOGIC AND DISPLAY

MUHAMMAD MASUDUZZAMAN AND MUHAMMAD ASHRAFUL ALAM

PURDUE UNIVERSITY, WEST LAFAYETTE, IN 47907, USA

Memory materials have recently been used not only in data storage, but also in emerging applications in data sensing, processing and display. What properties do these bistable materials have that attract their pervasive use in all the major functional areas of future electronic devices?

Information sensing, processing, storing, and displaying are the four fundamental functions of electronic devices. Whether it is a transistor for logic operations, a flash memory for data storage, a light emitting diode for display devices, or an ion-sensitive switch for biosensing applications, until now these key functional devices have been made of different combinations of metallic/semiconducting/insulating materials. Recently, however, many of the emerging devices/architectures [1] are beginning to use bistable (non-volatile) memory materials or analogous bistable structures (e.g., NEMS) to achieve superior performance. These include neuromorphic [2] and logic-in-memory architectures [3], nanomagnetic and spintronic devices [4, 5], negative capacitance transistors [6], NEMS switch [7], atomic switch [8], correlated electron devices [9], electrophoretic and other bistable passive displays [10-12], bifurcation based chemical and biosensors [13, 14], etc. A close examination reveals that such widespread use of memory structures in data sensing, processing, storing and displaying (as we refer by the term "memtronics", signifying memory electronics) is not a mere coincidence. In the following, we will list a few intrinsic properties of these materials that encourage their ubiquitous use in such a broader range of applications.

(1) A binary logic device works by defining two states that are isolated by an "energy barrier" created by some physical means within the system [15, 16]. The input information conditionally

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at radhakrishnan@ieee.org

# ELECTRON DEVICES SOCIETY

#### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### President-Elect

Fernando Guarin GlobalFoundries E-mail: fernando.guarin@ieee.org

#### Treasurer

Subramanian S. Iyer UCLA E-mail: iyer@ieee.org

**Secretary** Simon Deleonibus CEA-LETI

E-mail: simon.deleonibus.1992@

ieee.org

#### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Sr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

# Vice President of Membership and Services

Tian-Ling Ren Tsinghua University

E-mail: rentl@mail.tsinghua.edu.cn

# Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: hmomose@ynu.ac.jp

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

# Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

#### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

#### Membership Administrator

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (BoG) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| 2016                                                                                             | TERM                                          | <u>2017</u>                                                                                             | TERM                                                 | 2018                                                                                                | Term                                          |

|--------------------------------------------------------------------------------------------------|-----------------------------------------------|---------------------------------------------------------------------------------------------------------|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-----------------------------------------------|

| A. Escobosa<br>R. Huang<br>L. Lunardi<br>M. Ostling<br>M.K. Radhakrishnan<br>J. Swart<br>X. Zhou | (2)<br>(1)<br>(1)<br>(2)<br>(2)<br>(1)<br>(2) | Z. Celik-Butler<br>S. Chung<br>M. Farooq<br>P. Fay<br>C. Lilley<br>D. Misra<br>H. S. Momose<br>T.L. Ren | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) | N. Bhat<br>D. Camacho Montejo<br>S. Deleonibus<br>M. Ieong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(2) |

# NEWSLETTER EDITORIAL STAFF

#### **Editor-In-Chief**

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

#### **REGIONS 1-6, 7 & 9**

Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

# Central USA & Canada (Regions 4 & 7)

Karim S. Karim University of Waterloo E-mail: kkarim@uwaterloo.ca

# Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

#### **REGION 8**

#### Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

#### Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### **UK, Middle East & Africa**

Jonathan Terry The University of Edinburgh E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

# REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

#### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editorin Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

#### Newsletter Deadlines

| <u>Issue</u> | DUE DATE    |

|--------------|-------------|

| January      | October 1st |

| April        | January 1st |

| July         | April 1st   |

| October      | July 1st    |

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2016 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

**FPO**

### EMERGENCE OF MEMTRONICS

(continued from page 1)

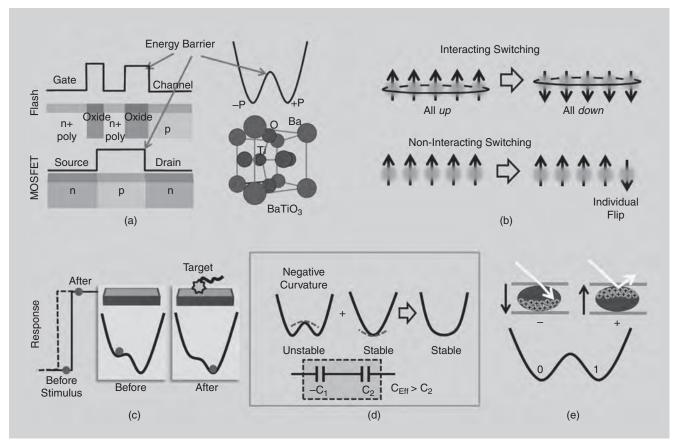

lowers the barrier so that the relative occupancy of the states can be altered. For traditional semiconductor devices, the barrier is created macroscopically by stacking different semiconductor materials, oxides, metals, etc. For example, gate metal, oxide layers, and semiconductor channel form the required barriers in a flash memory (Fig. 1(a)). Similarly, the channel forms the energy barrier from source to drain in a MOSFET [15]. The physical design of energy landscape using

different materials in this heterogeneous manner leads to a certain minimum scaling limit. This is because the integrity of both the materials and/or the devices are degraded at very small length scales due to, for example, random dopant fluctuations, short channel effects, etc. In contrast, the required energy barrier is intrinsically built-in within any memory material (Fig. 1(a)). Thus, a single homogeneous material, can act as a switch or memory, and ideally, the element can scale down to a much smaller limit [17], overcoming the density scaling challenge associated with classical semiconductor devices. Some of the beyond CMOS devices, such as nanomagnetic logic [4] (e.g., Magnetic Quantum Cellular Automata (MQCA) [18]) exploit this intrinsic energy barrier of the memory materials to promise high density logic/memory devices for future electronics.

(2) Another problem of the existing semiconductor devices relates to the excessive energy neces-

Fig. 1. (a) Energy barrier in traditional semiconductor devices (shown for flash memory and MOSFET) are created macroscopically by connecting different semiconductor/insulator materials. This barrier can be intrinsically present in a memory material as illustrated using a ferroelectric crystal (BaTiO<sub>2</sub>) where the Ti atoms stay in one of the two energy pockets below the Curie temperature. (b) With interacting switching in a magnetic nanodot, a large number of spins are "stitched" together and switch like a single entity. If those were non-interacting, individual spins could be flipped, making those more vulnerable to thermal noise. (c) Due to the extreme nonlinearity of a bifurcation based sensing device, the capture of a tiny bit of target molecule can cause a sudden jump in the response signal. (d) When biased properly with a stable system (positive capacitance), the unstable equilibrium state of a memory material (negative capacitance) can give unconventional performance boost to traditional devices, such as increasing the gate capacitance of a transistor, etc. (e) Memory structures can have optically distinguishable states as used in an electrophoretic display.

sary to switch between the states. This challenge originates from the greater degree of freedom of the electronic charges which translates to lesser immunity to thermal noises. For example, the minimum switching energy for N electronic charges is given by DEB, where  $E_B = k_B T In(r)$  is the minimum energy barrier height necessary to define binary states with an error probability of 1/r [15], and (D~N) is the degree of freedom for the charges. Thus, the minimum voltage margin is  $E_B/q$  (~0.4 V for  $r = (I_{ON}/I_{OFF}) = 10^7$ ). However, for some of the memory materials, the switching of the state variables occurs collectively, which reduces the degree of freedom. For example, during a switching event, all the spins (large N) in a nanomagnet work in unison  $(D \sim 1)$  [19] (Fig. 1(b)). In such case, the minimum energy dissipation per switching is of the order of  $E_B$  (instead of  $NE_B$ ). Many of the nanomagnetic and spintronic devices promise energy scaling by several orders of magnitude [4] by utilizing this interacting switching of memory materials.

Interestingly, the interacting switching property is also present in other bistable memory structures, such as a NEMS. In this case, the charges are constrained mechanically within a given mass (electrode) and the degree of freedom reduces to the order of one. As a result, N charges can be switched from one state to the next with a very small difference in the applied voltage ( $E_B/Nq$ , instead of  $E_B/q$  for a non-interacting system), which is characterized essentially by a sudden jump during the switching of a NEMS. In addition to low power logic and memory applications [1], this extreme nonlinear transition is the basis of bifurcation based chemical and biosensing techniques which promise attogram-scale mass sensing in atmospheric conditions [13, 14]. Here the system can be biased very close

- to the bifurcation point in a metastable way and the arrival/detection of the target causes a sudden jump across the critical point (Fig. 1(c)).

- (3) Another feature of memory structures, which is not very obvious at first, is the presence of unstable equilibrium states in between a pair of stable states (Fig. 1(d)). Although these unstable states are generally inaccessible (and hence not very useful), one can bias a memory material at the unstable state by combining it with another stable material. In the combined system, the former acts as a negative circuit element (e.g., negative capacitor for case of ferroelectrics) which can potentially enhance the performance of the traditional devices and circuits in a very unique way. The proposed negative capacitance field effect transistor [6] and the ferroelectric-NEMS [20] utilize this property to amplify the applied voltage for a sub-60 mV/ decade switching and sub-1V pullin voltage, respectively.

- (4) The most recognized property of nonvolatile memory is the bistability which not only enables various data storage applications, but also reduces power consumption during off state in a logic switch. In addition, if a memory element has optically distinguishable discrete states (Fig. 1(e)), it can be used as a superior quality passive display element. This includes electrophoretic, droplet-driven electrowetting, bistable electrofluidic, bistable LCD, MEMS-based display, etc. [10, 11], which work using the ambient light (like ink on a paper) and the only energy required is during the switching of the display pixel. This can potentially save significant amount of power in many portable electronic devices.

- (5) Finally, the intrinsic scalability of memory materials enables the design of logic devices with memory as an elemental and integrated building block. In other words, one can squeeze a memory functionality

into the design of a logic device which was not practical with previous generations of heterogeneous non-volatile memories due to their relatively larger size. These revamped beyond-Neumann logic designs, such as adaptive, neuromorthic logic [2] and logic-in-memory [3] architectures, which promise a paradigm shift in computation, and reduced transmission loss.

These are some reasons that inspired widespread use of bistable memory structures in different electronic devices (sensor, logic, memory, display). Since all of these devices possess analogous double well energy landscapes, one must take advantage of this connection across the disciplines, and share inventions and solution strategies of one field to the other. In fact, such efforts have already led to the realization that the negative capacitance scheme [6], originally developed for logic, can also be used in NEMS or bistable display applications [20]. In addition to such cross-disciplinary research, one must also focus on defining the primary challenges towards developing these memtronic devices/ architectures. For example, one may identify the reduced speed and the inefficient switching [21] of some memory materials due to domain formation, interfacial defects, grain boundaries, etc. Note that the unprecedented development of semiconductor technology has been possible partly due to the ability to grow the single crystalline materials and improve the quality of the interfaces. Likewise, one needs to develop low defect density memory materials and integrate these in the future low power memtronic devices. The technological barriers, without any doubt, are challenging, but once the functionality and performance are promised, it is highly likely that these barriers would be overcome.

#### References

[1] "Emerging Research Devices," International Technology Roadmap for Semiconductors (ITRS), 2011.

[2] S. D. Ha and S. Ramanathan, "Adaptive oxide electronics: A review," Journal of Applied Physics, vol. 110, pp. 071101-071101, 2011.

[3] S. Matsunaga, J. Hayakawa, S. Ikeda, K. Miura, H. Hasegawa, T. Endoh, et al., "Fabrication of a nonvolatile full adder based on logic-inmemory architecture using magnetic tunnel junctions," Applied Physics Express, vol. 1, p. 1301, 2008.

[4] S. A. Wolf, J. Lu, M. R. Stan, E. Chen, and D. M. Treger, "The promise of nanomagnetics and spintronics for future logic and universal memory," Proceedings of the IEEE, vol. 98, pp. 2155-2168, 2010.

[5] S. A. Wolf, D. D. Awschalom, R. A. Buhrman, J. M. Daughton, S. Von Molnar, M. L. Roukes, et al., "Spintronics: A spin-based electronics vision for the future," Science, vol. 294, p. 1488, 2001.

[6] S. Salahuddin and S. Datta, "Use of negative capacitance to provide voltage amplification for low power nanoscale devices," Nano Lett, vol. 8, pp. 405-410, 2008.

[7] H. Kam, D. T. Lee, R. T. Howe, and T.-J. King, "A new nano-electromechanical field effect transistor (NEMFET) design for low-power electronics," in IEEE International Electron Devices Meeting, 2005, pp. 463-466.

[8] T. Sakamoto, H. Sunamura, H. Kawaura, T. Hasegawa, T. Nakayama, and M. Aono, "Nanometer-scale switches using copper sulfide," Applied Physics Letters, vol. 82, pp. 3032-3034, 2003.

[9] H. Takagi and H. Y. Hwang, "An emergent change of phase for electronics," Science, vol. 327, pp. 1601-1602, 2010.

[10] B. Comiskey, J. D. Albert, H. Yoshizawa, and J. Jacobson, "An electrophoretic ink for all-printed reflective electronic displays," Nature, vol. 394, pp. 253-255, 1998.

[11] D. Graham-Rowe, "Electronic paper targets colour video," Nature Photonics, vol. 2, pp. 204-205, 2008.

[12] J. Chen, W. Cranton, and M. Fihn, Handbook of Visual Display Technology: Springer, 2012.

[13] V. Kumar, J. W. Boley, Y. Yang, H. Ekowaluyo, J. K. Miller, G. T. C. Chiu, et al., "Bifurcation-based mass sensing using piezoelectrically-actuated microcantilevers," Applied Physics Letters, vol. 98, p. 153510, 2011.

[14] W. Zhang and K. L. Turner, "Application of parametric resonance amplification in a singlecrystal silicon micro-oscillator based mass sensor," Sensors and Actuators A: Physical, vol. 122, pp. 23-30, 2005.

[15] V. V. Zhirnov, R. K. Cavin Iii, J. A. Hutchby, and G. I. Bourianoff, "Limits to binary logic switch scalinga gedanken model," Proceedings of the IEEE, vol. 91, pp. 1934-1939, 2003.

[16] R. Landauer, "Irreversibility and heat generation in the computing process," IBM journal of research and development, vol. 5, pp. 183-191, 1961.

[17] S. Loth, S. Baumann, C. P. Lutz, D. M. Eigler, and A. J. Heinrich, "Bistability in atomic-scale antiferromagnets," Science, vol. 335, pp. 196-199, 2012.

[18] C. S. Lent, P. D. Tougaw, W. Porod, and G. H. Bernstein, "Quantum cellular automata," Nanotechnology, vol. 4, p. 49, 1993.

[19] S. Salahuddin and S. Datta, "Interacting systems for self-correcting low power switching," Applied Physics Letters, vol. 90, pp. 093503-093503, 2007.

[20] M. Masuduzzaman and M. A. Alam, "Effective Nanometer Airgap of **NEMS Devices Using Negative Capac**itance of Ferroelectric Materials," Nano Letters, vol. 14, pp. 3160-3165, 2014.

[21] B. Behin-Aein, A. Sarkar, S. Srinivasan, and S. Datta, "Switching energy-delay of all spin logic devices," Applied Physics Letters, vol. 98, p. 123510, 2011.

Muhammad Masuduzzaman received the Ph.D. degree from Purdue University, West Lafayette, Indiana,

USA, in 2012, and joined there as a postdoctoral research associate at the same year. He contributed towards the reliability and performance of transistors and devices made with highk, higher-k and negative-k materials. His current research interests include design, performance and reliability of novel electronic devices, nonvolatile memories and microelectromechanical systems. Currently he is with SanDisk, a Western Digital brand, at the Silicon Valley, California, USA. He can be reached at masuduzzaman@ieee.org

Muhammad Ashraful Alam holds the Jai N. Gupta professorship at Purdue University, where his research focuses on the phys-

ics and technology of semiconductor devices. During his tenure at Bell Laboratories, Murray Hill, New Jersey, from 1995 to 2003, he made fundamental contributions to reliability physics of semiconductor devices and optoelectronic ICs. Since joining Purdue in 2004, his research has broadened to include biosensors, flexible electronics, and solar cells. Prof. Alam enjoys teaching - more than one hundred thousand students worldwide have learned some aspects of semiconductor devices from his web-enabled courses. He can be reached at alam@purdue.edu.

### EDS TUTORIALS AT SEMICON WEST 2016

By MUKTA FAROOQ

EDS coordinated a half-day session at Semicon West 2016, held in the Moscone Center in San Francisco on July 14th, as part of the overall Semicon West 2016 Business and Technology Conference. This was a paid session, with IEEE EDS members receiving a discount code for registration. Both tutorials were well attended with over 70 people in each session.

# Tutorial: 2.5D/3D Integration Technology

Instructor: Mukta Farooq, Ph.D., GlobalFoundries Fellow and IEEE Fellow.

2.5D/3D integration technology encompasses a wide variety of configurations which employ TSVs (Through Silicon/Substrate Vias) in a silicon wafer. 2.5D generally refers to heterogeneous integration of chips using interposers which typically have only passive components: wiring, capacitors and inductors. 3D technology goes beyond the interposer by integrating logic functionality in the assembly. 3D integration has the ability to enhance system performance by increasing bandwidth, reducing wire delay, and enabling better power management. In 3D technology, the TSVs may be integrated into the CMOS transistor fabrication at a number of points in the manufacturing sequence. Key considerations to determine the optimal introduction point include the size of the TSV, dimensional compatibility of the TSV with the BEOL (Back End Of Line) features, and the wiring design requirements. In this tutorial, we will review the various types of 2.5D and 3D integration, and why they offer significant advantages over conventional methods. We will also discuss the key elements of TSV fabrication including via etching, insulation, metallization, annealing, capping, as well as wafer grindside processing. We will also discuss the effects of TSVs on devices and BEOL structures, and the type of reliability testing that is required to evaluate the long-term impact of TSVs.

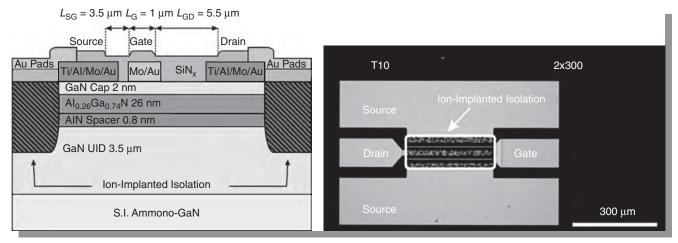

# Tutorial: GaN Devices and Technology

Instructor: Patrick Fay, Ph.D., Professor, Dept. of Electrical Engineering, University of Notre Dame.

The unique material properties of GaN and related materials provide significant opportunities for realizing exceptional levels of device performance, both for conventional devices such as HEMTs and HFETs, as well as for novel and potentially disruptive device designs. These devices show promise for both existing as well as emerging applications. Current applications for GaN devices include power conversion and control as well as RF power amplification, while potential future applications include high-performance mixed-signal, millimeter-wave, and sensing applications, to name just a few. GaN-based device concepts to address the specific needs of each of these areas are under intensive development by groups around the world. This course will provide a broad overview of the material properties, device structures, fabrication processing issues, and applications surrounding this emerging device technology. At the material properties level, the III-N compounds offer several unique features that are important to achieving optimum device performance. The physical origins of these fundamental material properties - and how these properties differ in important ways from other semiconductor material systems - will be described. Device structures that leverage these unique properties of GaN and related materials, including HEMTs and HFETs, homojunction and heterojunction diodes, and a range of vertical FET concepts, will be described and their strengths and limitations for applications will be explored. This discussion will also include an overview of fabrication process technology, scaling trends, the impact of process modules on device performance and characteristics, and key technological issues. Applications for these device technologies will be discussed, and the prospects for future application spaces for nitride-based devices will be examined.

# UPCOMING TECHNICAL MEETINGS

# 2016 IEEE INTERNATIONAL ELECTRON DEVICES MEETING: PROGRAM HIGHLIGHTS

The 62nd annual IEEE International Electron Devices Meeting (IEDM), to be held December 3-7, 2016, in San Francisco, California, USA, will have various Special Focus Sessions, Tutorials and Workshops. Details of these events include:

#### **Special Focus Sessions**

**Wearable Electronics and Internet** of Things (IoT) - Wearable technology offers great promise for communications, fitness tracking, health monitoring, speech therapy, elder care/assisted living and many other applications. This Special Focus Session has been organized to benchmark wearable electronics technologies, to address applications with comprehensive system demonstrations, and to learn industrial perspectives about the gaps, challenges and opportunities for wider uses of wearable and IoT technologies. Papers on flexible/stretchable electronics, MEMs, display devic-

- es, sensors, printed electronics, organic devices and 2-D material devices enabling wearables/loT devices also will be featured.

- Quantum Computing As traditional CMOS scaling enters the post-Moore's Law era, quantum computing has emerged as a possible candidate for further device scaling because it exploits the laws of quantum physics and may make much more powerful computers possible. This Special Focus Session will explore relevant semiconductor-related fabrication issues and will brainstorm R&D directions for new materials, devices, circuits, and manufacturing approaches for the

- scalable integration of a large number of gubits with CMOS technology, operating at cryogenic temperatures for the realization of quantum computers.

- **System-Level Impact of Power** Devices - While there are forums that serve circuit experts for the exchange of ideas and the reporting of breakthroughs, there hasn't been a suitable forum for bringing device and circuit experts together to consider impacts at the system level, even though that would be fruitful due to the interactions of circuits and devices. IEDM aims to serve as the forum for their dialogue, and so this Special Focus Session has been organized. Papers are expected to explore the system-level impact of power devices, and also to describe various types of power devices targeting the full range of power/power conversion applications such as hybrid vehicles, utility and grid control, computing/telecom power supplies, motor drives, and wireless power transfer.

- **Ultra-High-Speed Electronics -**There have been many advances and breakthroughs in ultra-highspeed electronics for communications, security and imaging applications, but technology gaps continue to prevent spectrum above millimeter-wave frequencies from being fully used. This Special Focus Session has been organized to discuss, showcase and benchmark advanced ultra-high speed devices and circuits based on high-electron-mobility transistors (HEMTs), heterojunction bipolar transistors (HBTs) and conventional CMOS devices; high-speed interconnect; antennas for ultra-

The city of San Francisco is just south of the Golden Gate Bridge

high-speed systems; ultra-high-frequency oscillators; and to discuss other possible applications.

#### **Tutorials**

A program of 90-minute tutorial sessions on emerging technologies will be presented by experts in the fields, to bridge the gap between textbooklevel knowledge and leading-edge current research. Advance registration is recommended.

- The Struggle to Keep Scaling BEOL, and What We Can Do Next, Dr. Rod Augur, GlobalFoundries -Looking ahead, it's the interconnect that threatens further cost-effective scaling. The tutorial will cover challenges and trade-offs in back-endof-the-line (BEOL) scaling, and will evaluate emerging devices from a scaled-BEOL viewpoint.

- **Electronic Circuits and Architec**tures for Neuromorphic Computing Platforms, Prof. Giacomo Indiveri, University of Zurich and ETH Zurich - The principles and origins of neuromorphic (i.e., braininspired) engineering, examples of neuromorphic circuits, how neural network architectures can be used to build large-scale multi-core neuromorphic processors, and some specific application areas well-suited for neuromorphic computing technologies will be discussed.

- **Physical Characterization of** Advanced Devices, Prof. Robert Wallace, Univ. Texas at Dallas – Physics, and chemistry that enable modern physical characterization of novel electronic materials will be covered. How these techniques can shed light on electronic materials research and development, and on the resultant devices. Examples of novel electronic materials for device applications and techniques discussed will include high-resolution electron microscopy, scanning tunneling microscopy and spectroscopy, dynamic x-ray photoelectron spectroscopy, and ion mass spectrometry. The detection

- limits of these techniques and its relation to device behavior.

- Present and Future of FEOL Reliability - from Dielectric Trap Properties to Reliable Circuit Operation, Dr. Ben Kaczer, IMEC - This tutorial will introduce the main degradation mechanisms occurring in present-day CMOS. The reliability of novel devices (SiGe, IIIV, gateall-around nanowires, junctionless FETs, tunnel FETs), of deeplyscaled devices, and of circuits (e.g., "reliability-aware" designs) will be covered in detail. The tutorial will give attendees an overview and background in this area sufficient to allow them to follow and participate in any discussion on reliability in general and on front-end-of-theline (FEOL) reliability in particular.

- Spinelectronics: From Basic Phenomena to Magnetoresistive Memory (MRAM) Applications, Dr. Bernard Dieny, Spintec CEA -Spintronics phenomena, magnetic tunnel junctions (growth, magnetic and transport properties), field-written MRAM (toggle and thermally assisted MRAM), STT-MRAM (principle and development), 3-terminal MRAM and innovative architectures that benefit from these high-endurance nonvolatile memories will be covered.

- Technologies for IoT and Wearable Applications, Including Advances in Cost-Effective and Reliable Embedded Non-Volatile Memories. Dr. Ali Keshavarzi, Cypress Semiconductor - A range of technology opportunities for IoT and wearable applications, including embedded non-volatile memories (eNVM), IPs and integrated solutions based on charge-trap memory technologies such as SONOS for low power (LP) and ultra-low-power (ULP) for advanced technology nodes are included. Technologies will be described for various integrated IoT, wearable and energy-harvesting systems using programmable systems-on-chips (SoCs) with digital and analog capabilities, along with low-energy Blue-

tooth radio, WiFi radio, solar cells, sensors, actuators, and power management ICs will be described.

#### **Short Courses**

The Short Courses provide the opportunity to learn about important areas and developments, and to benefit from direct contact with world experts. Advance registration is recommended.

- 1. Technology Options at the 5-Nanometer Node: This course will describe the complex technological challenges at the 5nm node and explore innovative potential solutions. It begins with an in-depth discussion of patterning strategies being pursued to print critical features. Then, a pair of lectures will provide an overview of current transistor technologies and their relative strengths/weaknesses in the context of various applications such as mobility, data centers and IoT. Strategies for effective mitigation of performance-limiting parasitic resistance and capacitance will be discussed, and advanced interconnect technologies including post-copper materials options for BEOL and MEOL applications will be addressed. Lastly, metrology challenges for in-line and end-of-line process technologies will be discussed. The intent of the course is to provide a thorough understanding in process technology targets at the 5nm node and their potential solutions. Attendees will have the opportunity to learn about advanced technology options that are being actively pursued in the industry from leading technologists.

- This course consists of lectures from six distinguished speakers:

- Nano Patterning Challenges at the 5 nm Node, Akihisa Sekiguchi, Tokyo Electron, Japan

- Novel Channel Materials for High-Performance and Low-Power CMOS, Nadine Collaert, IMEC

- **Transistor Options & Challenges**

- for 5 nm Technology, Aaron Thean, National University of Singapore

- Low Resistance Contacts to Enable 5 nm Node Technology: Patterning, Etch, Clean, Metallization and Device Performance, Reza Arghavani, Lam Research, USA

- Parasitic R and C Mitigation Options for BEOL and MOL in N5Technology, Theodorus Standaert, IBM, USA

- Metrology Challenges for 5nm Technology, Ofer Adan, Applied Materials, Israel

- 2. Design/Technology Enablers for **Computing Applications** –This course will describe how various design techniques and process technologies can enable computing applications, beginning with the relative advantages and disadvantages of processors such as CPU, GPU and FPGA with regard to today's high data demands. It then will cover how memory becomes a

bottleneck, and will discuss various emerging memory technologies to mitigate the problem. Because managing power dissipation has become critical, it also will offer a broad perspective on power efficiency in computing and how interconnect plays a pivotal role in both performance and energy efficiency. Finally, 2.5-D and 3-D advanced packaging technology is discussed for system integration.

This course consists of lectures from five distinguished speakers:

- The Rise of Massively Parallel Processing: Why the Demands of Big Data and Power Efficiency are Changing the Computing Landscape, Liam Madden, Xilinx, USA

- Breaking the Memory Bottleneck in Computing Applications with Emerging Memory Technologies: a Design and Technology Perspective, Gabriel Molas, Leti, France

- Power Management with Integrated Power Devices and how GaN Changes the Story, Alberto Doronzo, Texas Instruments, USA

- · Interconnect Challenges for Future Computing, William J. Dally, NVIDIA & Stanford, USA

- Advanced Packaging Technologies for System Integration, Douglas Yu, TSMC, Taiwan For Further information about IEDM, Registration, etc., visit www.ieee-iedm.org.

Follow IEDM via social media: Twitter: www.ieee-iedm.org/twitter LinkedIn: www.ieee-iedm.org/linkedin Facebook: www.ieee-iedm.org/ facebook

> Chris Burke co-Media Relations Director chris.burke@btbmarketing.com

> > Gary Dagastine co-Media Relations Director gdagastine@nycap.rr.com

# 1st Electron Devices Technology and Manufacturing CONFERENCE (EDTM)

TOYAMA INTERNATIONAL CONFERENCE CENTER, TOYAMA, JAPAN FEBRUARY 28TH TO MARCH 2ND, 2017

# **IEEE Electron Devices Technology and** Manufacturing Conference (EDTM):

The Inaugural EDTM (Electron Devices Technology and Manufacturing) conference is a full three-day conference to be held at Toyama International Conference Center, Japan from February 28th to March 2nd, 2017, fully sponsored by the IEEE Electron Devices Society (EDS). As semiconductor technology scaling challenges continues to grow, so should the industries collaborative efforts to overcome them must increase. EDTM is intended to serve as a forum for the electron devices community to collaborate on topics ranging from devices, materials, and tools, to create new and innovative technologies. EDTM will provide the following new formats.

#### 1. Technical sessions

EDTM 2017 and beyond will have a strong specific technical focus, and this year's focus being on devices and process technologies for advanced applications, IoE (Internet of Everything) and related low-power devices, advanced memories, sensors, actuators, MEMS, bio.-chips, passive devices, and all types of (exploratory) devices related to advance applications and IoE. Papers/ Posters on materials and processes for enabling above-mentioned devices building in heterogeneous integration such as 2.1, 2.5 and 3D structures using wafer-level packaging process (e.g.) are of great focus.

EDTM aims for highest quality, and all papers accepted would be subject to IEEE-EDS standard review processes and conference publishing guidelines. Accepted and presented papers will be published in EDTM proceedings. A selected number of high impact EDTM papers would be invited for the consideration of publication in the IEEE Journal of Electron Devices Society (J-EDS) as extended version of EDTM conference papers following the IEEE publication policy and J-EDS author-guidelines.

#### 2. Education

- Tutorials: We will provide both the basic and advanced programs. Basic program will be presented in local language.

- Poster sessions: Primarily intended for young engineers and

- students. The best poster will be awarded in the conference.

- Short courses: Will bring high level programs.

#### 3. Exhibition

Given the strong semiconductor manufacturing base in Asia, we intend to offer exhibits that will demonstrate products and technology. All of the exhibitors will have an opportunity to offer technical insight and share their knowhow. Moreover, we hope to offer Forum Making Session to engage and allow deeper discussions between device, material, and equipment engineers and technologists.

Following areas will be covered in the conference for which papers are solicited till November 4, 2016:

Devices and Manufacturing for "Cloud and Edge:" papers in all areas of device and manufacturing enhancing cloud and edge computing; highperformance devices include CMOS technology, platform technologies, stand-alone and embedded memory technologies, interconnects, optical interconnects, compound semiconductors, low-dimensional systems including 2D materials, nanowires, nanotubes, and quantum dots, 3D-IC. The devices for edge computing correspond to ultra-low power devices, energy harvester, RF devices, sensors, sensor networks, display, and actuators, MEMS, power devices, flexible and stretchable electronics, printed electronics, organic and inorganic displays.

Papers are also solicited on the manufacturing issues on process control, manufacturability, yield improvements, and failure analysis and related considerations.

Packaging and Manufacturing for "Cloud and Edge:" papers in all areas of advanced packaging and package-related manufacturing technologies for both cloud and edge applications of IoT, especially, heterogeneous integration technologies such as 2.1D, 2.5D and 3D integrations,

wafer-level packaging and panellevel packaging are strongly encouraged; breakthrough technologies in ultra-fine-pitch interconnection, submicron package-level wiring, optical/ wireless interconnect, power/sensor device packaging, control in thermalexpansion coefficient and thermal management are also recommended; package design methodology and technique for miniaturization of IoT edge sub-systems, and the manufacturability of all the technologies above are of course interested. Emerging topics, such as bio-compatible package, neuromorphic interconnection, and flexible/bendable package are very much welcome.

Process, Tools, and Manufacturing: papers in all areas of process, tools, and manufacturing systems with novel sensing technologies and artificial-intelligence and deep-learning algorithms; process and equipment including process module, process integration and process control, and equipment that improve device performance, reliability, yield or enabling new product are also solicited; the topics are substrates, isolation technologies, integration of heterogeneous channel materials, dielectrics and metal electrodes for gate stacks and MIM capacitors, shallow junctions, and silicides, low dielectric constant materials, contact and via processes, multi-patterning and EUV lithography, self-assembly techniques, deposition techniques include CVD, ALD and PVD, dry and wet etch techniques, cleaning, planarization, integration process for sensors, MEMS, RF devices, and photonics electronics, and process and tool design or process control techniques to reduce variation or improve reliability or yield.

Materials: papers in all areas of materials to achieve the higher performance and manufacturability, including materials for the deposition of films of semiconductor, magnetics, ferroelectrics, insulators, metals, liquid crystals are highly welcome; and

to achieve their structures, the resist, organic films, etching gas, and CMP materials and their chemical materials, gas chemistries, wafers, filament, phase change memory materials, cost down, reliability, high yield, manufacturability are also in our scope. Innovative materials for sensor and actuator achieving cloud and edge computing are highly welcome.

Reliability & Modeling: papers in all areas of numerical, analytical (including compact/SPICE) and statistical modeling and simulation of electronic, optical or hybrid devices, their interconnect, and 2D / 3D integration; in context of materials, fabrication processes, and devices, e.g. advanced physical phenomena (quantum mechanical and non-stationary transport phenomena, ballistic transport); Mechanical or electro-thermal modeling and simulation; Test structures and methodologies; Front-end and backend manufacturing processes; 3D integration and wafer-level packaging; Reliability of materials, processes, and devices; Advanced interconnects; ESD, latch-up, soft errors, noise and mismatch behavior, hot carrier effects, bias temperature instabilities, and EMI; defect monitoring and control; manufacturing yield modeling, DFM, analysis, and testing.

Important dates November 4, 2016:

Initial extended abstract submission deadline – one page text and one page Figure

December 12, 2016: notification of acceptance

January 16, 2017:

Final camera ready 3-page manuscript submission deadline

For more information, please visit the conference website, http://ewh.ieee.org/conf/edtm/2017.

Shuji Ikeda EDTM ExCom (Japan) tei Solutions Inc. Tokyo, Japan

# 2017 IEEE INTERNATIONAL MEMORY Workshop (IMW)

The 9th International Memory Workshop (IMW) will be held at the Hyatt Regency Monterey in California from May 14-17, 2017. The history of the IMW dates back to the NVSMW (Nonvolatile Semiconductor Memory Workshop) which began in 1976 and then later merged with the ICMTD (International Conference on Memory Technology and Design). The IMW is significantly broader in scope than its parent meetings, covering all memory types as well as the co-evolution of memory technology and memory system design. The workshop is focused on advancing innovation in memory technology and provides increased professional development and networking opportunities for attendees while still maintaining a small workshop experience. The IMW is sponsored by the IEEE Electron Devices Society and meets annually in May.

The IMW is the premier international forum for both new and seasoned technologists with diverse technical backgrounds to share and learn about the latest developments in memory technology with the global community. The scope of workshop content ranges from new memory concepts in early research to emerging technologies to the technology drivers currently in volume production. Topics include new and emerging device concepts, technology advancements, scaling and integration, circuit design and reliability, as well as emerging applications. Consistent with the increased importance of memory system architecture and integration, the workshop also includes increasing coverage of the evolving systems in which memories are deployed.

The IMW is the preeminent forum covering the latest developments, innovations, and evolving trends in the memory industry. Highlights from the 2016 workshop included invited talks from renowned industry and research leaders outlining their visions for 3D NAND Moore's law scaling acceleration, breakthroughs enabled by 3D X-point memory, the future of STT MRAM in mobile computing, the outlook for universal memory research, and the future of embedded memory technologyintherapidlyexpandingIOT market. Typical workshop attendance exceeds 250 attendees and the technical program begins with a full day short course given by renowned experts that provides an excellent professional development opportunity for both new and experienced technologists. The single-track program spans three days and also includes an evening poster session for informal

technical discussion with authors as well as a panel discussion with experts weighing in on a current hot topic. The technical program is organized to maximize networking opportunities and facilitate open information exchange among workshop contributors, committee members, and attendees. The program schedule includes ample time dedicated to social events including provided refreshment breaks, a workshop luncheon, and an evening banquet. The workshop is located in the beautiful Monterey Bay area, within close proximity to numerous area attractions and downtown Monterey.

On behalf of the organizing committee, I cordially invite you to participate in the 2017 IMW to continue to advance and/or stay current on both the latest and future innovations in the rapidly evolving memory industry. For additional information, including the call for papers, key dates, abstract submission instructions, registration information, and technical program details, please visit the IMW website for the latest updates: http://www. ewh.ieee.org/soc/eds/imw/. I look forward to seeing you in Monterey this May.

> Randy Koval 2017 IMW General Chair Intel

IEEE ResumeLab is Now Available!

ResumeLab allows IEEE members to use customized templates to create resumes/CVs, letters related to the employment process, portfolios of past work, skills profiles, and video resumes. The product also provides members with the ability to conduct mock interviews. Finally, everything created in the product can be shared with colleagues, mentors, potential employers, the

public, or social media via publicly-available links.

For more information about the product visit www.ieee.org/resumelab.

# SOCIETY NEWS

## Message from President-Elect

Fernando Guarin President Elect (2016-2017)

Dear Readers and **EDS Members:**

It is once again a true honor and privilege to write to you as the EDS President Elect 2016-2017. I will take this opportunity to outline my vision for the

direction in which our society should move in the years ahead. We live in interesting times and continue to reap the benefits brought about by the many contributions from EDS members that have shaped society and the world in which we live. Long gone are the days of the predictable path dictated by the traditional scaling of semiconductor devices. It is true that there remain many guestions to be answered about the particular embodiment of the electron devices that will dominate future applications in the same manner that Bipolar/CMOS semiconductor devices have done in the past decades. As we set our sights into the future, it is unquestionable that switching devices will provide a path to the future of a vibrant semiconductor industry and will continue to shape our world, enabling solutions to some of the great challenges we face. 1) Feeding and enabling health services for a growing population. 2) Cleaning and preserving our water supplies. 3) Processing the ever growing amounts of information that will grow even

more as we embrace the Internet of Things - IoT. 4) Enabling green energy to mitigate climate change. These solutions will be enabled in great measure thanks to the research and contributions of our EDS members in industry and academia throughout the world. The one goal that we must have as our guiding principle in all of our activities is the continued commitment of EDS to the realization of our vision of "Promoting excellence in the field of electron devices for the benefit of humanity." How do we continue to translate this vision into a reality? The central part of the answer is to provide our members with the infrastructure and network to enhance their skills in order to achieve the full potential of their careers. We will continue to impart excellence and leadership in our field by providing a vibrant network of teachers, colleagues and mentors. All with unsurpassed access to the required infrastructure that will serve and support our current and future members in all of the core areas of EDS; publications, conferences, education, awards and chapters all around the globe while we continue to grow our membership and work hard to reach out to young bright minds to replenish and invigorate the future of our society. EDS will continue offering programs that will enhance the skill set of our members at all levels (student, young professional and experienced professional members) providing training and exposure to

the research of fellow members in industry and academia. As our Society continues to organize webinars by leading experts from industry and academia in all of our fields of interest. We also provide a solid platform of leading publications, where our members can learn and share the fruits of their research in the field. EDS offers initiatives that will serve our students and young professionals in every corner of the world, offering STEM programs like EDS-ETC that will give them an opportunity to go out to their local environments and share their passion for engineering and keep the pipeline replenished with younger students. Our web content and open access publishing are growing progressively. We are enhancing our support of humanitarian projects enabling our students to form Special Interest Groups in Humanitarian Technology SIGHT. Our society will also encourage and support innovative, creative, and potentially disruptive approaches to the implementation of electron devices while serving the current and future needs of our members. As a closing remark, I would like to request your feedback and ideas on ways to continue improving the value of EDS to our members and to our society.

Fernando Guarin President Elect (2016–2017) **Global Foundries** East Fishkill, New York, USA Email: fernando.guarin@ieee.org

## Message from Editor-IN-Chief

M K Radhakrishnan Editor-in-Chief

**Dear EDS Members** and Readers,

I have been writing this column for the past 3 years as Editor-in-Chief of the Newsletter. From the very beginning of tak-

ing responsibility, and in every issue, I briefly wrote what topics were included and requested reader feedback. This message as well as some of the major changes in the content of the Newsletter was initiated in 2103 with the approval of the EDS leadership team. Major content changes include, an invited technical article explaining any significant technical development related to devices as a lead story written by an expert in a language digestible to all our members; a column of reflections from Young Professionals including an interview with a YP, and messages from the EDS leadership team. Apart from these, we the editorial team tried our best to speed up the Society news and Regional news to reach out to the members as fast as possible, within the publication frequency of the Newsletter. In the meantime, we also opened our Newsletter so that everyone can read irrespective of being an IEEE/EDS member or non-member with an online version available. We wanted to improve the Newsletter with technical briefs and technical content covering half the volume. Target set by me was about six years to develop it as a more versatile technical Newsletter useful to young professionals and students, and now we are only half-way through in our efforts. To my readers, I am afraid whether I will be able to fulfill my vows for the Newsletter as I may have to take a leave soon. However, recently we started getting very positive feedback from readers and I am happy that the efforts are being appreciated by the readers.

This issue of the Newsletter has a technical article on MEMTRONICS written by an expert team, a preview of the upcoming IEDM 2016, an interview of a young professional as the Reflections from YP and reports of a number of EDS mini-colloquia and Distinguished Lectures organized by many Chapters around the globe. These are apart from our usual columns, Society news and announcements.

As mentioned, we are in the process of transformation and to complete it in all respects we need cooperation and timely feedback - both critical and appreciative - from our members and readers. Again, that is why I am repeating the request to provide your candid opinion by e-mail to either: edsnewsletter@ieee.org OR to me radhakrishnan@ieee.org

> M. K. Radhakrishnan Editor-in-Chief, EDS Newsletter e-mail: radhakrishnan@ieee.org

# Message from VP Publications and Products

Hisayo S. Momose **FDS Vice-President** of Publications and **Products**

Dear fellow EDS Members:

It is my great pleasure to write to you as the new Vice President of Publications and Products. For over 30 years, since I started to research transistors in semiconductor area,

I have been really encouraged by this global professionals' community, EDS.

Our EDS publications' activities are critical to promote excellence in the field of electron devices. Emerging technologies have been expanding and changing rapidly. We would like to change and be more flexible to meet members' need and provide better service to the community.

Based on the paper download statistics from IEEE Xplore, our flagship journal, the IEEE Transactions on Electron Devices (T-ED) has been ranked among the top 10 in all IEEE publications, and our flagship letter, the IEEE Electron Devices Letter (EDL) has been top-ranked in the IEEE Letters publications. The submissions to our first open access (OA) journal, the Journal of Electron Devices Society (J-EDS) has been increasing year by year since it launched in 2013. We will promote strategically to make J-EDS one of the top-tiered topical OA publications in competing OA publications on device technology.

Last year we welcomed two new EiCs, Giovanni Ghione for T-ED and Tsu-Jae King Liu for EDL by the EiC selections using new EiC Selection and Evaluation Procedures for the EDS journals. We also welcomed Mickael Ostling as a new EiC of J-EDS this September. We will strive further to improve our

publications' value for EDS members. We hope researchers report any devices-related subjects in EDS publications as the first consideration.

We need to keep the quality of published papers as high as possible. In addition, to make our publications more attractive and timely, we need to catch new developing areas timely and increase submitted manuscripts in such emerging fields. In order to improve our journals further, your feedback is really appreciated. If you have any suggestions and comments, please let me know by email (h.s.momose@ieee. org) or Ms. Marlene James, Supervisor EDS Publications (m.james@ieee.org).

Sincerely, Hisayo S. Momose EDS Vice-President of Publications and Products Yokohama National University Yokohama, Japan

## EDS MEMBERSHIP FEE SUBSIDY PROGRAM (MFSP)

APPLICATIONS NOW BEING ACCEPTED FOR 2017 EDS MEMBERSHIP FEE SUBSIDY PROGRAM

Tian-Ling Ren EDS Vice-President of Membership and Services

Our society continually works to increase the value of EDS membership and our colleagues enjoy an incredible array of free and deeply-discounted, members-only benefits. One EDS initiative to encourage new-

comers and assist current members is the EDS Membership Fee Subsidy Program (MFSP). This program offers the generous incentive of one year complimentary IEEE and EDS memberships to help launch new chapters or enable existing ones, in low income geographical areas to grow their memberships.

This special offer is available to students and to those professionals who meet the eligibility requirements.

To complement our Society program, we are encouraging members in eligible countries to try IEEE e-Membership (an electronic membership option with reduced fees). Please visit the IEEE website for more details on e-Membership: http://www.ieee.org/membership\_services/membership/join/emember.html.

The EDS Membership Fee Subsidy Program policy is as follows:

- EDS will cover the cost of a full year of IEEE and EDS membership for up to 15 new or current members per chapter, provided the existing members have not received MFSP benefits in the past.

- Five of the fifteen members each year must be new IEEE/EDS members.

- New and renewing members must apply through their local chapter.

Current elected officials of eligible

- chapters will receive instructions from the EDS Executive Office.

- Chapter Chairs must verify member's eligibility according to IEEE income guidelines. A complete list of special circumstances eligible for reduced IEEE membership dues can be found on the IEEE website, at http://www.ieee.org/membership\_services/membership/cost/special\_circumstances.html.

Please visit the EDS website for more information on the EDS Membership Fee Subsidy Program: http://eds.ieee.org/mfsp. html. Any questions should be directed to Joyce Lombardini (j.lombardini@ieee. org), EDS Membership Administrator.

Tian-Ling Ren EDS Vice-President of Membership and Services Tsinghua University Beijing, China

# EDS VLSI TECHNOLOGY AND CIRCUITS TECHNICAL COMMITTEE

On June 15, 2016, the IEEE EDS *VLSI Technology and Circuits* Technical Committee (TC) met in Honolulu, Hawaii, USA during the 2016 Symposium on VLSITechnology, held June 13th–16th.

The mission of the VLSI Technology and Circuits TC's is to identify new technical trends, help foster new technical concepts, and serve the emerging needs of the Electron Devices and Solid-State Circuits communities in VLSI. The committee members include many well recognized technical experts representing a wide spectrum of technical mastery in VLSI devices, technology, and circuits.

In pursuing the objective to identify new and relevant areas of interest to the Electron Devices and Solid-State Circuits communities, the committee recommends any or all of the following based on the nature of the areas:

Initiate topical workshops of current interest (attached to existing

- conferences or incorporated in new ones)

- Promote special issues for major publications (e.g., T-ED, J-EDS)

- Sponsor panel session topics, invited talks and special sessions for major conferences

The topics discussed during the June 15, 2016 meeting included: Committee membership and regional participation, Sub-Committee roles and responsibilities and EDTM support.

Based on strong manufacturing technologies, Asia has the potential to take the initiative for system integration. Deep-diving discussions among societies on material, process and devices are essential to accelerate manufacturing innovations through this conference.

The Inaugural EDTM – Electron Devices Technology and Manufacturing will be a full three-day conference to

be held at Toyama International Conference Center, Japan, from February 28th to March 2nd, 2017, fully sponsored by the IEEE Electron Devices Society (EDS). As semiconductor technology scaling challenges continue to grow, the industry must increase collaborative efforts to overcome them. EDTM serves as a forum for the electron devices community to collaborate on topics ranging from devices, materials, and tools, to create new and innovative technologies.

For further details please contact Dr. Reza Arghavani (Reza.Arghavani@lamresearch.com), Conferences/Workshops Subcommittee Chair, or Dr. Shu Ikeda (shu.ikeda@tei-solutions.com) Committee Chair.

Reza Arghavani EDS VLSITC Committee Member Lam Research Corporation Fremont, CA, USA

# IEEE/OSA JOURNAL OF DISPLAY TECHNOLOGY (JDT)

Dear EDS Members:

The IEEE/OSA Journal of Display Technology (JDT) will cease publication with its October-December 2016 issue, due to be published early December 2016. This publication, along with its archived content, will continue to be accessible to EDS members on the IEEE Xplore platform as part of your membership benefits. The IEEE has a number of highly-

cited journals that will be accepting papers which cover appropriate segments of the IEEE/OSA JDT's focus area. Within the Electron Devices Society (EDS), we hope you consider one of our following journals for your manuscript submis-

1) IEEE Journal of the Electron Devices Society (J-EDS), an Open Access (OA) publication;

- 2) IEEE Transactions on Electron Devices (T-ED);

- 3) IEEE Electron Device Letters (EDL).

Sincerely,

Hisayo S. Momose EDS Vice-President of Publications and Products Yokohama National University Yokohama, Japan

# LETTERS TO THE EDITOR

Dear Editor,

I'd like to offer my praise for an excellent article! As a semiconductor-

physics-challenged electrical engineer, it is quite an accomplishment for Mayank Shrivastava and V. Ramgopal Rao to 1) keep my attention for a full article and 2) get me to understand most of the physics behind the devices. I found their Technical Brief "Tunnel Field Effect Transistors: Past, Present, and Future" in the July 2016 issue fascinating and easy to read. I thoroughly enjoyed the article.

> Jim (James) Ford Principal Engineer

MK, I always enjoy perusing the newsletter, helps keep me in touch and very much appreciate your diligence with the newsletter.

> Randy Rannow Apichip.com Culver City, California

# Volunteers Needed for IEEE Humanitarian Programs

In recent years, IEEE has placed great emphasis on Humanitarian Technology Activities as part of its strategic efforts to advance technology for the good of humanity. A program called Special Interest Group on Humanitarian Technology (SIGHT) was created to further these efforts.

EDS members interested in devoting their time and talents to an IEEE humanitarian project will find that there are many opportunities.

We encourage current EDS chapters to form a SIGHT group and qualify for the \$250 seed funding.

Should you submit a proposal to start a new SIGHT group and participate in any of the IEEE humanitarian programs, please make sure to indicate the Electron Devices Society as your Operating Unit (OU).

For more details on this program, visit the IEEE SIGHT webpage: http:// www.ieee.org/special\_interest\_ group\_on\_humanitarian\_technology. html.

# CALL FOR NOMINATIONS FOR IEEE ELECTRON DEVICES SOCIETY NEWSLETTER EDITOR-IN-CHIEF

Since July 1994, the IEEE Electron Devices Society (EDS) Newsletter has been a flagship publication of the IEEE Electron Devices Society (EDS). The EDS Newsletter, published quarterly, covers regional and chapter activities, technical meetings, awards and other news and initiatives of the society. The EDS Newsletter publishes technical articles and reports from experts providing a general outline or standing in the respective areas of field of interest of EDS to our readers. Two sections on Young Professionals (YP) and Chapters News are included to encourage YP participation and highlight the activities of vibrant Chapters. Messages from the EDS Officers (President, President-Elect, Secretary, Treasurer) and VPs appear in each issue to highlight the current and future evolutions of EDS.

We invite nominations for the position of Editor-in-Chief (EiC) for the EDS Newsletter for a 3-year term beginning in **January of 2017**.

The EiC's duties include supervising the operations of the EDS Newsletter with the assistance of the EDS publications staff and collaboration of Regional Editors; monitoring the quality and timeliness of publications in its paper and e-formats; editing, reviewing and proof reading all articles published in the EDS Newsletter; inviting Technical Articles from experts, messages of EDS Officers and VPs, and articles from Vibrant Chapters; conducting interviews of Young Professionals; recommending Regional Editors to serve across the scope of the journal; leading development to strengthen the Newsletter; reporting to the EDS Newsletter Oversight Committee twice per year and take up actions for the next period.

#### **Criteria for the Nominees:**

Ability and motivation to spend sufficient time on the job;

- Demonstrated technical leadership in EDS field-ofinterest and commitment to volunteer;

- Formal support from the institution for which the nominee works (waived if self-employed);

- Has served or currently is serving as editor at the Regional level or as experienced editor at other EDS publications.

- Be a member of EDS and willing to support EDS procedures and policies;

- Commitment to guiding the publication according to this Call for Nominations;

- In addition, the EIC must demonstrate a willingness to work collaboratively with internal and external stakeholders so to ensure the advancement of the society's vision and mission as well as the technical and fiscal health of the Newsletter.

#### **Requirement for Nominations:**

- A brief IEEE-style biography (up to 250 words) of the nominee;

- A complete CV and list-of-publications of the nominee;

- A brief statement from the nominator on nominee's qualification and how the nominee meets the criteria listed above;

- A letter from nominee's employer indicating support for the EiC activity;

- Endorsement from two EDS members on the nomination;

- Optionally, a statement (up to 500 words) from the nominee on his/her vision for the journal.

Please email the nomination materials to: Marlene James (m.james@ieee.org) no later than October 31, 2016.

Simon Deleonibus Secretary IEEE Electron Devices Society

### $oldsymbol{\mathsf{A}}$ wards and $oldsymbol{\mathsf{R}}$ ecognitions

## 2015 EDS PAUL RAPPAPORT AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. Every year, the Society confers its prestigious Paul Rappaport Award to the best paper published in the IEEE Transactions on Electron Devices. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The winning paper was selected from over 600 articles that were published in 2015. The winning paper is entitled "Noise-Induced Resistance Broadening in Resistive Switching Memory—Part I: Intrinsic Cell Behavior/ Part II: Array Statistics." This paper was published in the November 2015 issue of the IEEE Transactions on Electron Devices, and was authored by Stefano Ambrogio, Simone Balatti, Vincent McCaffrey, Daniel C. Wang and Daniele lelmini.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 5, 2016, in San Francisco, California. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Stefano Ambrogio received the M.S. and Ph.D. degrees in Electrical Engineering from Politecnico di Milano, Italy, in 2012 and 2016. His main research interests are electrical characterization, modeling and neuromorphic computing of resistive switching memories (RRAM, PCM). He is first author of nine papers on peer-reviewed journals and has given talks in various international conferences (IEDM, VLSI, and MRS).

Simone Balatti received the B.S., M.S., and Ph.D. degrees from the Politecnico di Milano, Milan, Italy, in 2009, 2011, and 2015, respective-

ly, all in electrical engineering. He is currently a Device Engineer with Intermolecular, Inc., San Jose, CA, USA. His current research is focused on the study of novel devices for memory applications.

Daniele lelmini, Ph.D., is an Associate Professor at Dipartimento di Elettronica, Informazione e Bioingegneria, Politecni-

co di Milano. He conducts research on emerging nanodevices, such as phase change memory (PCM) and resistive switching memory (RRAM). He published more than 250 papers in peer-reviewed journals and international conferences. He received the Intel Outstanding Researcher Award in 2013 and the ERC Consolidator Grant in 2014. He is a Senior Member of the IEEE.

Vincent McCaffrey received the BS degree in electronic engineering from University College, Dublin, Ireland, in 1981. Since then, he has

worked in the semiconductor industry in the fields of technology reliability and product engineering for FPGA's and non-volatile memories. He is currently employed at Maxim Integrated, working on the characterization, reliability, and qualification of power management ICs.

Daniel C. Wang was born in Tainan. Taiwan, in 1965. He received his B.S. degree in electrical and computer engineering from National

Central University, Taiwan in 1988, and the M.S. and Ph.D. degrees in electrical engineering from University of Florida, USA in 1992 and 1996, respectively.

He is a Senior Member of Technical Staff at Adesto Technologies. His current research interests include nonvolatile memory operation and device reliability with a special focus on resistive-switching memory and conductive-bridge memory.

Hisayo S. Momose EDS Vice-President of Publications and Products Yokohama National University Yokohama, Japan

## 2015 EDS GEORGE E. SMITH AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. The George E. Smith Award was established in 2002 to recognize the best paper appearing in a fast turnaround archival publication of EDS, targeted to the IEEE Electron Device Letters. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The paper winning the 2015 George E. Smith Award was selected from 400 articles that were published in 2015. The paper is entitled, "First Demonstration of Amplification at 1 THz Using 25 nm InP High Electron Mobility Transistor Process." This paper appeared in the February 2015 issue of the IEEE Electron Device Letters and was authored by Xiaobing Mei, Wayne Yoshida, Mike Lange, Jane Lee, Joe Zhou, PoHsin Liu, Kevin Leong, Alex Zamora, Jose Padilla, Stephen Sarkozy, Richard Lai, and William R. Deal.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 5, 2016, in San Francisco, California. In addition to the award certificate, the authors will receive a check for \$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Xiaobing Mei received his Ph.D. degree in electrical engineering from University of California, San Diego in 1997. He is a Senior Staff En-

gineer at Northrop Grumman's Micro Electronics Center, leading advanced InP HEMT technology development.

Wavne Yoshida received a B.S. in Chemical Engineering from the California Institute of Technology and Ph.D. in Chemical Engineering from

UCLA. He has worked for Northrop Grumman in the field of advanced lithography since 2003, and currently serves as Technical Lead for the Electron Beam Lithography group in the Microelectronics Process Department.

Michael D. Lange received his Ph.D. from the University of Illinois at Chicago in 1993. From 1986 to the present, he has worked in R&D of compound

semiconductor materials by MBE. In 2002, he joined Northrop Grumman Aerospace Systems for R&D of compound semiconductor materials and structures for transistor circuits.

Jane Lee worked as a semiconductor process engineer in Northrop Grumman for over 30 years. Jane received a Master of Science degree in

metallurgical engineering from Ohio State University, a Master of Science degree in chemistry from University of Notre Dame and a Bachelor of Science degree in chemistry from National Taiwan University.

Joe Zhou received his B. S degree in Metallurgical engineering from Northeast University of China, in 1984, and his Ph.D. degree in metallurgical engineering from University of Missouri in 1996. He was a Staff Engineer at Northrop Grumman's Micro Electronics Center, leading advanced InP HEMT technology in backside process development.

Po-Hsin Liu was the research and production lead of the advanced Ebeam lithography group at Northrop Grumman Aerospace Systems for

over 30 years. He has recently retired in 2016 after 36 years of distinguished service at Northrop Grumman.

Kevin Leong received a B.S. degree from University of Hawaii and Ph.D. degree from UCLA, both in electrical engineering. From

2004 to 2007, he was a postdoctoral researcher at UCLA. Currently, he is a staff engineer at NGAS where he is involved in high frequency MMIC and package design.

Alexis Zamora earned his B.S. and M.S. degrees in electrical engineering from the University of Hawaii at Manoa in 2008 and 2010.

respectively. Since 2011 he was been a staff engineer at Northrop Grumman Aerospace Systems, Redondo Beach, CA, where he predominantly does MMIC design on various III-V technologies. His main area of interest is InP-HEMT-based high frequency electronics.

Jose Padilla is the Transmitters & Receivers section manager for the

Radio Frequency & Mixed Signal department at Northrop Grumman Aerospace Systems. He has more than 20 years of experience

veloping advanced technologies and products in the RF electronics and photonics fields in the aerospace, defense, and commercial industries.