OCTOBER 2017 VOL. 24, NO. 4 ISSN: 1074 1879

EDITOR-IN-CHIEF: CARMEN M. LILLEY

## TABLE OF CONTENTS • Highlights of the 2017 IEEE Photovoltaic Specialists Conference • 2017 IEEE International Electron Devices Meeting (IEDM) • 2017 IEEE Semiconductor Specialists Conference (SISC) • 2018 IEEE International Memory Workshop (IMW) Message from EDS President-Elect • Message from Editor-in-Chief • Message from EDS Vice President of **Publications and Products** • EDS Photovoltaic Devices Technical Committee Report • Message from EDS Women in Engineering Liaison EDS/Women in Engineering Co-sponsor Entrepreneur Luncheon at IEDM • EDS Members Recently Elected to IEEE Senior Member Grade Award Recipients and Call for Nominations . . . . 16 • 2016 EDS Paul Rappaport Award Winners • 2016 EDS George Smith Award Winners • 2017 William R. Cherry Award - Call for Nominations YOUNG PROFESSIONALS ...... 18 • Organizing IEEE EDS STEM Workshops for Kids to Build Electronic Circuits • EDS-ETC in Silicon Valley (ED Santa Clara Valley/San Francisco Chapter) • ED Sri Jayachamarajendra College of **Engineering Vacation Project Mania** • EDS-ETC Program at ED University of Calcutta DLs, MQs and Conference Reports EDS MEETINGS CALENDAR......42

# **IEEE**

INTEREST STATEMENTS ......44

EDS VISION, MISSION AND FIELD OF

## TECHNICAL BRIEFS

# HIGHLIGHTS OF THE 2017 IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE

The international 2017 IEEE Photovoltaic Specialists Conference, also called PVSC-44, was held June 25–30, 2017, at the Marriott Wardman Park Hotel in Washington, D.C. The PVSC-44 is the leading international conference on PV science and technology and one of the flagship conferences of IEEE sponsored by the Electron Devices Society. Being a highly interactive venue for both seasoned PV experts as well as entry-level professionals and students, the PVSC-44 provided a unique opportunity to meet share and discuss PV-related developments in a timely, influential forum. The conference had therefore 1,298 attendees from 43 different countries out of which 57% came from the USA, 8% from Japan, 4% from Germany, 3% from Australia, 3% from China and the remaining 25% from other nations. During the conference, 986 presentations took place; 62% of these presentations were posters, which were partly shown by interactive e-poster boards.

The PVSC conference is well known for its strong awards program's. This year's recipient of the William R. Cherry Award was Eli Yablonovitch (Berkeley University, USA) in recognition of his many contributions to solar cell device physics and technology, among which strained semiconductor lasers and photonic crystals. The Young Professional Awardee was Weiwei Deng (State Key Laboratory of PV Science and Technology, China) for her work on the development of low cost mono- and multi-crystalline silicon PERC solar

(continued on page 3)

#### YOUR COMMENTS SOLICITED

Your comments are most welcome. Please write directly to the Editor-in-Chief of the Newsletter at edsnewsletter@ieee.org

## ELECTRON DEVICES SOCIETY

#### President

Samar Saha Prospicient Devices E-mail: samar@ieee.org

#### President-Elect

Fernando Guarin GlobalFoundries E-mail: fernando.guarin@ieee.org

#### Treasurer

Secretary

Subramanian S. Iyer UCLA E-mail: iyer@ieee.org

Simon Deleonibus CEA-LETI E-mail: simon.deleonibus.1992@ ieee.org

#### Jr. Past President

Albert Z.H. Wang University of California, Riverside E-mail: aw@ee.ucr.edu

#### Sr. Past President

Paul K.L. Yu University of California at San Diego E-mail: p.yu@ieee.org

## Vice President of Membership and Services

Tian-Ling Ren Tsinghua University

E-mail: rentl@mail.tsinghua.edu.cn

## Vice President of Publications and Products

Hisayo Momose Yokohama National University E-mail: h.s.momose@ieee.org

#### Vice-President of Regions/ Chapters

M.K. Radhakrishnan NanoRel

E-mail: radhakrishnan@ieee.org

## Vice President of Technical Committees & Meetings

Ravi Todi GlobalFoundries E-mail: rtodi@ieee.org

#### **IEEE Newsletters**

Theresa Smith IEEE Operations Center E-mail: tlsmith@ieee.org

#### **Operations Director**

James Skowrenski IEEE Operations Center E-mail: j.skowrenski@ieee.org

#### **Membership Administrator**

Joyce Lombardini IEEE Operations Center E-mail: j.lombardini@ieee.org

IEEE prohibits discrimination, harassment, and bullying. For more information, visit http://www.ieee.org/web/aboutus/whatis/policies/p9-26.html.

#### EDS Board of Governors (B0G) Elected Members-at-Large

Elected for a three-year term (maximum two terms) with 'full' voting privileges

| <u>2017</u>                                                                         | TERM                                                 | <u>2018</u>                                                                                       | TERM                                | 2019         | Term                                          |

|-------------------------------------------------------------------------------------|------------------------------------------------------|---------------------------------------------------------------------------------------------------|-------------------------------------|--------------|-----------------------------------------------|

| Z. Celik-Butler S. Chung M. Farooq P. Fay C. Lilley D. Misra H. S. Momose T. L. Ren | (2)<br>(2)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1)<br>(1) | N. Bhat<br>D. Camacho Monte<br>S. Deleonibus<br>M. leong<br>M. Polavarapu<br>R. Todi<br>D. Verret | (1)<br>ejo (2)<br>(1)<br>(1)<br>(1) | J. Burghartz | (1)<br>(2)<br>(1)<br>(1)<br>(1)<br>(2)<br>(1) |

| I. L. 11011                                                                         | (2)                                                  |                                                                                                   |                                     |              |                                               |

## NEWSLETTER EDITORIAL STAFF

#### **Editor-In-Chief**

Carmen M. Lilley University of Illinois at Chicago E-mail: clilley@uic.edu

## REGIONS 1-6, 7 & 9

Eastern, Northeastern & Southeastern USA (Regions 1,2 & 3)

Mukta Farooq GlobalFoundries E-mail: mukta.farooq@ globalfoundries.com

## Central USA & Canada (Regions 4 & 7)

Michael Adachi Simon Fraser University E-mail: mmadachi@sfu.ca

## Southwestern & Western USA (Regions 5 & 6)

Kyle H. Montgomery Air Force Research Laboratory E-mail: kyle.h.montgomery@ieee.org

#### Latin America (Region 9)

Joao Antonio Martino University of Sao Paulo E-mail: martino@lsi.usp.br

### REGION 8

## Eastern Europe

Daniel Tomaszewski Institute of Electron Technology E-mail: dtomasz@ite.waw.pl

## Scandinavia & Central Europe

Mariusz Orlikowski Lodz University of Technology E-mail: mariuszo@dmcs.p.lodz.pl

#### UK, Middle East & Africa

Jonathan Terry

The University of Edinburgh

E-mail: jonterry@ieee.org

#### Western Europe

Jan Vobecky Abb Switzerland Ltd. E-mail: vobecky@fel.cvut.cz

## REGION 10 Australia, New Zealand & South East Asia

P Susthitha Menon Universiti Kebangsaan Malaysia E-mail: susi@ukm.edu.my

#### Northeast Asia

Kuniyuki Kakushima Tokyo Institute of Technology E-mail: kakushima@ep.titech.ac.jp

#### **East Asia**

Ming Liu Institute of Microelectronics E-mail: liuming@ime.ac.cn

#### South Asia

Manoj Saxena University of Delhi E-mail: msaxena@ieee.org

### CONTRIBUTIONS WELCOME

Readers are encouraged to submit news items concerning the Society and its members. Please send your ideas/articles directly to either Editorin Chief or the Regional Editor for your region. The e-mail addresses of all Regional Editors are listed on this page. E-mail is the preferred form of submission.

### NEWSLETTER DEADLINES

ISSUE DUE DATE

January October 1st

April January 1st

July April 1st

October July 1st

The EDS Newsletter archive can be found on the Society web site at http://eds.ieee.org/eds-newsletters.html. The archive contains issues from July 1994 to the present.

**IEEE Electron Devices Society Newsletter** (ISSN 1074 1879) is published quarterly by the Electron Devices Society of the Institute of Electrical and Electronics Engineers, Inc. Headquarters: 3 Park Avenue, 17th Floor, New York, NY 10016-5997. Printed in the U.S.A. One dollar (\$1.00) per member per year is included in the Society fee for each member of the Electron Devices Society. Periodicals postage paid at New York, NY and at additional mailing offices. Postmaster: Send address changes to IEEE Electron Devices Society Newsletter, IEEE, 445 Hoes Lane, Piscataway, NJ 08854.

Copyright © 2017 by IEEE: Information contained in this Newsletter may be copied without permission provided that copies are not used or distributed for direct commercial advantage, and the title of the publication and its date appear on each photocopy.

## HIGHLIGHTS OF THE 2017 IEEE PHOTOVOLTAIC SPECIALISTS CONFERENCE

(continued from page 1)

cells with world record efficiencies. Richard King (Arizona State University, USA) was elevated to the level of IEEE Fellow. Further, many Best Student Paper Awards and Poster Awards were issued in various categories. A full listing of the award winners can be found on the PVSC-44 website under the Awards menu.

The PVSC-44's Technical Program included 12 areas covering cuttingedge developments in photovoltaics, ranging from fundamentals to applications, with an emphasis on material science, devices, PV systems, solar resources and policy. The PVSC-44 was opened by an excellent Keynote presentation by Charlie Gay (Department of Energy, USA). At present the technical program can be easily digitally explored at http://www .ieee-pvsc.org/PVSC44. However, to give the reader focused insights on the conference's vast program, this Technical Brief provides an overview of the conference highlights per area.

Area 1 was on Fundamentals and New Concepts for Future Technologies and kicked off with a Plenary talk by Jean-Francois Guillemoles of the IRDEP at CNRS, who spoke about hot carrier solar cells and some of the illusions surrounding them. After first presenting an excellent overview of hot carrier effects in semiconductors, he then described the hyperspectral photoluminescence imaging technique that allows the carrier temperature and electrochemical potential of electrons and holes to be determined unambiguously. Insights on hot carrier solar cell design included not simply requiring slowed cooling, but control of all of the processes, as well as the selective energy contact operation. Lars Samuelson of Lund University opened an exciting Nanowire (NW) Photovoltaics special session. Lars first reviewed the growth and applications of nanowire arrays in the early days, followed by the development of nanowire photovoltaics in nanophotonics. Topics include 15.3% record efficiency of GaAs NW in 2015, substrate reuse via NW thin film peel-off, and tandem junction NW cells. He also introduced the

aerotaxy method of single crystalline NW synthesis as a low-cost means to the mass production of NWPV. Until recently, Selenium photovoltaics remained overlooked and stalled with a low efficiency record of 5%. Douglas Bishop from IBM T.J. Watson Research Center demonstrated a 30% increase in efficiency and a simultaneous reduction in thickness by a factor of five. Due to their bandgap, these low cost Se devices look very promising for indoor applications, such as powering Internet of Things (IoT) devices.

The Area 2, Chalcogenide Thin Film Solar Cells, Plenary was given by Dr. Markus Gloeckler from First Solar who spoke about the company's relentless advances in quality and efficiency and their record of moving drastic innovations in the cell technology into production within 2 years. First Solar is scaling production on 440  $W_{\tiny peak}$  Series 6 modules that are over three times as large as prior modules. The use of CdSeTe bandgap grading to ~1.4 eV at the front of the cell increases J<sub>sc</sub> dramatically, while ZnTe back

Winners of the Best Student Paper Award, (Back Left to Right) Geoff Bradshaw (Awards Chair), Ilke Celik, Klemens K. Ilse, Seonyong Park, Jeremie Werner, Bradley M. West, Mallory A. Jensen, Amit Munsh, Natasha E. Hjerrild, (From Left to Right) Angele Reinders (General Chair) and Seth Hubbard (Program Chair), (Student Award Winners not in photo) Sven Killinger, Xiaochen Zhang, Illya Nayshevsky, Boju Gai

contacting controls Cu migration thus making the modules extremely stable. As well, Area 2 had multiple presentations from First Solar, IEC Delaware, and NREL reporting significant advances in p-doping CdTe using P, As, and Sb rather than Cu, providing a strategy for reaching greater than 1 V V ... Walajabad Sampath's group at Colorado State University reported the highest-ever efficiency CdTe cell (not produced by First Solar) at 19.1%. Paul Haney of NIST detailed a recently developed analytical framework for V<sub>oc</sub> loss from grain boundaries in polycrystalline solar cells including complex grain boundary networks. Lars Stolt of Solibro reported 17% modules and plans to double the module area to 1.88 m.

The Area 3 sessions on *III-V* and *Concentrator Technologies* were jampacked this year, with lots of new and exciting work regarding III-V technology. Plenary speaker Stefan Myrskog, VP of Control Systems at Morgan

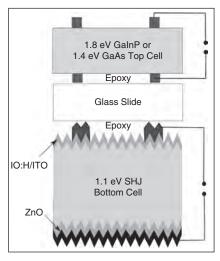

Fig. 1(a). Schematic cross section of the mechanically stacked III-V/Si dual-junction solar cells with record one-sun efficiencies up to 32.8% (© 2017 IEEE) Proceedings of the 2017 PVSC-44. "Mechanically stacked 4-terminal III-V/Si tandem solar cells" Stephanie Essig, Christophe Allebé, John F. Geisz, Myles A. Steiner, Loris Barraud, Antoine Descoeudres, J. Scott Ward, Manuel Schnabel, David L. Young, Matthieu Despeisse, Christophe Ballif, Adele Tamboli

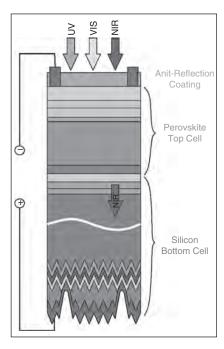

Solar, provided an overview of their development of solid, thin-plate CPV modules using innovative optics concepts borrowed from the optical communications field. Their newest designs are based on a standard Si industry bill of materials and have applications ranging from cost effective utility scale generation to multi-purpose building integrated systems. Area 3 invited speaker Stephen Forrest (University of Michigan) discussed methods for wafer reuse requiring no polishing, as well as new tracker concepts based on kirigami, the Japanese art of paper folding and cutting. John Geisz of NREL gave an insightful tour of NREL's effort toward the development of a 6-junction concentrator cell. A special session was held this year dedicated to results from the ARPA-E MOSAIC program, with an introduction from invited speaker, and MOSAIC program manager, Michael Haney. A range of innovative and fascinating module designs were presented, with the goal of a Moore's Law type system level scaling for CPV. Finally, a joint session on "Hybrid Tandems" pitted III-V and perovskite based Si tandems in a battle for the best. Record results include a 32.3% 2-terminal III-V/Si cell (Frank Dimroth, Fraunhofer ISE), a 23.6% monolithic Perovskite/Silicon (Zhengshan Yu, ASU, in collaboration with Stanford) and 32.5% and 32.8% III-V/Si cells (Stephanie Essig, EPFL, in collaboration with NREL and CSEM). The two Most Outstanding Technical Contributions to the PVSC-44 were awarded in this area to Stephanie Essig for her III-V/Si dual-junction solar cells (Fig. 1a) and their challenging path towards cost competiveness, and Zhengshan Ju, who presented record results on monolithic perovskite/silicon tandem devices (Fig. 1b).

Area 4 was on Silicon Photovoltaic Materials and Devices. The Plenary was given by Pietro Altermatt of Trina Solar. Pietro presented their most recent research in High-Performance (HP) multicrystalline p-type Si, show-

Fig. 1(b). Schematic of the monolithic Perovskite/Silicon tandem solar cell, with record-breaking efficiency of 23.6%

ing that the reduction in dislocations due to the HP mc-Si process and the reduction in Fe impurities in the Si material has already allowed for a record efficiency of 21.25% (total area on 156 mm wafers). He also give a plan to reach efficiencies greater than 22% in the future. If contaminants such as Fe and Cu are sufficiently reduced, the performance of mc-Si can be as good as mono-crystalline CZ solar cells. In other Area 4 news, Kunta Yoshikawa (Kaneka) announced the current world record single-junction Si device using a backside contact hetero-junction structure with a 26.7% efficiency. Stefan Glunz (Fraunhofer ISE) reported on the development of TOPcon passivated contact cells with efficiency up to 25.3% and a world record n-type multi-Si cell with an efficiency of 21.9%. Weiwei Deng (Trina Solar) presented her research leading to a 22.61% efficient PERC Silicon solar cell. Johnson Wong (SERIS) presented on Griddler Al (artificial intelligence), a Luminescence Image Analysis program using a Finite Element simulator that seeks

cell parameters that can best explain a set of luminescence imaging data. The fitted cell parameters (contact resistance spatial distribution, saturation current densities of the wafer's passivated regions and under the metal contacts) lead to simulated I-V characteristics that are in agreement with experimental data.

Area 5, Characterization Methods, had plenary speaker David Ginger from the University of Washington. He presented on the realization of correlative scanning and optical microscopies to probe perovskites. Informative photoluminescence maps of grains and interfaces before and after chemical treatment were also presented, showing a guideline to diagnose the sources of non-radiative recombination within any PV material. Area 5 also provided a fantastic special session on synchrotronbased characterization methods to advance the understanding of lightinduced effects in perovskites. Laura Schelhas, from SLAC, discussed how in-operando X-ray diffraction reveals the relevant structural changes that take place in perovskites as a function of temperature. Jeremy Poindexter, from MIT, resolved the chemical composition distribution in perovskite grains with high spatial resolution by X-ray fluorescence. Finally, during a session on novel scanning probe microscopy approaches, Pablo Garrillo, from CEA in Grenoble, presented the use of multi-temporal photo-carrier dynamics at the nanoscale. As well, Julia Deitz, from Ohio State University, gave an outstanding presentation on how EELS can be realized to help us understanding the origin of deep level defects in CIGS.

In Area 6 Perovskite and Organic Solar Cells, Michael McGehee of Stanford University delivered an excellent overview on recent progress and development of perovskite solar cells. He showed promising thermal cycling results for addressing the big challenges to perovskites with stability results indicating the potential for long-term performance. The focus of his

group's work is on improving stability and lowering costs and their work on a perovskite-silicon tandem devices was highlighted. As result of this work, a world record efficiency of 23.6% for 1 square centimeter monolithic perovskite Si tandem solar cell was demonstrated. Alex Zunger (University of Colorado) gave an exciting invited talk to discuss rational materials discovery for perovskites and the limitations and promise of newly discovered families of materials. Finally, both CSEM and EPFL demonstrated perovskite modules with steady-state aperture area efficiencies as high as 16% and a geometrical fill factor of 92.

For the Area 7 Space and Specialty Technologies plenary, we were pleased to welcome a talk from Christophe Allaud of OneWeb who presented on "Low Cost Applied to Large Constellations" for their ambitious goal to provide global highspeed internet access. Christophe's presentation demonstrated the manufacturing and automated assembly plans needed to achieve their production plans of over 900 satellites per year. The first generation of satellites plan to utilize triple junction III-V solar cells generating around 500 watts and would have an expected mission life of 6 years. Don Walker from Aerospace Corporation demonstrated that individual subcell parameters of a GalnP/GalnAs/Ge triple junction solar cell irradiated by 1 MeV electrons can be derived utilizing the spectral reciprocity relation between electroluminescence and external quantum efficiency. Gordon Wu and Bao Hoang from Space Systems Loral (SSL) discussed a new analytical tool for accurate shadow prediction of space solar, using a combination of CAD modeling, raytracing and simulation of solar cell performance under various levels of illumination. Louise Hirst from the Naval Research Laboratory presented results for ultra-thin GaAs cells with potential for superior radiation hardness.

In the Area 8 PV Modules, Manufacturing, Systems and Applications,

Plenary Christophe Ballif of EPFL presented us with a fascinating overview of concepts for improving module performance as well as his concepts for unique PV applications. His work on PV modules that reflect light in the visible range drew the most attention. This interesting technology can be used to make whitelooking modules but also unlimited textures and even images, thus hiding the fact that PV modules are present at all, and opening up additional applications where aesthetics trump economics. Kyumin Lee of CFV Solar Test Laboratory demonstrated that once the temperature dependence of the series resistance is included, the single-diode model can reproduce I-V curves with greater accuracy. Multiple groups presented on irradiance modeling for bifacial PV applications, showing significant progress and consistent results, including validations of field measured data. Bruce King of Sandia presented on the degradation of 6 CIGS modules typologies and observed two populations with respect to degradation in maximum power. One population of older products displayed a high degradation rate of 2%/year or greater while the second, contemporary population displayed degradation of less than 0.5%/year.

In the Area 9 PV and System Reliability, Plenary John Trout from Dupont summarized the use of field data and accelerated testing data to better understand materials durability. Data from 200 systems including 2 million modules showed 7.5% observation of problems with back sheets and 11% observation of problems related to cells. The accelerated test sequence correlating best with field data included damp heat, UV, and thermal cycling and found 1000 h of damp heat exposure correlated to backsheets and 2000 h correlated to cell corrosion. Dirk Jordan of NREL presented how yearon-year calculations of degradation rates are "the best thing since sliced bread." Olga Lavrova from Sandia showed how several factors limit the potential shock hazard to firefighters encountering rooftop PV arrays, among them the resistances in their protective gear and the high effective resistance of ungrounded arrays. Nick Bosco (NREL) quantified the adhesion strength needed to avoid delamination in fielded modules. Robert Witteck (ISFH, Germany) presented UV light degradation of front surface recombination by breaking the H bond in SiNx. Finally, Volker Naumann of Fraunhofer CSP identified specific surface defects causing potential-induced degradation (PID).

The Area 10 Power Electronics and Grid Integration Plenary saw Thomas Bialek (San Diego Gas and Electric) first describe the current challenges of high penetration PV integration, including the variability issues of PV generation and the lack of hightemporal resolution visibility that utilities have traditionally used to operate their systems. Tom discussed how advanced PV inverter capabilities can mitigate many undesirable impacts by managing reactive power in the grid and buildings in bulk system support in distribution-connected PV to maintain overall system reliability. Mahesh Morjaria (First Solar Inc.) gave a well-received invited talk on reducing costs of installed solar energy, flexibility and Automated Generator Control (AGC) capabilities of PV. Sigfredo Gonzalez (Sandia) presented definitions and simulation results of 6 classes of PV inverter unintentional islanding capability.

In the Area 11 Solar Resources for PV and Forecasting Plenary, Steven Steffel of Pepco Holdings Inc. give a broad overview of some of the challenges faced when integrating renewables into the electricity grid and some of the opportunities for PV in particular to play a vital role

on the grid of the future. He showed how the grid of the future will need advanced monitoring and secure communications for existing infrastructure, advanced modelling for geolocating generators, as well as smart algorithms in order to balance load and distributed generation. The importance of PV in terms of ancillary services such as voltage regulation will also continue to grow in the future. In a joint session with Area 10, Nicholas Engerer (The Australian National University) demonstrated a forecast of PV production in Australia, using the advanced Himawari satellite data (10 min., 1 km resolution), showing impressive accuracy for short term forecasts. Yu Xie (NREL), gave an excellent overview of a new improved rapid radiative transfer model for estimating solar resources from satellite observations. The Fast All-sky Radiation Model for Solar applications (FARMS) uses the simulation of clear-sky transmittance and reflectance and a parameterization of cloud transmittance and reflectance to rapidly compute broadband irradiances on horizontal surfaces. The accuracy of FARMS is comparable to that of two-stream approximation, but it is almost 1,000 times faster.

Finally, the Plenary talk for Area 12 PV Deployment and Sustainability featured Becca Jones-Albertus from the U.S. Department of Energy's SunShot Office. SunShot has set an aggressive cost target of 3 ¢/kWh by 2030 for utility-scale PV. Reaching this cost target would enable a tremendous future for PV, where photovoltaics could provide 15–20% of US electricity in 2030 and 30–60% in 2050. Area 12 also featured excellent regional updates from speakers from Japan, South Korea, Europe and the US. Strong growth is ex-

pected in most markets, with South Korea's government actively supporting PV, with an aim for 35 GW of installed capacity by 2030. Finally, in an invited talk by Vasilis Fthenakis (Columbia University), opportunities for clean water desalination and the role of photovoltaics were discussed. Reverse osmosis (RO) plants provide 75% of new desalination capacity, which requires constant power input. Vasilis discussed solutions in which PV, despite the intermittent nature, can provide a clean power source for RO.

In addition, several special international sessions took place on such topics as Smart Mobility, Grid Integration and TPV. There were many other activities such as 10 tutorials on key PV topics, an exhibit, several receptions, a high school program, a Young Professionals networking event, a PV jobs fair, a Women in PV Luncheon, a wonderful conference banquet in the National Air and Space Museum, a lovely social program, an "Open Mike Night" and the traditional early morning scheduled Sun Run. Next year the PVSC will be held at the Hilton Waikoloa Village in Hawaii in the form of a world conference, named WCPEC-7. The dates of this forthcoming event will be June 10-15, 2018.

The authors greatly acknowledge Jeremiah McNatt (NASA, USA), the full Program Committee and in particular PVSC-44's presenters for their contributions to the daily highlights and the realization of the technical program of the PVSC-44 conference. It was a great meeting for which we like to thank all involved!

This article was prepared by Dr. Stephen Bremner, the PVSC-44 Daily Highlights Coordinator, Dr. Seth Hubbard, the PVSC-44 Technical Program Chair, and Dr. Angèle Reinders, the PVSC-44 Conference Chair.

## UPCOMING TECHNICAL MEETINGS

## 2017 IEEE INTERNATIONAL ELECTRON DEVICES MEETING

Advances in semiconductor and related devices are driving significant progress in our increasingly digital world, and the place to learn about cutting-edge research in the field is the annual IEEE International Electron Devices Meeting (IEDM), to be held December 2-6, 2017 at the Hilton San Francisco Union Square hotel. Highlights for 2017 include:

- A talk on transformative electronics by Dr. Hiroshi Amano, who received the 2014 Nobel Prize in Physics along with Isamu Akasaki and Shuji Nakamura for the invention of efficient blue LEDs, which sparked a revolution in innovative, energy-saving lighting.

- The above talk is part of an exceptional slate of plenary talks to be given by some of the industry's leading figures, as listed below.

- Focus Sessions will be held on the following topics: 3D Integration and Packaging, Modeling Challenges for Neuromorphic Computing, Nanosensors for Disease Diagnostics, and Silicon Photonics: Current status and perspectives.

- A vendor exhibition will be held again, based on the success of last year's first-ever such event at the IEDM.

- The IEEE Magnetics Society will host a poster session on MRAM (magnetic RAM memories).

Each year at the IEDM, the world's best technologists in micro/nano/ bioelectronics converge to participate in a technical program consisting of more than 220 presentations along with special luncheon talks and a variety of panels, special sessions, tutorials, Short Courses, IEEE/EDS award presentations and other events that highlight leading work in more

diverse areas of the field than any other conference. Some of the events that will take place at this year's IEDM are:

#### Focus Sessions on:

- 3D Integration and Packaging

- **Modeling Challenges for Neuro**morphic Computing

- **Nanosensors for Disease Diagnostics**

- **Silicon Photonics: Current Status** and Perspectives

## 90-Minute Tutorials - Saturday, Dec. 2

A program of 90-minute tutorial sessions on emerging technologies will be presented by experts in the fields, bridging the gap between textbooklevel knowledge and leading-edge current research. Advance registration is recommended.

- The Evolution of Logic Transistors Toward Low Power and High Performance IoT Applications, Dr. Dae Won Ha, Samsung Electronics

- Negative Capacitance Transistors, Prof. Sayeef Salahuddin, **UC** Berkeley

- Fundamental, Thermal, and Energy Limits of PCM and ReRAM, Prof. Eric Pop, Stanford University

- Hardware Opportunities in Cognitive Computing: Nearand Far-Term, Dr. Geoffrey Burr, Principal Research Staff Member, IBM Research-Almaden

- 2.5D Interposers and High-Density Fanout Packaging as Enablers for Future Systems Integration, Dr. Sundaram Venkatesh, Associate Director, Georgia Tech 3D Systems Packaging Research Center

- Silicon Photonics for Next-Generation Optical Interconnects, Dr. Joris Van Campenhout, Program Director Optical I/O, IMEC

## Short Courses - Sunday, Dec. 3

Short Courses provide the opportunity to learn about important areas and developments, and provide the opportunity to network with experts from around the world. Advance registration is recommended.

- Performance Boosters and Variation Management in Sub-5 nm CMOS, organized by Sandy Liao, Intel

- Merged Memory-Logic Technologies and Their Applications, organized by Kevin Zhang, TSMC

## Plenary Presentations – Monday, Dec. 4

- System Scaling Innovation for Intelligent Ubiquitous Computing, Jack Sun, VP of R&D,TSMC

- Driving the Future of High-Performance Computing, Lisa Su, President & CEO, AMD

Energy-Efficient Computing and Sensing: From Silicon to the Cloud, Adrian Ionescu, Professor, EPFL

## Plenary Presentation – Wednesday, Dec. 6

Development of a Sustainable Smart Society by Transformative Electronics, Hiroshi Amano, Professor, Nagoya University

## **Evening Panel Session – Tuesday evening, Dec. 5**

The IEDM offers attendees an evening session where panels of experts give their views on important industry topics. Audience participation is encouraged to foster an open and vigorous exchange of ideas.

Who Will Lead the Industry in the Future? Moderator: Prof. Philip Wong, Stanford University

### **Entrepreneurs Lunch**

This popular luncheon, jointly sponsored by IEDM and IEEE EDS Women in Engineering, will be held once again. This year's speaker is Courtney Gras, Executive Director for Launch League. Event details can be found at, http://ieee-iedm.org/program/entrepreneurs-luncheon/.

Early registration is suggested, as tickets sell out fast for this crowd-pleasing event. Don't forget to sign-up for the luncheon when you register for the IEDM.

### **Further information about IEDM**

For registration and other information, visit www.ieee-iedm.org.

Gary Dagastine Dagastine & Co. PR

Chris Burke BtB Marketing Communications

## 2017 IEEE SEMICONDUCTOR INTERFACE SPECIALISTS CONFERENCE (SISC)

The 48th IEEE Semiconductor Interface Specialists Conference (SISC) will be held at the Bahia Resort Hotel in San Diego, California, on **December 6–9, 2017**, immediately after the IEEE International Electron Devices Meeting (IEDM) in San Francisco. An evening Tutorial session, free to all registered SISC attendees, will be held on December 6th.

The SISC is a workshop-style conference that provides a unique forum for device engineers, materials scientists, and solid-state physicists, to openly discuss issues of common interest. Principal topics are semiconductor/insulator interfaces, the physics of insulating thin films, and the interaction among materials science, device physics, and state-of-the-art technology. Emphasis is placed on

current and future nano-scale device architectures, and how interfaces between dissimilar materials and ultra-thin films affect device operation where theory, modeling/simulation, and characterization results are used to help understand the impact on device performance and reliability. The conference is held in San Diego, and meets back to back with the IEDM to encourage participation of IEDM attendees. SISC is sponsored by the IEEE Electron Devices Society.

An important goal of the conference is to provide an environment that encourages interplay between scientific and technological challenges. Oral sessions of invited and contributed talks, as well as a lively poster session, are designed to encourage discussion.

Conference participants have numerous opportunities for social gatherings with renowned scientists and engineers. They also enjoy San Diego attractions including Mission Beach, Coronado Island, Sea World, La Jolla, and Old Town San Diego.

The program includes talks and poster presentations (theory and experiment) from all areas of semiconductor interface science and technology, including but not limited to:

- SiO<sub>2</sub> and high-k gate dielectrics on Si and their interfaces

- Insulators on high-mobility and alternative substrates (SiGe, Ge, III-V and III-N, SiC, etc.)

- MOS gate stacks with metal gate electrodes

- Stacked dielectric layers for non-volatile memory

- Oxide and interface structure, chemistry, defects, and passivation: theory and experiment

- Electrical characterization, performance and reliability of MOS-based devices

- Surface cleaning technology and impact on dielectrics and interfaces

- Dielectrics on nanowires/-tubes and graphene

- Oxide electronics and multiferroics

- Interfaces in photovoltaics, e.g. Si passivation

- 2D materials and devices and their interfaces

- Interfaces in semiconductor lighting and optical communications

- Interfaces and surfaces in biotechnology such as bio-sensing

#### **Confirmed invited speakers are:**

- Prof. Joerg Appenzeller, Purdue U. 2D Tunneling FET

- Prof. Suman Datta, Notre Dame U. Novel selectors and Phase FETs

- Dr. David Ginley, NREL Photovoltaic materials, Devices and interfaces by design

- Dr. David Hemker, LAM Research Enabling Continued Device Scaling: An Equipment Supplier's Perspective

- Prof. Cheol Seong Hwang, SNU, Korea

Ferroelectric HfO<sub>2</sub> – Materials fundamentals, switching, wake-up, and applications in electronics and energy

- Prof. Evan Reed, Stanford U. Leveraging machine learning to screen 2D van der Waals materials

- Prof. Mark Reed, Yale U. Field effect transistor biosensors

- Dr. Nirmal Ramaswamy, Micron Technology

Emerging memories: High density integration challenges

The Wednesday evening Tutorial, which is free to all registered SISC attendees, will be given by Prof. Lars Samuelson, Lund University, Sweden on Semiconductor nanowires and their interface properties enabling photovoltaics and lighting applications.

A unique feature of SISC is the attention paid to the poster presentations. Each author of a poster presentation has the opportunity to introduce their work orally, using two visuals, to the entire SISC audience during special poster introduction sessions. The posters are then presented during a separate poster reception on Thursday evening. A rump session organized for Friday afternoon is dedicated to a topic of current interest.

SISC is a popular conference with students, who can get immediate and candid feedback on their latest results from the experts in the field. In addition to a reduced registration fee for students, a Best Student Presentation award is given every year in memory of E.H. Nicollian, a pioneer

in the exploration of the metal-oxidesemiconductor system who had a strong presence within the SISC.

The scientific content of the conference is complemented by informal events designed to encourage lively discussion and debate. A hospitality suite with complimentary drinks is available to attendees to continue their discussions on every evening of the conference. On Friday evening the conference hosts a banquet and awards ceremony, complete with the nowfamous (and always riotous) limerick contest. The limericks never fail to give the conference presentations, people and events an entirely new perspective.

SISC is always a rewarding experience for specialists, students, as well as newcomers to the field. For more information about the conference, to consult its program and to register, please visit http://www.ieeesisc.org. We look forward to seeing you at SISC 2017!

Chris Hinkle 2017 SISC General Chair University of Texas at Dallas, USA

> Matthias Passlack 2017 SISC Program Chair TSMC Europe, Belgium

Paul McIntyre 2017 SISC Arrangements Chair Stanford University, USA

## 2018 IEEE INTERNATIONAL MEMORY WORKSHOP (IMW)

The 10th International Memory Workshop (IMW) will be held at the Westin Miyako Hotel in Kyoto, Japan from May 13-16, 2018. The history of the IMW dates back to the NVSMW (Nonvolatile Semiconductor Memory Workshop) which began in 1976 and which later merged with the IC-MTD (International Conference on Memory Technology and Design) to become the IMW. The IMW is sponsored by the IEEE Electron Devices Society and meets annually in May. The workshop covers all types of memory technology, is focused on advancing innovation in memory technology, and is organized in a way that provides excellent professional development and networking opportunities for attendees.

The IMW is the premier international forum for both new and seasoned technologists having diverse technical backgrounds to share and learn about the latest developments in memory technology with the global community. The scope of workshop content ranges from new memory concepts in early research to the technology drivers currently in volume production as well as emerging technologies in development. Topics include new device concepts, technology advancements, scaling and integration, circuit design and reliability, as well as emerging applications. Consistent with the increased importance of memory system architecture and integration, the workshop also includes increasing coverage of the systems in which memories are deployed and the co-evolution of memory technology along with memory systems and applications.

The IMW is the preeminent forum covering the latest developments, innovations, and evolving trends in the memory industry. Typical workshop attendance exceeds 250 attendees and the technical program begins with a full day short course given by distinguished experts that provides an excellent professional development opportunity for both new and experienced technologists. The single-track technical program spans three days and also includes an evening poster session for informal technical discussion with authors as well as a panel discussion where experts discuss and debate a current hot topic. The 2017 workshop included invited talks from industry and research leaders from Google, Samsung, Micron, IBM, Western Digital, Panasonic, Everspin, CEA LETI, and IMEC. Highlights included experts sharing their insights and perspectives on a variety of topics including the 3D NAND scaling horizon and potential successors, the latest breakthroughs in RRAM/ MRAM/FRAM technology, low latency persistent memory architecture, the prospects of emerging NVM to

accelerate deep learning, and the transformative impact that machine intelligence in consumer products is having on memory architecture. The technical program is organized to maximize networking opportunities and facilitate open information exchange among workshop contributors, committee members, and attendees. The program schedule includes ample time dedicated to social events including provided refreshment breaks, a workshop luncheon, and an evening banquet. This year's workshop is located near downtown Kyoto, with opportunities to explore the local temples, shrines, palaces, gardens, and museums that are part of the area's rich cultural heritage.

On behalf of the organizing committee, I cordially invite you to participate in the 2018 IMW to continue to participate in the advancement of innovation in the rapidly evolving memory industry. For additional information, including the call for papers, key dates, abstract submission instructions, registration information, and technical program details, please visit the IMW website for the latest updates: http://www.ewh.ieee.org/soc/eds/imw/. I look forward to seeing you in Kyoto this May.

Randy Koval 2018 IMW Publicity Chair Intel

## SOCIETY NEWS

## Message from EDS President-ELECT

Dear Readers and EDS Members,

Fernando Guarin EDS President-Elect

It is once again a true honor and privilege to write to you as the EDS President Elect 2016-2017. I will take this opportunity to outline some of the plans and vision for the engagement

young professionals and our involvement in humanitarian activities.

In order to remain a viable and vibrant society, EDS needs to reach out to its youngest and newest members. We must make every effort to reach out and include them with the clear realization that they represent the future of our society. It is imperative that we enhance our presence and become active in the channels that are part of their daily life. Consequently, is important for EDS to establish a strong and active presence in social media (Facebook, LinkedIn, Instagram...), not a replacement for our strong and well known communication channels, but a complementary way to engage more of our members, and reach a

larger and global audience. Who better to spearhead this effort, than by engaging and leveraging our members and volunteers that are part of our Young Professionals. In my opinion one of the best tools for recruiting young members will be by enhancing and creating programs that enable our members to use their knowledge to become active participants in volunteer activities that will benefit society. We must provide a path to execute our society's mission of promoting excellence in the field of electron devices for the benefit of humanity. Any EDS members interested in devoting their time and talents to an IEEE humanitarian project will find that there are many opportunities that can be found at http://eds.ieee.org/ humanitarian-programs.html

Educating and motivating young minds to engage in science and technology are one of our core programs. Since 2011 our society has taken a leadership role in outreach efforts to engage young minds starting at the elementary and High School levels through the EDS-ETC program (Engineers Demonstrating Science: an Engineer Teacher Connection). Any

of our chapters wishing to visit local schools and engage their community can request kits in our EDS webpage http://eds.ieee.org/the-edsetc-program.html. Through this initiative, we have reached over 30,000 students in all regions of the world.

The Electron Devices Society (EDS) is proud to announce that we partnered with the IEEE Foundation to establish the IEEE Electron Devices Mission Fund of the IEEE Foundation. This will be one more tool that will be available to our volunteers, by having our own mission fund currently funded with \$100,000 and ready to be used to fund valuable initiatives, to enhance the humanitarian activity efforts of our members.

I look forward to your feedback on your ideas about how we can improve our society and enhance the value added that a membership to EDS will bring for you and provide the tools to make lasting contributions to society.

> Fernando Guarin EDS President-Elect GlobalFoundries New York, USA

## Message from the Editor-In-Chief

Dear EDS Members and Readers,

Carmen M. Lilley Editor-in-Chief EDS Newsletter

Welcome to the October newsletter! It is a pleasure to share with you the wide array of information and articles from our chapters and members around the globe that we

received for this newsletter. In particular, I was inspired by the articles demonstrating the enthusiasm of our members to share their knowledge and inspire the next generation of ED engineers around the world. These education outreach programs, conferences, and workshops show how EDS is improving access to education in communities around the world. I hope you are as inspired by these articles as

I was. As always, I invite our EDS members and readers to share with me their ideas on themes they would like to appear in the newsletter and feedback on changes you see in the newsletter.

> Sincerely, Carmen M. Lilley University of Illinois at Chicago Editor-in Chief, EDS Newsletter e-mail: clilley@uic.edu

## Message from EDS VICE PRESIDENT OF PUBLICATIONS AND PRODUCTS

Dear Fellow EDS Members:

Hisayo S. Momose EDS Vice President of Publications and

I am very pleased to have this opportunity to update you on the latest progress and the topics in our EDS publications.

Our flagship publications, the IEEE Transactions on Electron Devices

(T-ED), the IEEE Electron Devices Letters (EDL), and the IEEE Journal of the Electron Devices Society (J-EDS), have continued to do well over the last few years under the excellent leadership of corresponding Editor-in-Chiefs (EiCs); Giovanni Ghione for T-ED, Tsu-Jae King Liu for EDL and Mickael Ostling for J-EDS. Submitted papers are steadily increasing both in T-ED and EDL. In the case of J-EDS, they have been increasing significantly since it launched in 2013. For the three publications, we have more than one hundred editors in the Editorial Boards and many reviewers including more than three thousand Golden Reviewers last year (2016). Their outstanding contributions are really appreciated. In addition, we would like to express our sincere thanks to the EDS editorial staff and the members of Publication and Products Committee (PPC) for their continuing contributions and great support.

The publishing cycle time (Submission to e-Publication) has been improved year by year. Extremely short cycle times of 3.5 weeks and 12.7 weeks were achieved in the first half of this year for EDL and T-ED, respectively. EDL is now the fastest-turnaround IEEE journal, and T-ED also keeps the fastest of all IEEE Transactions. We are proud of these excellent results. In the case of J-EDS, the publishing cycle time is now around 11 weeks. We will work to further shorten the time as an open access (OA) journal.

Paper download statistics are important indicators for our publications, since they help to directly grasp accessing the information required by readers around the world. Based on the download statistics from IEEE Xplore, T-ED was ranked as the top eighth in all IEEE publications (from over 350 publications) last year, which had 870 thousand downloaded papers. EDL was top-ranked in the IEEE Letters publications with 530,000 downloaded papers. The total usage of J-EDS has been also growing significantly year by year, and the downloaded papers of last year became 1.5 times larger than those of 2015.

Bibliometric Indicators, such as Impact Factor (IF) and Article Influence (AF), are also known as important indexes for journals. The latest IF values are 2.61, 3.05 and 3.14 for T-ED, EDL and J-EDS, respectively. Delightfully, each value has improved compared with that of last year for the three journals. We will continue steady efforts to keep or improve the quality of the publications going forward in order to make them more attractive and to reach out to more audiences.

A few Special Issues per year have been published in T-ED and J-EDS. They are being planned on wide and high impact research areas including new developing and/or emerging areas. Reviewed Special Issues on "Power Semiconductor Devices and Smart Power IC Technologies" and "Flexible Electronics" were published with T-ED in March 2017 and May 2017, respectively. A special issue on "Vacuum Electronics" will be published with T-ED in 2018. Special issue volumes in J-EDS will also be published in 2017 and 2018, collaborating with target flagship conferences, including the European Solid-State Device Research Conference (ESSDERC) and the Electron Devices Technology and Manufacturing Conference (EDTM).

In EDL, an Editors' Picks program started last year. About six excellent papers per month are highlighted as "Editors' Picks," and available for free online within a limited time. Please use the benefit of this program to get cutting-edge valuable technical information.

J-EDS launched as the first OA journal of the Electron Devices Society in January 2013 in response to the demand for OA publishing. Recently, it has been recognized widely inside and outside of our society. Since the launch, both submissions and downloads have been increasing year by year, and the latest IF of 3.14 is a very good start, as described above. In February 2017, we successfully completed the first review for J-EDS by the IEEE Periodicals Review and Advisory Committee (PRAC). We obtained very positive feedback from PRAC regarding the issues of timeliness and quality. For the success of our journal at the first stage, we would like to especially thank Renuka P. Jindal (First EiC) and Mikael Ostling (Current EiC) for their outstanding leadership. In accordance with members' need, we will continue to strategically work and go forward to make J-EDS one of the top-tiered topical OA publications within competing OA publications on device technology.

Finally, we report the latest progress of our co-sponsored publications briefly. EDS co-sponsors several leading journals, including the IEEE Journal of Photovoltaics (J-PV), the IEEE Transactions on Device and Materials Reliability (T-DMR), the IEEE Transactions on Semiconductor Manufacturing (T-SM), the IEEE Journal of Lightwave Technology (J-LT), and the IEEE Journal of Microelectromechanical Systems (J-MEMS). The submissions of these five journals have been holding steady in recent years. The total usage statistics from IEEE Xplore downloads are

also steady for all the journals. J-LT had around 570,000 downloaded papers last year, and was ranked among the thirtieth in all IEEE publications. That of J-PV has been increasing recently, reflecting the readers' interests.

We hope that all researchers in the Electron Device area consider pub-

lishing devices-related articles first in our EDS publications. We would like to increase our flexibly to meet members' need and provide better service to the community. In order to improve our journals further, your feedback is really appreciated. If you have any suggestions and comments, please contact me by

email (h.s.momose@ieee.org) or Ms. Marlene James, Supervisor EDS Publications (m.james@ieee.org).

Sincerely, Hisavo S. Momose EDS Vice President of Publications and Products e-mail: h.s.momose@ieee.org

## EDS PHOTOVOLTAIC DEVICES TECHNICAL COMMITTEE REPORT

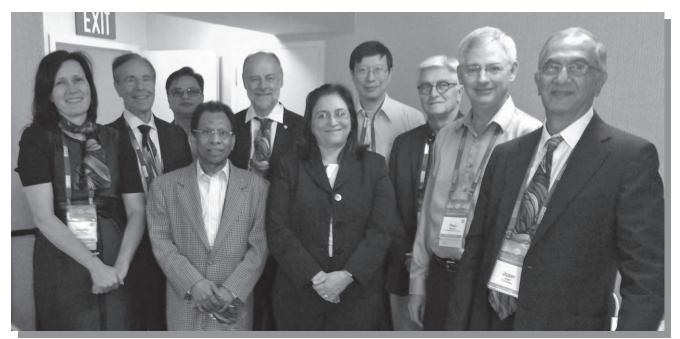

The EDS Photovoltaic Devices Technical Committee (TC) has the charter to identify new emerging areas in photovoltaic (PV) devices, and to promote activities in PV among EDS members. The TC consists of 12 members: Armin Aberle, Tim Anderson, Paul Basore, Richard Corkish, Sonia Diniz, Ned Ekins-Daukes, Larry Kazmerski, Hassan Qasem, Angele Reinders, Charles Surya, Sunit Tyagi and Juzer Vasi (Chair). The Committee had a face-toface meeting on June 28, 2017 during

the 44th IEEE Photovoltaic Specialists Conference (PVSC) in Washington DC, which was held from June 25-30, 2017. All members of the Committee except 3 were able to attend this meeting. EDS President, Samar Saha, was also present as he was attending the PVSC.

To start off the meeting, Samar Saha gave a brief overview of EDS and the mandate of Technical Committees. The Committee then discussed various issues related to photovoltaics

and what the TC could do to leverage the technical excellence of EDS to impact photovoltaics research and deployment worldwide. Some of the suggestions are:

• The TC can play an important role in disseminating technical information about PV globally, especially to industry in the manufacturing countries, where IEEE has a strong presence through its Sections and Chapters.

Attendees at the meeting of Photovoltaic Devices TC meeting at PVSC in Washington, D.C., on June 28, 2017. (L to R): Angele Reinders, Larry Kazmerski, Sunit Tyagi, Samar Saha, Richard Corkish, Sonia Diniz, Charles Surya, Tim Anderson, Paul Basore, Juzer Vasi

- The TC can encourage EDS chapters to conduct the EDS signature 'Mini-Colloquia' with a focus on new developments in photovoltaics.

- The TC can solicit a Review paper on some of the important new developments in PV devices, which could be published jointly in IEEE Transactions on Electron Devices (TED) and IEEE Journal of Photovoltaics (JPV). This would have the benefit of bringing such developments to the attention of a wider electron devices community.

It was decided that the above suggestions would be taken up by the committee and pursued further. The Committee also discussed the recommendation from Carmen M. Lilley, Editor-in-Chief of the EDS Newsletter. that a 'Technical Brief' article giving the Highlights of the PVSC conference be published in the Newsletter on an annual basis. This article would be similar to the very successful IEDM Highlights which appears annually. This suggestion was agreed to, and Angele Reinders, who is also the 2017 PVSC Conference Chair, agreed to follow up on this.

The Committee also agreed that the TC would meet every year while attending IEEE PVSC, since most members are likely to attend this conference. Accordingly, the next meeting of the Photovoltaic Devices TC is scheduled to be held in Hawaii in June 2018.

EDS members who would like to offer suggestions to the TC are most welcome to write to the Chair, Juzer Vasi, at j.vasi@ieee.org.

Juzer Vasi Chair, EDS Photovoltaic Devices Technical Committee Indian Institute of Technology Bombay

## Message from Leda Lunardi, EDS Women in Engineering Liaison

Leda Lunardi EDS WIE Liaison

I have been representing the EDS as the IEEE Women in Engineering Liaison since January 2016. One myth that exists is that WIE is only for women, when actually today WIE has more

than 20,000 members from which 1/3 identify themselves as males. This may be related to the lack of information around the formation of WIE, which started in 1993 as an ad-hoc committee to address the increase in IEEE membership that identifies themselves as females (about 8% of the total IEEE members). An interest in having an umbrella organization for women with the rapidly number of members joining WIE prompted the IEEE board to pass a resolution for letting the group start collecting membership dues and having separate representation at the board of directors without voting privileges. Some geographic regions have a larger percentage of WIE members than other areas, (Regions 1–8 have the lowest fraction of the total members that are WIE members, while Regions 9–10 have the largest participation). The majority of the WIE members are students (undergraduate and graduate) that benefit from creating a professional network and receiving different perspectives for their technical careers in engineering and science.

As the EDS liaison, I participate in monthly conference calls with all the other technical societies and councils representatives and on alternate months with the WIE executive committee.

Some of us volunteer for WIE activities including the WIE newsletter, awards committees, workshops, technical committees and outreach.

WIE has sponsored several technical leadership career development projects that began in Silicon Valley and more recently expanded internationally. These events are organized in different geographical areas in conjunction with IEEE technical con-

ferences or meetings, and co-sponsored by IEEE regions.

Last year in November 2016, I attended the WIE leadership summit sponsored by Region 3 in Atlanta, Georgia: tailored to attract Georgia Tech and regional engineering students. It was well attended by local area industry, defense contractors and professionals.

With the input of the liaisons, the WIE executive committee is starting to compile the best practices that exist around the IEEE technical societies related to the involvement of women and underrepresented minorities in committees and technical conferences.

Consider in joining IEEE WIE: the membership is free for students, graduate student members and life members, while for IEEE member dues are US\$25 annually.

Leda Lunardi EDS Women in Engineering Liaison North Carolina State University Raleigh, NC, USA

## EDS/Women in Engineering Co-sponsor ENTREPRENEUR LUNCHEON AT IEDM

Courtney Gras Invited Speaker

At the 63rd IEEE International Electron Devices Meeting, the Entrepreneur Luncheon will be held on Tuesday, December 6, 2017, at the San Francisco Hilton. This event

sponsored by IEDM and EDS/Women in Engineering with Leda Lunardi as moderator, will feature Courtney Gras, an electrical engineer who

started her entrepreneurial career while still an undergraduate student and the co-founder of the Akronbased Design Flux Technologies, a clean energy startup.

She discovered a passion for building startup communities and helping technology-focused companies meet their goals. Presently she is the Executive Director for Launch League, an Akron-based nonprofit focused on developing a strong startup ecosystem in NE Ohio with her work as a business development consultant for local technology companies.

In 2016 she was named, while serving as Chief Operations Officer, a "Forbes 30 under 30". She has also been named to the "Top 40 under 40" in Cleantech by Midwest Energy News and one of Crain's "Twenty in their 20s." More recently on August 26, 2017 she has been featured in TEDx Talks with "Why Success Will Keep You Moving."

Leda Lunardi EDS Women in Engineering Liaison

## EDS Members Recently Elected TO IEEE SENIOR MEMBER GRADE

Pierre-Jean Alet Roger Booth Rongming Chu Werner Drexel Abel Garcia Stephen Heinrich-Barna Haslina Jaafar\* Carlos Leal Saballos Matthew Marinella Marco Munguia

Ken Nishimura Taiji Noda Rebecca Peterson C. Pinzone Angele Reinders C. Selvakumar Oscar Somarriba Chan Tan Miaomiao Wang Ahmad Sabirin Zoolfakar\*

Thank you to the EDS members who remembered to designate the Electron Devices Society as their nominating entity!

Indicated with an asterisk(\*).

If you have been in professional practice for 10 years, you may be eligible for Senior Membership, the highest grade of membership for which an individual can apply. New senior members receive a wood and bronze plaque and a credit certificate for up to US \$25 for a new IEEE society membership. Upon request, a letter will be sent to employers, recognizing this new status. For more information on senior member status, visit: http://www .ieee.org/membership\_services/membership/senior/ index.html

To apply for senior member status, fill out the on-line application after signing in with your IEEE account: https:// www.ieee.org/membership\_services/membership/ senior/application/index.html.

## Awards and Call For Nominations

## 2016 EDS PAUL RAPPAPORT AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. Every year, the Society confers its prestigious Paul Rappaport Award to the best paper published in the *IEEE Transactions on Electron Devices*. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The winning paper was selected from over 740 articles that were published in 2016. The winning paper is titled "A Color-Tunable Polychromatic Organic-Light-Emitting-Diode Device with Low Resistive Intermediate Electrode for Roll-to-Roll Manufacturing." This paper, published in the January 2016 issue of the IEEE Transactions on Electron Devices, was authored by Takatoshi Tsujimura, Takeshi Hakii and Suguru Noda.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 4, 2017, in San Francisco, California. In addition to the award certificate, the authors will receive a check for USD\$2,500 to be shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Takatoshi Tsujimura was selected as "10 best engineers/researcher in 10 best Japanese companies" by Nikkei Electronics Magazine.

He received the SID Special Recognition Award and SID Fellow Award for his development of OLED TV technology, which has become an industry standard. He is currently a Konica Minolta Fellow and is a CTO of Konica Minolta Pioneer OLED.

Takeshi Hakii has been working with Konica Minolta since 1995. He is responsible for next generation technology for flexible OLED. He received a bachelor's degree in

Applied Chemistry in 1995 from Waseda University, Tokyo, Japan. He has developed many products such as OLED lighting, wearable dis-

plays and electronic papers.

Suguru Noda is a professor at the Department of Applied Chemistry, Waseda University, Japan. He has conducted research in the field of materi-

als processing, especially thin films by chemical and physical vapor deposition methods. He is recently focusing on practical production of carbon and silicon nanomaterials for energy and electronic applications.

Hisayo S. Momose EDS Vice President of Publications and Products h.s.momose@ieee.org

## 2016 EDS GEORGE E. SMITH AWARD

A high priority of the Electron Devices Society (EDS) is to recognize and enhance the quality of papers published in EDS archival literature. The George E. Smith Award was established in 2002 to recognize the best paper appearing in a fast turnaround archival publication of EDS, targeted to the *IEEE Electron Device Letters*. Among other criteria including technical excellence, an important metric for selection for the award is comprehensive and impartial referencing of prior art.

The paper winning the 2016 George E. Smith Award was selected from

over 390 articles that were published in 2016. The paper is entitled, "An Experimental Demonstration of GaN CMOS Technology." This paper appeared in the March 2016 issue of the IEEE Electron Device Letters and was authored by Rongmin Chu, Yu Cao, Mary Chen, Ray Li, and Daniel Zehnder.

The award will be presented at the plenary session of the IEEE International Electron Devices Meeting to be held on December 4, 2017, in San Francisco, California. In addition to the award certificate, the authors will receive a check for USD\$2,500 to be

shared equally among all authors. On behalf of the Electron Devices Society, I would like to congratulate the authors for this achievement. Brief biographies of the authors follow.

Rongming Chu received his PhD at UC-Santa Barbara, working on GaN microwave transistors. After finishing his degree in 2008, he spent

two years at Transphorm, Inc., then a

start-up company commercializing GaN power switching technology. He joined HRL Laboratories in 2010 as a Research Staff responsible for GaN power device technology development, and became a Senior Research Staff in 2014. His research at HRL includes GaN-on-Si lateral power transistors, GaN-on-GaN vertical power devices. and more recently GaN CMOS IC. He served on the technical program committees of the IEEE Workshop on Wide Bandgap Power Device and Applications, the IEEE Lester Eastman Conference, and the Asia-Pacific Workshop on Wide Bandgap Semiconductors.

Yu Cao received the PhD degree in Electrical Engineering at the University of Notre Dame. He is currently a research staff scientist at

HRL Laboratories, working on GaN epitaxy and devices. As a senior member of IEEE, he has authored 3 books/ chapters, over 120 peer-reviewed journal and conference papers.

Mary Chen received her B.S. in physics at Mount Holyoke College with magna cum laude in 1983. and her Ph.D. in electrical engineering from Cornell in 1988.

She has experience with compound semiconductor devices in several material systems for high speed and high power MMIC applications, and highspeed digital IC applications. She is currently with Microelectronics Laboratory of HRL Laboratories LLC.

Ray Li is an IEEE member. He received his Ph.D. in Chemical Engineering from University of California, Riverside.

He developed the processes for different generations of lateral and vertical GaN devices at HRL. He has authored and co-authored more than 30 publications and patents.

Zehnder Daniel received the electrical engineering degree from the Gewerbliche Berufsschule Biel, Switzerland, in 1992. He joined

HRL Laboratories in 2004 as a Senior R&D Specialist. His experience is on-wafer characterization of power electronic devices and high speed mixed signal circuits, and the design of Printed Circuit Boards for device verification.

Hisayo S. Momose EDS Vice President of Publications and Products h.s.momose@ieee.org

## *<b>PIEEE*

## CALL FOR NOMINATIONS

## IEEE EDS WILLIAM R. CHERRY AWARD

The IEEE Electron Devices Society invites the submission of nominations for the 2018 William R. Cherry Award. This award is named in honor of William R. Cherry, a founder of the photovoltaic community. In

the 1950's, he was instrumental in establishing solar cells as the ideal power source for space satellites and for recognizing, advocating, and nurturing the use of photovoltaic systems for terrestrial applications. The William R. Cherry award was instituted in 1980, shortly after his death. The purpose of the award is to recognize an individual engineer or scientist who devoted a part of their professional life to the advancement of the science and technology of photovoltaic energy conversion.

The award consists of a plaque, monetary award, recognition at the PVSC Opening Ceremony and a dedicated Cherry Award Talk during the Opening Ceremony. A reception is also held in honor of the Cherry Award winner during the PVSC.

LECTRON EVICES

#### Nominate:

William R. Cherry Award online nomination form: https://ieeeforms.wufoo.com/forms/eds-william-r-cherry-award-nomination-form/

#### **Submission Deadline:**

January 31, 2018

#### For more information:

http://www.ieee-pvsc.org/PVSC45/awards-cherry.php

## Young Professionals

## ORGANIZING IEEE EDS STEM WORKSHOPS FOR KIDS TO BUILD ELECTRONIC CIRCUITS

PREPARED BY SANG LAM AND MANSUN CHAN

DEPARTMENT OF ELECTRONIC & COMPUTER ENGINEERING,

HONG KONG UNIVERSITY OF SCIENCE & TECHNOLOGY (HKUST)

#### Introduction

Advancements of electron devices have revolutionized our modern world [1], both in terms of our lifestyle and industrial manufacturing activities. While electronic technologies are indispensable in our everyday life, young students and children do not have many chances to acquire the skill of circuit construction until a very late stage of their education. With the belief that electronic projects can be introduced at a much earlier stage in our education system, EDS and the ED/SSC Hong Kong ED/SSC Chapter have initiated a number of workshops and exploration camps to let students as young as 10 years old explore electronic circuits by building interesting electronics [2] such as a running light indicator, an electronic piano, an infrared detector, etc. In this article, we share our experience and knowledge in organizing such educational activities with the IEEE EDS community, and especially for those interested in organizing similar activities in their local communities.

### **Motivation**

Hosting electronic circuit exploration workshops can achieve multiple goals. The hands-on reverse engineering approach is expected to arouse students' interest in electronics without in-depth understanding that usually takes much longer time to acquire. Once the students develop their interest, they will pursue the required knowledge without much guidance in this information-rich generation [3]. In organizing such workshops, university students are recruited as helpers.

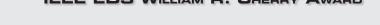

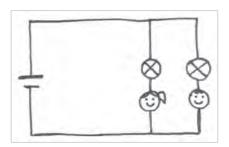

Fig. 1. Basic tools required for electronic circuit construction: (a) a breadboard, (b) a wire stripper and (c) a digital multimeter

Through serving as student helpers to explain the process of circuit construction to schoolchildren, they can practice their organization skills and develop their abilities in communicating technical ideas to a non-technical audience. By organizing these events, the organizers as well as the event sponsors can have increased visibility among schools and even the general public. The workshop can also reach out to parents to do projects together with their kids outside the workshops. Parents spending time with their children on doing something together with fun is always desirable.

## Resources

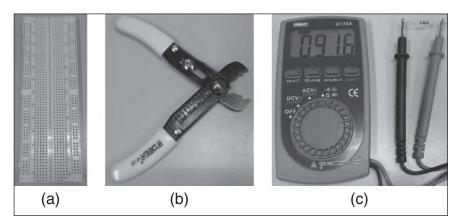

The electronic circuit construction requires only very basic tools (such as a breadboard, a wire stripper and a multimeter) (Fig. 1) and components (e.g. resistors, capacitors, LEDs, chipsets etc.) (Fig. 2) which are all readily available at affordable prices. As a result, the circuit construction workshop can

be delivered anywhere with a desk at school or at home [3]–[5]. In addition, ordinary batteries are used and the voltage is low enough not to hurt a person, though some sensitive electronic devices may be damaged by circuit mistakes. No soldering iron is needed as the electronic circuits are built on a prototyping breadboard (Fig. 1a).

### **General Practices**

In delivering such electronic circuit construction workshops, only essential physical concepts are taught. Whenever possible, understandable analogies using daily life examples are used to explain concepts. The theory discussion of electronics is kept minimal when delivering the workshops. Neither prior knowledge or skills of electronics are assumed for the workshop. As for the mathematics requirement, simple arithmetic (addition, subtraction, multiplication, division) is sufficient for building the electronic circuits in the workshop.

Fig. 2. Inexpensive components readily available for electronic circuit construction: (a) resistors, (b) capacitors, (c) LEDs, (d) chipsets, (e) wires, (f) batteries inside a battery box and (g) variable resistors

## Delivering the Workshop -**General Skills**

The workshop can start with a demonstration of how to use a wire stripper (Fig. 1b) as the basic tool. Since the hands-on approach is the essence of the workshop, participants should be given the first task of cutting and stripping wires in plastic coatings (Fig. 2e). It is then natural to explain about electrical wires. A daily life analogy of water pipes can be used. When explaining about electrical wires, the two important quantities in electronic engineering, namely current and voltage, should be introduced. The corresponding units of current and voltage need to be included as well. With the concept of voltage introduced, a battery (Fig. 2f) can be depicted as a voltage source or generator. Based on the concepts of voltage and current, the concept of resistance can then be explained. The daily life example of wa-

ter flow can be used to illustrate the idea of resistance. After explaining about resistance, it is natural to proceed to the introduction of resistors together with the color code of discrete component resistors (Fig. 2a). The second hands-on task would be reading the color code of a few resistors to figure out the resistance. Afterwards, the use of a multimeter (Fig. 1c) for measurements of current, voltage and resistance can be taught. With basic demonstrations, students should be able to learn easi-Iv how to use the multimeter (Fig. 1c). The third hands-on task would be the measurements of the resistors and checking the resistance against the values read from the color code.

The next key apparatus to introduce is the breadboard, shown in Fig. 1a, for use as a handy circuit board for quick prototyping of electronic circuits. The properties of the breadboard should be carefully

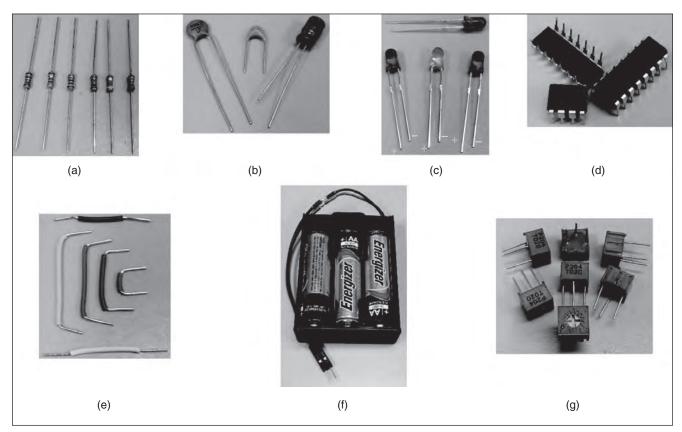

explained, especially the electrical connections of the pin holes along different rows and columns. As the fourth hands-on task, a multimeter (Fig. 1c) can be used to verify the electrical connections along a row and a column and the electrical isolation between different rows. Without explaining the theory of operation, a light-emitting diode (LED) (Fig. 2c) can be introduced as a light indicator which works only when current flows in one direction but not the other. Students should be taught how to identify the two different electrodes of an LED (Fig. 2c). With the positive and negative electrodes of the LED explained, the use of a battery box (Fig. 2d), which has positive and negative terminals as well as a switch to turn on the voltage, can then be described. This leads to the fifth hands-on task in using a battery box, an LED and a resistor to construct a simple circuit of

| Table 1. List of components, electronic engineering concepts, tools and hands-on tasks for an introductory session on electronic circuit exploration |                                                               |               |                                                                             |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|---------------|-----------------------------------------------------------------------------|--|--|

| Component                                                                                                                                            | Engineering Concept                                           | Tool          | Hands-on Task                                                               |  |  |

| Electrical wires                                                                                                                                     | Current & voltage and the corresponding units (ampere & volt) | Wire stripper | Cutting & stripping wires                                                   |  |  |

| Resistors                                                                                                                                            | Resistance                                                    |               | Reading the resistance values from the color codes of resistors             |  |  |

|                                                                                                                                                      | DC measurement                                                | Multimeter    | Measurements of the resistance of resistors                                 |  |  |

| Breadboard                                                                                                                                           |                                                               | Multimeter    | Verification of the electrical connections of a breadboard                  |  |  |

| Light-emitting diode (LED)                                                                                                                           | Unidirectional current flow                                   |               |                                                                             |  |  |

| Battery box                                                                                                                                          | DC power source; distinguishing positive & negative terminals |               | Circuit construction of a simple light indicator                            |  |  |

| Variable resistor                                                                                                                                    |                                                               |               | Circuit construction of a simple light indicator with adjustable brightness |  |  |

Fig. 3. Basic LED indicator circuit for hands-on circuit construction tasks with noticeable visual effects when working (a) with fixed brightness; (b) with a variable resistor for adjusting the resistance and hence the brightness